Ik kom al een aantal jaren samen met AMIQ EDA mede-oprichter Cristian Amitroaie om de paar maanden de toestand van de industrie te bespreken, de belangrijkste trends op het gebied van ontwerp en verificatie, en de manieren waarop deze de chipontwikkeling helpen vergemakkelijken en versnellen. Ik heb een interessante nieuwe functie opgemerkt die in hun nieuwste versie wordt genoemd persbericht, dus vroeg ik Cristian om meer informatie. Dit leidde tot een levendige en interessante discussie.

De meeste ontwerpers en verificatie-ingenieurs schrijven tegenwoordig hun code in SystemVerilog, maar er zijn uitzonderingen. Sommigen maken gebruik van tools voor synthese op hoog niveau (HLS) om te ontwerpen in SystemC of andere talen die iets abstracter zijn dan SystemVerilog. Anderen schrijven in hun eigen taal en gebruiken aangepaste tools om de SystemVerilog-bestanden te genereren die worden gebruikt voor simulatie, formele verificatie, synthese en andere stappen in het ontwikkelingsproces.

Cristian zei dat ze af en toe een middenweg zien waarin ingenieurs code schrijven die voornamelijk SystemVerilog is, maar ook 'preprocessor'-instructies bevat in gevestigde talen zoals de Jinja2-bibliotheek van Perl en Python, of in eigen talen. Ze gebruiken scripts om deze bestanden te verwerken en genereren de pure SystemVerilog-bestanden voor de rest van de stroom. Ik vroeg Cristian hoe het gebruik van preprocessors de manier verandert waarop ingenieurs een geïntegreerde ontwikkelomgeving (IDE) gebruiken.

Ik heb geleerd dat gebruikers van de AMIQ EDA Design and Verification Tools (DVT) De IDE-familie wil toegang hebben tot al hun favoriete functies, zelfs bij het bewerken van bestanden met preprocessorcode. Het AMIQ EDA-team heeft slimme heuristieken ontwikkeld om volledige IDE-mogelijkheden mogelijk te maken bij het bewerken van dergelijke bestanden, net zoals ze doen met pure SystemVerilog. Deze functies omvatten navigatie-hyperlinks, automatisch aanvullen, on-the-fly foutdetectie, snelle oplossingen, refactoring en alle geavanceerde functionaliteit waaraan DVT IDE-gebruikers verslaafd zijn.

Dit was voor mij intrigerend. We hebben het over het “begrijpen” van bestanden in gemengde talen, niet echt iets dat een compiler gemakkelijk kan verwerken. Om er zeker van te zijn dat ik het goed begrijp en dat dit echt is, nodigde Cristian Zeljko Zurzic, de teamleider die de ontwikkeling van deze mogelijkheid coördineerde, uit om uit te leggen hoe het werkt. Hij zei dat het enige wat gebruikers hoeven te doen is DVT IDE te informeren over de mapping tussen de bestanden die preprocessor-instructies bevatten (“p-bestand”) en de gegenereerde bestanden (“g-bestand”).

Dit wordt gedaan met behulp van speciale compilerrichtlijnen die verschillende gebruiksscenario's ondersteunen. Er is bijvoorbeeld een manier om de DVT IDE-compiler te vertellen: "Ga het corresponderende p-bestand uitzoeken uit de opmerking in de g-bestandskop." Zodra dit is gebeurd, bewerken gebruikers gewoon hun p-bestanden alsof er niets speciaals aan is. On-the-fly incrementele compilatie markeert eventuele SystemVerilog-fouten terwijl ze typen, hyperlinks leiden ze door de code, automatisch aanvullen en refactoring werken prima, ze kunnen verschillende diagrammen opvragen, enz.

De secties die preprocessorcode bevatten, zijn duidelijk gemarkeerd, zodat gebruikers weten dat ze zullen worden omgezet in SystemVerilog-code. In DVT Eclipse-IDE ze kunnen zien hoe code wordt gegenereerd met behulp van de Inspect View; in DVT IDE voor VS-code ze kunnen de transformaties ‘gluren’. DVT IDE kan worden geconfigureerd om het voorverwerkingsscript automatisch uit te voeren wanneer de preprocessorcode wordt gewijzigd. Gebruikers kunnen indien gewenst eenvoudig het ap-bestand vergelijken met het overeenkomstige g-bestand.

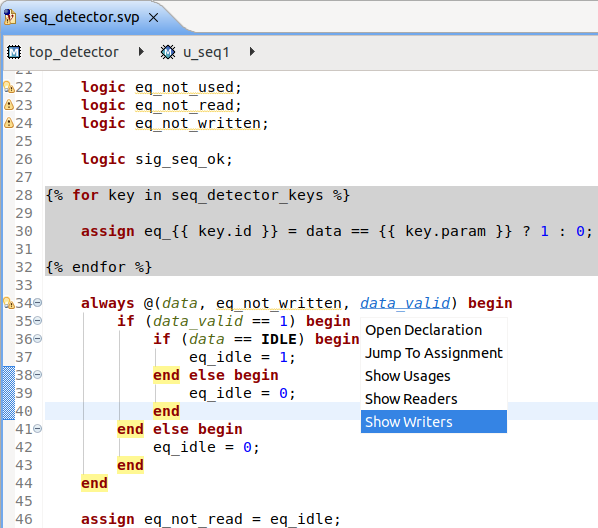

Zeljko leverde drie screenshots die deze nieuwe mogelijkheid in actie laten zien. De eerste hieronder toont een bestand in DVT Eclipse IDE dat een Jinja2 preprocessor-instructie bevat. Ondanks de aanwezigheid van deze niet-SystemVerilog-code kan de gebruiker profiteren van de krachtige functie “Show Writers” om snel te begrijpen hoe een variabele wordt aangestuurd. Compilatiefouten en waarschuwingen worden weergegeven in de meest linkse kolom van het scherm.

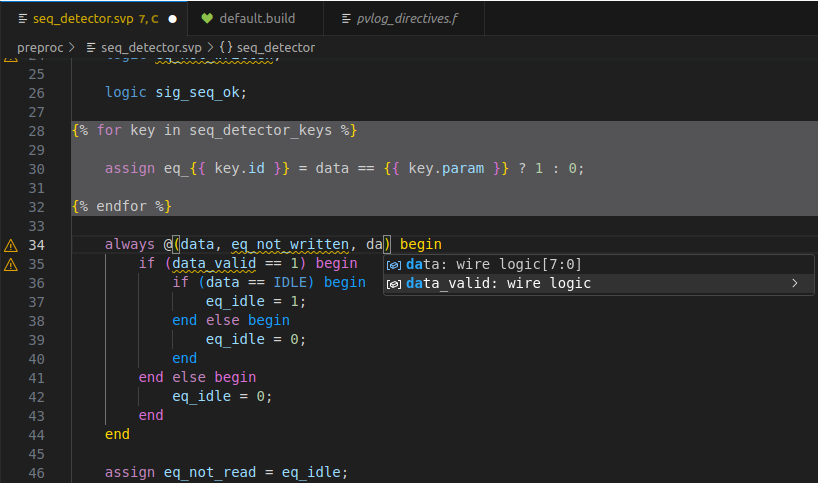

De onderstaande schermafbeelding toont hetzelfde bestand in DVT IDE voor VS Code, toont de compilerproblemen in de linkerkolom en maakt het gebruik van automatisch aanvullen mogelijk. Dit laat zien hoe zelfs de meest geavanceerde DVT-functies beschikbaar zijn in code met preprocessor-instructies.

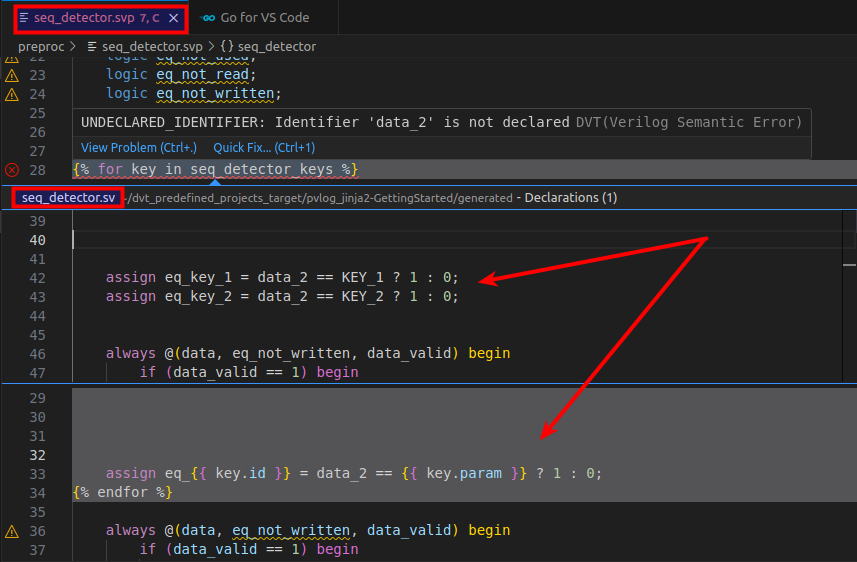

Zeljko benadrukte dat de IDE de gegenereerde SystemVerilog-code controleert, belangrijk omdat er een fout in een preprocessor-instructie of een bug in het preprocessing-script kan zitten. De onderstaande schermafbeelding toont zo'n voorbeeld. De gegenereerde SystemVerilog-code bevat een variabele die niet in het bronbestand is gedefinieerd. DVT IDE geeft de compilatiefout, het p-bestand en de gegenereerde code in het g-bestand weer.

Het bekijken van de g-bestanden kan nuttig zijn bij het debuggen, maar het komt erop neer dat gebruikers rechtstreeks met de p-bestanden werken en deze analyseren en bewerken met behulp van een krachtige IDE. De g-bestanden zijn getagd als “alleen-lezen” en gebruikers worden gewaarschuwd als ze worden gewijzigd. Ik was blij dit te horen; we weten allemaal dat het een heel slecht idee is om handmatige wijzigingen aan te brengen in elk bestand dat wordt overschreven door een codegeneratieproces.

Ten slotte benadrukte Cristian dat het hele punt van deze nieuwe functie is dat gebruikers code kunnen bewerken met preprocessor-instructies, net alsof het pure SystemVerilog is. Dit mogelijk maken is een aanzienlijke inspanning geweest van een aantal belangrijke klanten die vertrouwen op preprocessor-gebaseerde stromen. Ik bedankte Zeljko en Cristian voor hun uitleg en hun tijd.

Als u meer wilt weten over het gebruik van preprocessorbestanden of enig aspect van de AMIQ EDA-oplossingen, kunt u deze bezoeken in stand 107 op de Design and Verification Conference and Exhibition (DVCon) Verenigde Staten in San Jose, Californië op 5 en 6 maart.

Lees ook:

Vooruitzichten voor 2024 met Cristian Amitroaie, oprichter en CEO van AMIQ EDA

Linting gebruiken om foutloze Testbench-code te schrijven

AMIQ: Viert 20 jaar advies- en EDA-activiteiten

Deel dit bericht via:

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- PlatoData.Network Verticale generatieve AI. Versterk jezelf. Toegang hier.

- PlatoAiStream. Web3-intelligentie. Kennis versterkt. Toegang hier.

- PlatoESG. carbon, CleanTech, Energie, Milieu, Zonne, Afvalbeheer. Toegang hier.

- Plato Gezondheid. Intelligentie op het gebied van biotech en klinische proeven. Toegang hier.

- Bron: https://semiwiki.com/eda/amiq-eda/342053-handling-preprocessed-files-in-a-hardware-ide/