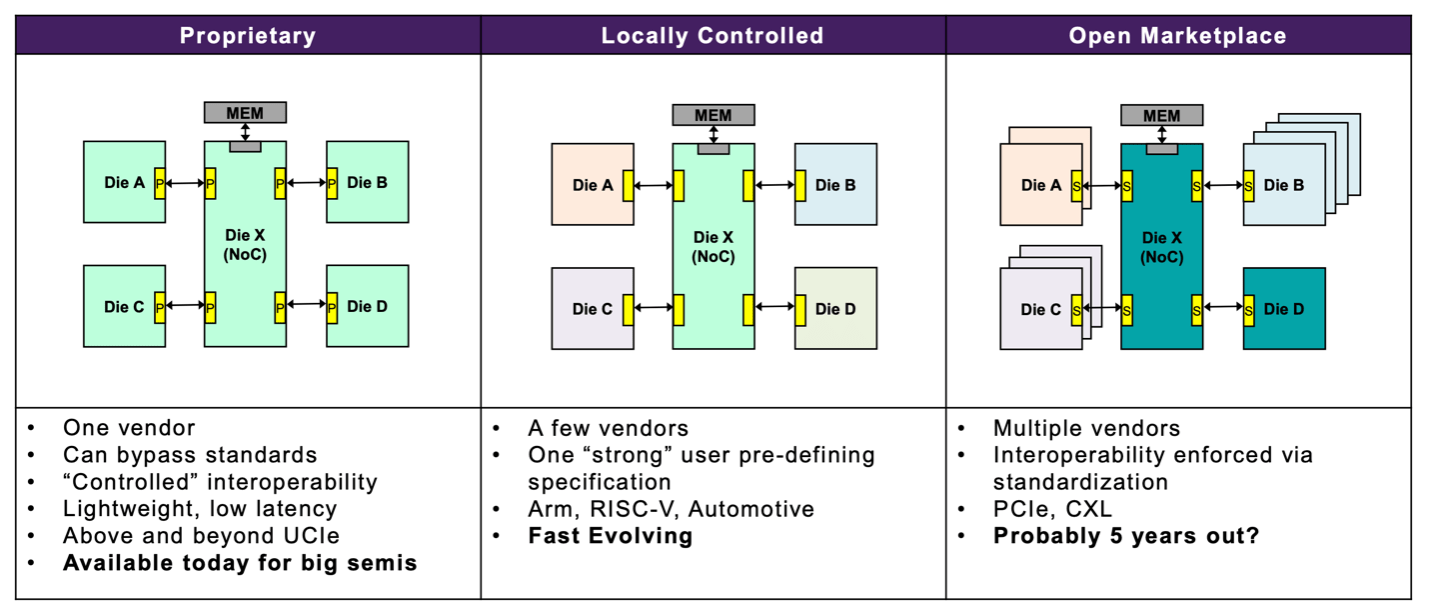

Ik sprak onlangs met Frank Schirrmeister (Solutions & Business Development, Arteris) over de stand van zaken op weg naar het open chiplet-ideaal. Weet je – waar een multi-die-systeem in een pakket kan worden samengesteld met UCIe- (of andere) verbindingen die gegevensstromen tussen dies naadloos met elkaar verbinden. Als kunstmatige algemene intelligentie en quantum computing op industriële schaal voor de deur staan, zouden de resterende problemen in het ontwerp van open chiplets toch in een handomdraai moeten worden opgelost? Volgens Frank is het antwoord ja en nee. Voor een aantal bevoorrechte groepen is alles mogelijk en wordt vandaag de dag in de praktijk gebracht. Voor grotere open markten niet zozeer, althans niet op de korte termijn.

Met dank aan slagader

Multi-matrijssystemen en eigen oplossingen

Multi-die-systemen komen tegemoet aan de nooit eindigende vraag om grotere en complexere systemen te bouwen (voor LLM-verwerking als voorbeeld) wanneer ze worden beperkt door een aantal halfgeleiderbeperkingen: je kunt maar een beperkte hoeveelheid logica op één chip passen; sommige functies zoals analoog en DRAM werken het beste in processen die niet optimaal zijn voor logica; en zelfs als je op de een of andere manier meer in één dobbelsteen zou kunnen stoppen, zou de opbrengst dalen en de kosten enorm stijgen.

Het afgelopen jaar hebben Intel, AMD en Nvidia allemaal processorproducten uitgebracht op basis van chiplet-architecturen. Wat in deze context uniek is aan deze producten, is dat deze bedrijven elk al hun eigen chiplets hebben gebouwd, samen met de infrastructuur en connectiviteit die ze samenvoegt tot een volledig multi-die-systeem. Ze zijn niet afhankelijk van externe chipletproviders of externe IP-providers voor chiplet-naar-chipletcommunicatie. Door alles intern te controleren en hun leveranciers dienovereenkomstig te begeleiden, kunnen ze de systemen die ze intern hebben gebouwd afstemmen en valideren aan de hand van hun eigen uitgebreide reeks tests. Sommige andere zeer grote verticaal geïntegreerde bedrijven kunnen ook in deze klasse vallen. Er is mij verteld dat Meta nu misschien een van deze is, en het zou me verbazen als Apple niet ook al hun eigen multi-die-ontwerp zou hanteren.

Voor iedereen die een multi-die-systeem wil bouwen: dit is allemaal interessant, maar komt nog steeds neer op een proof of concept. Werkt heel goed voor Intel, AMD en Nvidia, maar er is meer nodig voor systeembouwers die dat niveau van controle niet hebben. Hoewel de UCIe (naast andere opties) in principe voor de communicatie tussen mensen zou moeten zorgen, suggereert de realiteit dat de uitdaging nog niet is overwonnen.

Er is overigens ook een parallelle trend; Printed Circuit Boards (PCB’s) worden steeds kleiner. Hier heeft de industrie veel verschillende soorten verpakkingsbenaderingen gezien, en gebruikers zijn gewend om meerdere matrijzen op substraten te integreren voor ontwerpen die de hierboven genoemde limiet van het dradenkruis niet uitdagen. Beide trends komen samen op het gebied van chiplets, zij het met verschillende benaderingen van de ontwerpmethodologie: geminiaturiseerde PCB's versus gezamenlijk ontworpen of interoperabele kale stukjes silicium.

Open chiplets en interoperabele communicatie-interfaces

In theorie zou het gebruik van standaarden zoals UCIe voor communicatie tussen de computers de communicatieproblemen tussen de computers moeten oplossen, wat essentieel is om een echt open chiplet-ecosysteem mogelijk te maken. Als dit werkt zoals geadverteerd, zouden chiplets moeten kunnen communiceren, zelfs als ze van verschillende chipletleveranciers komen, in verschillende gieterijen zijn gebouwd, enz. Helaas blijkt naleving van de norm een noodzakelijke maar onvoldoende voorwaarde om interoperabiliteit tussen twee partijen te garanderen. (zeg maar) een UCIe-link. Hoewel de PHY's kunnen worden gecontroleerd via oogdiagrammen, is er nog steeds variatie in de manieren om gegevens te verpakken van protocollen als AXI en CHI naar streaminginterfaces zoals CXS en van daaruit naar FDI, de streaminginterface van UCIe.

Dit is geen openbaring. In de pc-wereld, bekabelde en draadloze communicatie en andere domeinen is het naleven van standaarden stap 1. Plugfests om real-world interoperabiliteit tussen leveranciers te bewijzen is een volgende stap. Voor mobiele communicatie vereisen netwerkexploitanten gedetailleerde interoperabiliteitstests op basis van hun vereisten. Het lijkt erop dat er een vergelijkbare infrastructuur nodig is voor chipletcommunicatie, hoewel dat misschien een beetje lastiger kan zijn omdat je geen connector op een chiplet kunt aansluiten. Frank vertelt me dat hij hoort dat er plannen in de maak zijn, maar dat deze naar verwachting niet snel mainstream zullen worden (het heeft ook een tijdje geduurd voor PCIe). De industrie heeft vroege gevallen aangekondigd van alleen UCIe-interoperabiliteit, tussen Intel en Synopsys bijvoorbeeld.

Eén klasse van systeembouwers heeft een eenvoudig antwoord op dit probleem. Ze zijn krachtig genoeg om hun leveranciers te dwingen hun ontwerp te conformeren. Als iets in hun gebruikssituaties niet werkt, graven de potentieel schuldige partijen zich in en moeten met een oplossing komen. Sommige grote auto-OEM's vallen in deze klasse, evenals enkele grote HPC-bedrijven. De problemen die hier worden aangetroffen, zijn waarschijnlijk kleine verschillen in verwachtingen ten aanzien van marges, buffering en andere parameters die niet volledig in de standaard zijn vastgelegd. Of gewoon bugs die niet worden behandeld in de use-case-testen van chiplet/IP-leveranciers. Wat het probleem ook is, de leveranciers moeten het oplossen. Het is goed om koning te zijn als je een op chiplets gebaseerd ontwerp wilt bouwen.

Voor alle anderen

Het vandaag de dag bereiken van interoperabiliteit hangt af van waar elk van uw inter-die-verbindingen valt in de grote en voortdurend evoluerende matrix van bewezen/gedekte communicatieparen, rekening houdend met IP/PHY-bronnen, specificatieverschillen en gebruiksverschillen (coherente versus niet-coherente links) . Symmetrische paren (alles hetzelfde aan beide kanten) zouden (?) prima moeten zijn, maar asymmetrische paren zijn een gok tenzij bewezen in de productie. Volgens Frank is deze uitdaging vooral zichtbaar vanuit de NoC-wereld. Hij zegt dat klanten vragen of de Arteris GeenC werkt met een bepaald UCIe Controller IP. Redelijke vraag zou je denken.

Maar de NoC praat met een protocol-naar-stream-converter, die vervolgens met een PHY praat. Dat communiceert via een link naar een PHY op de tweede chiplet, vervolgens naar een stream-to-protocol-omzetter en vervolgens naar de NoC op die chiplet. Iedereen voldoet volledig aan de standaard, maar toch werkt de koppeling niet – tenzij bewezen is dat deze in de productie werkt. Veel strengere interoperabiliteitstests zullen dit probleem uiteindelijk oplossen, maar dat kan over vijf jaar zijn. In de tussentijd, slagader en klanten vullen cellen in de interoperabiliteitsmatrix één (of misschien een paar) tegelijk in.

Kortom, chiplets zijn echt, volledig onder controle voor de verticaal geïntegreerde systeembouwer, snel evoluerend onder autocratische klanten, en langzaam vooruit voor alle anderen. Je kunt meer lezen HIER.

Deel dit bericht via:

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- PlatoData.Network Verticale generatieve AI. Versterk jezelf. Toegang hier.

- PlatoAiStream. Web3-intelligentie. Kennis versterkt. Toegang hier.

- PlatoESG. carbon, CleanTech, Energie, Milieu, Zonne, Afvalbeheer. Toegang hier.

- Plato Gezondheid. Intelligentie op het gebied van biotech en klinische proeven. Toegang hier.

- Bron: https://semiwiki.com/chiplet/341582-moderating-our-open-chiplet-enthusiasm-a-noc-perspective/