De meedogenloze vraag naar SoC's met een lager vermogen is op veel markten duidelijk zichtbaar. Voorbeelden zijn onder meer de allernieuwste mobiele apparaten, IoT- en draagbare apparaten, samen met de hoge rekenvereisten voor AI- en 5G/6G-communicatie. Drijfveren voor een laag stroomverbruik zijn onder meer de levensduur van de batterij, het temperatuurbeheer en, voor toepassingen met een hoog rekenvermogen, de totale bedrijfskosten. Er zijn verschillende benaderingen beschikbaar om een laag vermogen te bereiken. Een rode draad voor velen is de behoefte aan optimale Foundation IP, dat wil zeggen ingebedde herinneringen en logische bibliotheken. Dit is een gebied waarop Synopsys aanzienlijk investeert en marktleider is. Er zijn nu twee informatieve publicaties beschikbaar om u te helpen de beschikbare opties en voordelen te begrijpen. Het blijkt dat het bereiken van extreem laag vermogen met Synopsys Foundation IP-geheugencompilers en logische bibliotheken binnen handbereik is.

Laten we eens kijken naar de informatie die beschikbaar is.

Technisch Bulletin

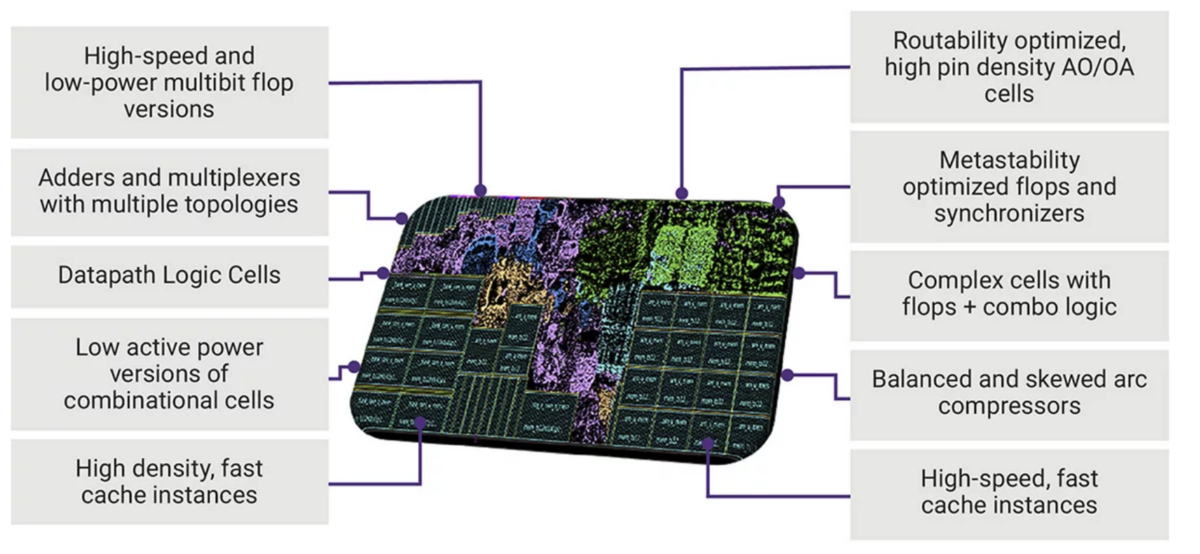

Ik zal beginnen PPA optimaliseren voor HPC- en AI-toepassingen met Synopsys Foundation IP, een technisch bulletin dat zich richt op logicabibliotheken. Het stuk geeft details over de toolbewuste Foundation IP-oplossing van Synopsys. Onderwerpen als geoptimaliseerde schakelingen, ondersteuning voor een breed bedrijfsspanningsbereik en de flexibiliteit om klantspecifieke optimalisaties toe te voegen, worden besproken. Het artikel biedt ook een perspectief op het bereiken van maximaal mogelijke prestaties of de beste afweging tussen vermogen en prestaties. De onderstaande afbeelding geeft een overzicht van de logische bibliotheekcircuits die beschikbaar zijn in de HPC Design Kit.

Details over hoe vermogensverbeteringen worden bereikt, worden gegeven voor veel toepassingen en ontwerpstrategieën. Onderwerpen die aan bod komen zijn onder meer dynamische spanningsschaling over een breed bedrijfsspanningsbereik, het optimaliseren van AI en toepassingsspecifieke acceleratorblok-PPA, oplossingen voor netwerk-op-chip, en hoe de Synopsys HPC Design Kit samen met Synopsys EDA wordt geoptimaliseerd voor een efficiënte SoC-implementatie.

Dit technisch bulletin biedt een rijke reeks informatie en voorbeelden. Jij kan bekijk deze informatie hier.

Wit papier

Er is ook een uitgebreid witboek beschikbaar met de titel: Hoe laag kan je gaan? De grenzen van transistors verleggen. Dit stuk graaft in zowel ingebedde herinneringen als logische bibliotheken. Het onderzoekt de details achter het bereiken van extreem laag vermogen. Verschillende toepassingsgebieden worden besproken, waaronder mobiel, Bluetooth en IoT, high-performance computing, automotive en crypto.

Voor ingebedde geheugens worden verschillende benaderingen besproken, waaronder hulptechnieken en het splitsen van voedingsspanningen. Er wordt op gewezen dat zorgvuldige co-optimalisatie tussen technologie en het ontwerp van geheugenhulpcircuits vereist is om een compacte geheugenwerking met laag vermogen bij lage spanningen te leveren. Verschillende verbeterde hulptechnieken worden besproken. Verbeteringen in het vermogen variëren van 10% tot 37%.

Ook de betrouwbaarheid van herinneringen wordt besproken. Het stuk legt uit dat naarmate de spanning wordt verlaagd, de SRAM-cel degradatie begint te vertonen. Deze degradatie kan meerdere problemen veroorzaken: de leesresultaten zijn verstoord, de bitcel draait niet om, SER wordt uitgesproken, de detectie mislukt, de besturingssignalen wijken af en het BL-signaal verzwakt. Daarom zijn er hulptechnieken nodig om de lagere extreem lage spanningen te ondersteunen die nodig zijn voor geavanceerde toepassingen met laag vermogen.

De benaderingen die Synopsys hier hanteert, maken een aanzienlijk verschil. Strategieën om de betrouwbaarheid te verbeteren en methoden om veroudering te simuleren worden besproken. Je zou de details zelf moeten lezen – er komt een link. De gegevens laten overtuigende resultaten zien, waarbij vijf tot tien levensjaren worden toegevoegd.

Ook worden logische bibliotheken besproken, met strategieën om diepe laagspanningswerking bij 0.4 V en lager mogelijk te maken. Ook architectonische optimalisatie komt aan bod. Standaard celarchitectuurtechnieken kunnen worden gebruikt om zowel het dynamische vermogen als het lekvermogen te verminderen. Synopsys gebruikt bijvoorbeeld stack-gebaseerde versus stage-gebaseerde architectuurtechnieken voor de optimale topologie voor werking op diepe laagspanning. De strategie achter deze aanpak wordt gepresenteerd.

Karakteriseringsoptimalisatie komt ook aan bod. Een belangrijk onderdeel van de karakterisering is het modelleren van procesvariatie binnen een SoC, ook wel on-chipvariatie (OCV) genoemd. Hier worden verschillende geavanceerde technieken gebruikt, waaronder machinaal leren om de nauwkeurigheid te vergroten en de prestaties en het vermogen te optimaliseren.

Het whitepaper wordt afgesloten met een overzicht van hoe alles op SoC-niveau kan worden samengevoegd om werking op diepe laagspanning te bereiken. Spanningsreductie wordt besproken, samen met dynamische spannings- en frequentieschalingstechnieken (DVFS) en verschillende uitschakelstrategieën zoals lichte slaap, diepe slaap, volledige uitschakeling en POFF-modi (Periferie UIT).

In deze whitepaper worden een aantal onderwerpen op het gebied van energieoptimalisatie tot in de kleinste details behandeld. Ik raad het ten sterkste aan. Jij kan bestel hier uw exemplaar. En zo is het bereiken van extreem laag stroomverbruik met Synopsys Foundation IP-geheugencompilers en logische bibliotheken binnen handbereik.

Deel dit bericht via:

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- PlatoData.Network Verticale generatieve AI. Versterk jezelf. Toegang hier.

- PlatoAiStream. Web3-intelligentie. Kennis versterkt. Toegang hier.

- PlatoESG. carbon, CleanTech, Energie, Milieu, Zonne, Afvalbeheer. Toegang hier.

- Plato Gezondheid. Intelligentie op het gebied van biotech en klinische proeven. Toegang hier.

- Bron: https://semiwiki.com/ip/341966-achieving-extreme-low-power-with-synopsys-foundation-ip-memory-compilers-and-logic-libraries/