Tijdens het GOMACTech conferentie die vorige week in South Carolina werd gehouden. Ik had een Zoom-gesprek met Deepak Shankar, oprichter en VP Technology bij Mirabilis Design Inc. om vragen te stellen en een live demo te bekijken van Visuele Sim – een modellerings-, simulatie-, verkennings- en samenwerkingsplatform voor de ontwikkeling van elektronica en SoC's. Wat VisualSim zo onderscheidend maakt, is dat het wordt geleverd met ongeveer 500 hoogwaardige IP-blokken die klaar zijn voor gebruik, waaronder 35 ARM-processors, zo'n 100 processors en meer dan 30 verschillende verbindingen. Gebruikers van VisualSim verbinden deze IP-blokken snel visueel met elkaar om hun systemen te creëren, compleet met netwerken. Een auto-ontwerper kan het hele netwerk modelleren, inclusief 5G-communicatie, Ethernet, SDA en OTA-updates met VisualSim.

Een model op hoog niveau maakt de snelste architectonische verkenning mogelijk en maakt architecturale afwegingen, lang voordat de implementatie zelfs maar met RTL-code begint. Je kunt complexe activiteiten modelleren, zoals een bus, herinneringen en zelfs cache, en zaken als end-to-end vertragingen en latentie meten. Ingenieurs kunnen meten wat de hit/miss-ratio van hun cache is, en wat er gebeurt met verzoeken aan L2-caches. Alle populaire netwerkprotocollen zijn gemodelleerd: AXI, CHI, CMN600, Arteris NOC, UCIe, enz.

Met deze modelleringsaanpak kan een architect een SoC, een compleet vliegtuig- of autosysteem modelleren en vervolgens de prestaties ervan gaan meten om te zien of deze aan de vereisten voldoet. VisualSim is een multi-domein simulator die analoog, software, energiesystemen, digitaal en netwerken in één model kan integreren.

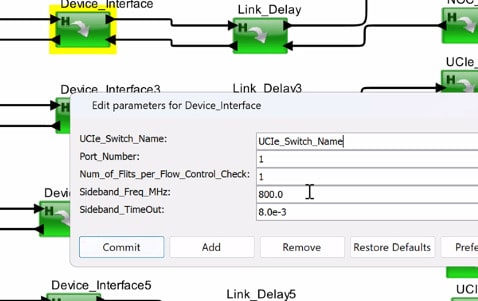

Voor de live demo liet Deepak me een op chiplets gebaseerd ontwerp zien met afzonderlijke chiplets voor de DSP, GPU, AI-processor en CPU, allemaal met elkaar verbonden via UCIe, en elk IP-blok was geparametriseerd om maatwerk en verkenning mogelijk te maken.

Toen we het UCIe-blok binnengingen, was er een IP-adres dat een UCIe-switch werd genoemd, en een gebruiker kan dit blok aanpassen met vijf parameters, allemaal op een hoog niveau.

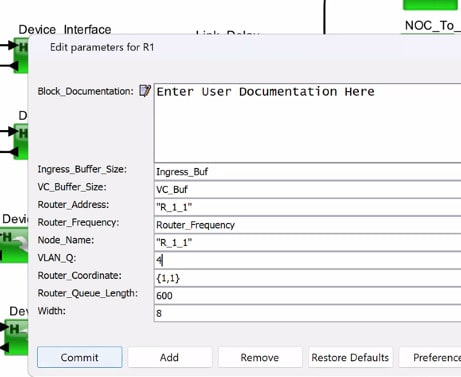

Een router-IP-blok had 10 parameters voor aanpassing.

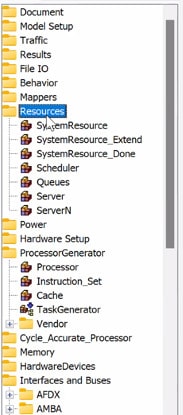

Om elk IP-blok te vinden, was er een schuifbare lijst aan de linkerkant van de GUI, met elke IP-familie in de bibliotheek. Binnen enkele seconden kunt u bladeren, een IP-adres selecteren en beginnen met het aanpassen ervan.

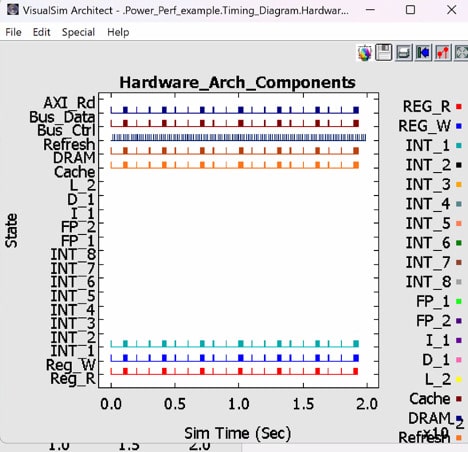

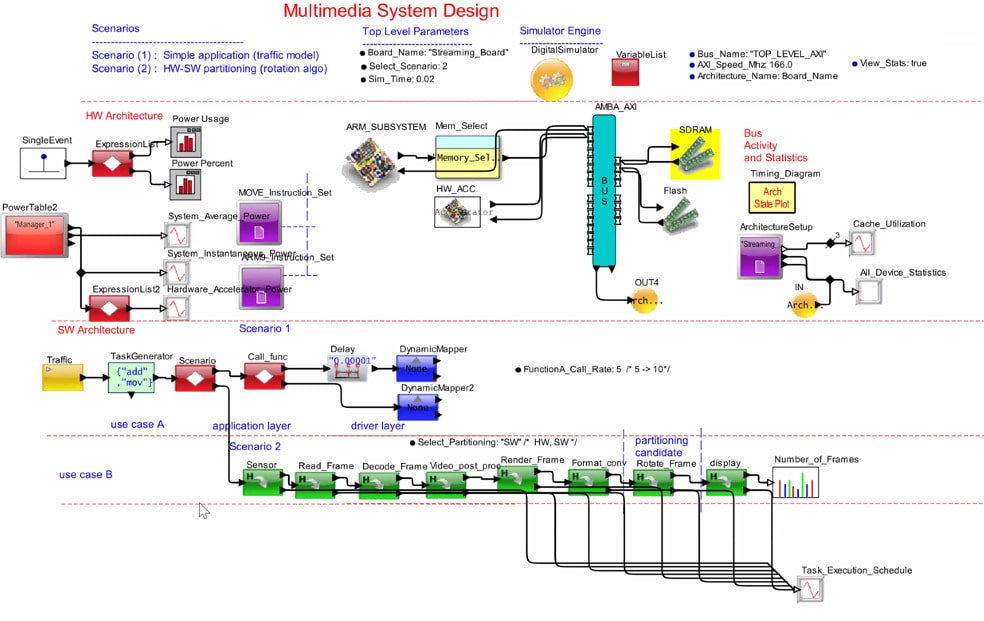

In VisualSim verbindt u elk IP-adres in de gegevensstroom en blijft u op een hoog niveau. De volgende live demo was voor een ontwerp van een multimediasysteem, en het simuleren van 20 ms kostte ongeveer 15 seconden aan muurtijd, uitgevoerd op een laptop. Terwijl de simulatie actief is, kunt u de systeemprestaties bekijken als momentaan vermogen, het pijplijngebruik, het cachegebruik en het geheugengebruik meten en zelfs een timingdiagram bekijken. Deze real-time simulatie veroorzaakte 7.5 miljoen gebeurtenissen en de klant bouwde dit model in minder dan twee weken, inclusief de volledige SoC.

Een ander klantvoorbeeld dat Deepak noemde, omvat 45 masters en werd in ongeveer 4 weken voltooid en volledig getest.

U kunt in elk van de IP-blokken kijken en statistieken zoals geslaagd/mislukt analyseren, en vervolgens begrijpen waarom het mislukte. Er is zelfs een AI-engine die gegevens efficiënter helpt analyseren, zoals het vinden van een bufferoverloop die een fout heeft veroorzaakt. Terwijl uw model actief is, worden er analyses vastgelegd om de systeemprestaties te helpen meten en architecturale knelpunten te identificeren.

VisualSim wordt twee keer per jaar bijgewerkt en er zijn patchupdates voor wanneer er nieuwe IP-blokken worden toegevoegd. Een architect definieert de vereisten in een Excel-bestand, met statistieken zoals latentielimieten en bufferbezetting.

Gebruikers van VisualSim kunnen het bereik van de payloadgrootte definiëren in termen van bytes, snelheidsbereiken en voorkeurswaarden. Uw systeemmodel kan door de combinaties worden geveegd om de beste set parameters te vinden. De simulator begrijpt zelfs hoe hij de min-, max- en voorkeurswaarden moet verkennen. U bepaalt welke systeemparameters worden onderzocht. Vervolgens werd een demo van het multimediasysteem getoond, die vervolgens live werd gesimuleerd.

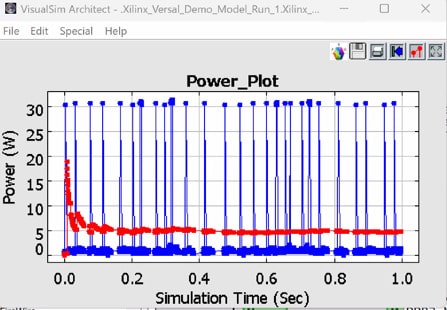

Voor een FPGA-blok kiest u de leverancier en het onderdeelnummer, waarna u de latentie voor elke taak en de kanaalstatistieken van de NOC kunt zien nadat een simulatie is uitgevoerd. Er werd een vermogensdiagram getoond voor 1 seconde werking bij gebruik van Xilinx Versal-onderdelen.

Alle live demo's werden gedraaid op een Windows-laptop. Andere ondersteunde besturingssystemen zijn: Unix, Mac. Het draaien van VisualSim vereist een minimale HW-infrastructuur, omdat de modellen van hoog niveau zijn.

VisualSim-gebruikers ontvangen meer dan 500 voorbeelden die vooraf zijn gebouwd om u snel op weg te helpen, zoals een compleet communicatiesysteem met een antenne, transceiver, FPGA met basisband en Ethernet-interface. Systeemarchitecten die VisualSim gebruiken, kunnen samenwerken met alle specialisten op laag niveau, zoals RTL-ontwerpers.

Afwegingen op systeemniveau kunnen worden gemodelleerd en geëvalueerd, zoals:

- Overstappen van 64-QAM naar QPSK-modulatie

- Snellere tot langzamere processor

- Ethernet-specificaties wijzigen

Als u met VisualSim begint om te modelleren, implementeren en vervolgens te meten, kunt u een nauwkeurigheid van 95% verwachten in vergelijking met de RTL-implementatieresultaten. De belofte van het gebruik van modellen op hoog niveau is het elimineren van prestatieproblemen vóór implementatie of integratie. Er is werkelijk geen codering vereist voor een heel systeemmodel.

Mirabilis heeft tot nu toe wereldwijd 65 klanten en zo'n 250 projecten voltooid. Enkele van de bekende klanten zijn: NASA, Samsung, Qualcomm, Broadcom, GM, Boeing, HP, Imagination, Raytheon, AMD, Northrup Grumman.

Samengevat

Vroeger heeft een systeemontwerper misschien zijn ideeën op een servet getekend terwijl hij in een restaurant aan het eten was, en vervolgens weer aan het werk gegaan en een aantal Excel-spreadsheets met geheimzinnige vergelijkingen in elkaar gezet om een model te creëren. Vandaag is er een nieuwe keuze, en dat is geven Visuele Sim van Mirabilis een keer proberen. U kunt nu een heel systeem in slechts een paar weken modelleren, architectonische afwegingen maken terwijl u daadwerkelijke simulaties uitvoert, en dat allemaal voordat u ingaat op gedetailleerde implementatiedetails.

Gerelateerde blogs

Deel dit bericht via:

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- PlatoData.Network Verticale generatieve AI. Versterk jezelf. Toegang hier.

- PlatoAiStream. Web3-intelligentie. Kennis versterkt. Toegang hier.

- PlatoESG. carbon, CleanTech, Energie, Milieu, Zonne, Afvalbeheer. Toegang hier.

- Plato Gezondheid. Intelligentie op het gebied van biotech en klinische proeven. Toegang hier.

- Bron: https://semiwiki.com/ip/343387-a-modeling-simulation-exploration-and-collaborative-platform-to-develop-electronics-and-socs/