De toenemende uitdagingen en stijgende kosten van logica-schaling, samen met de vraag naar een toenemend aantal functies, dwingen steeds meer bedrijven naar geavanceerde verpakkingen. En hoewel dat een hele reeks nieuwe opties opent, veroorzaakt het ook wijdverbreide verwarring over wat het beste werkt voor verschillende processen en technologieën.

In de kern is geavanceerde verpakking afhankelijk van betrouwbare verbindingen, goed gedefinieerde signaalpaden en het minimaliseren van hinderlijke effecten zoals invoegverliezen, overspraak van verbindingen, kromtrekken van het substraat en hotspots in het systeem. Deze parameters kunnen aanzienlijk variëren, afhankelijk van de pakketkeuze, die van alles kan zijn, van 2.5D, fan-out chip-on-substrate (FOCoS), 3D-IC's of bruggen die afzonderlijk of in combinatie met de andere benaderingen kunnen worden gebruikt. .

En dat is nog maar het begin. Roadmaps voor halfgeleiderverpakkingen leggen steeds de nadruk op robuuste interfaces, maar welke de juiste is voor een bepaalde toepassing is niet altijd duidelijk, omdat er veel manieren zijn om tot een eindresultaat te komen. Er zijn ook een hele reeks nieuwe processen, waaronder wafer-to-wafer bonding, stroomverdeling aan de achterkant en co-packaging-optica in pakketten. Silicium-interposers (bruggen) bieden communicatie met de hoogste bandbreedte, terwijl organische interposers drastisch goedkoper zijn en passieve componenten kunnen inbedden langs de interconnectieroute van RDL naar C4-bumping.

Nieuwe materialen en architecturen

Sinds de uitvinding van de eerste IC hebben ingenieurs gedebatteerd over de fundamenten van het ene materiaal versus het andere. In de begindagen was het silicium versus germaniumhalfgeleiders, altijd met als einddoel het maken van kosteneffectieve elektronica. De overvloed aan silicium en zijn vermogen om een natuurlijk oxide te laten groeien, vergemakkelijkten de integratie en zorgden voor betrouwbaarheid, waardoor het het substraat bij uitstek werd.

Snel vooruit naar vandaag en de maakbaarheid in geavanceerde verpakkingen ondergaat een soortgelijke metamorfose als ASIC's ooit ondergingen. In de medische, biotech-, HPC-, mobiele en 5G/6G-sector keren ingenieurs terug naar fysische en chemische principes om de beste manier te bepalen om fotonica, micro-elektronica, siliciumbruggen met herverdelingslagen en chipcommunicatie te combineren met medische elektronica.

De truc is het ontwerpen van chips voor pakketten met behulp van een robuuste architectuur die bestand is tegen temperatuurstresscycli en een specifiek gebruiksscenario doorstaat.

Tegelijkertijd staan chipmakers onder druk om eerder modules op systeemniveau te leveren. Ironisch genoeg vraagt dit in sommige gevallen om processen met lagere temperaturen om apparaten dichter bij elkaar en op nieuwe plaatsen, zoals het menselijk lichaam, effectief te kunnen inbedden.

“Er zijn maar een beperkt aantal metalen die we kunnen gebruiken voor implanteerbare apparaten, zoals goud, platina en sommige chroomstaalsoorten. We kunnen aluminiumoxide gebruiken, maar weinig polymeren zijn geschikt bij blootstelling aan organische media”, zegt Dick Otte, CEO van Promex. Bestaande processen kunnen worden ontworpen voor nieuwe toepassingen zoals implanteerbare medische apparaten of testers voor eenmalig gebruik om glucosewaarden of een ziekteverwekker zoals een Covid-virus te detecteren.

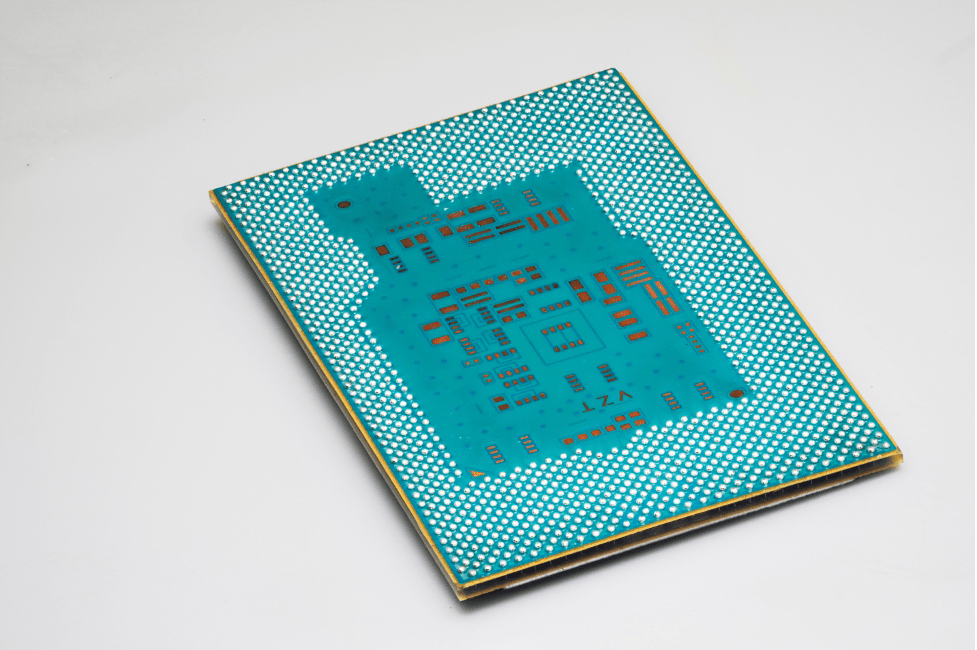

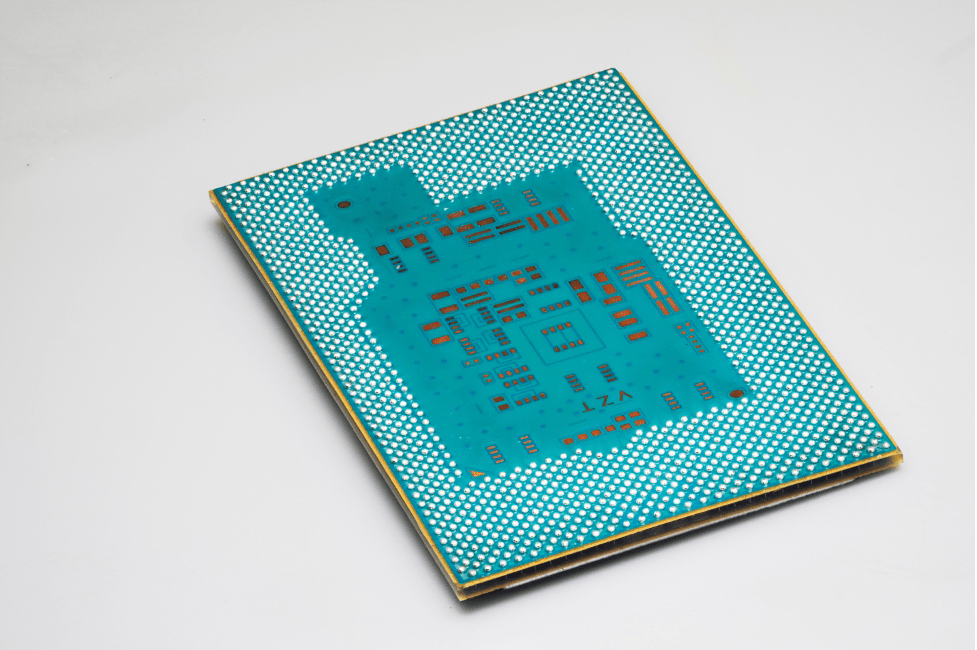

Bij high-performance computing zorgen problemen die voortkomen uit kromtrekken en spanningsschommelingen veroorzaakt door temperatuurwisselingen voor een grootschalige verandering van organische substraten naar glas. Intel heeft onlangs prototypen aangekondigd van chips op een glassubstraat die een pad bieden naar voortdurende schaalvergroting van functies en verbeterde vermogensafgifte in krachtige systemen (zie figuur 1).

Fig. 1: BGA-zijde van een geassembleerde testchip van een glazen substraat. Bron: Intel

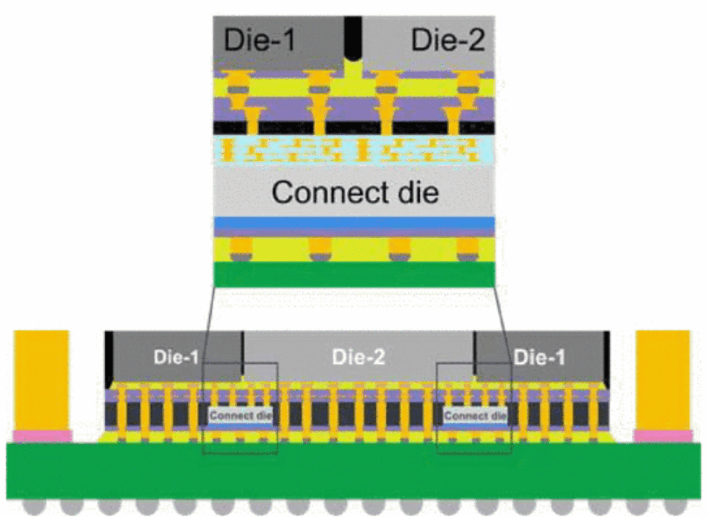

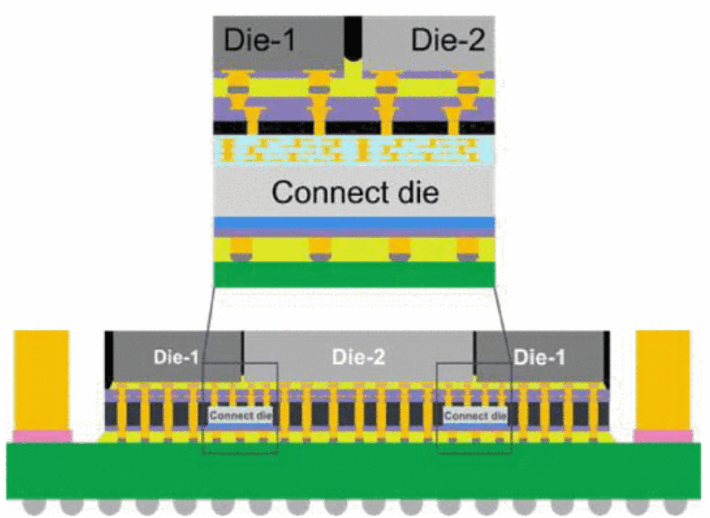

In plaats van stijve glassubstraten verminderen fan-out-benaderingen met siliciumbruggen de behoefte aan kostbare meerlaagse laminaatsubstraten, die de afgelopen jaren schaars waren. Een siliciumbrug kan worden gezien als de beste combinatie van de side-by-side 2D-benaderingen met een fan-out chip op substraat, FOCoS (zie figuur 2).

Fig. 2: Bij het integreren van een siliciumbrug met hoge bandbreedte (lijnen en ruimtes van 0.5 µm), hangt de kromming van het systeem af van de matrijsdikte (450 tot 650 µm), het maloppervlak en de CTE van de epoxyvormmassa. Bron: Amkor

Bridge-methoden bieden andere voordelen aan de prestatiekant. “Bij bridge-die-verbindingen profiteert het signaalpad van de kleine afstand tussen de matrijzen, in de orde van 1 tot 2 millimeter, zodat ze goed elektrisch kunnen communiceren”, zegt Mike Kelly, vice-president van Advanced Packaging and Integration bij Amkor. “Het is mechanisch gezien en vanuit het oogpunt van betrouwbaarheid een ingewikkelder systeem, en we kunnen gemengde functionaliteit zoals RF en logica in één pakket hebben.”

Het wordt duidelijk dat silicium-tussenbruggen vanwege de kosten zo klein mogelijk moeten zijn. Uit een analyse door Amkor-ingenieurs bleek dat dunnere actieve matrijzen in de FOCoS-brugconstructie gevoeliger zijn voor kromtrekken. Het werk wees ook op de positieve effecten van het gebruik van vormmassa's met een lagere thermische uitzettingscoëfficiënt (CTE) als tweede orde effect. [1]

Herverdelingslagen met bredere lijnen en spaties (tot 2 µm L/S) beheren het tweede niveau van verbindingssnelheid binnen deze pakketten. Over het geheel genomen zal het thermische dissipatiepad uit de bovenkant van dergelijke grote systemen (meer dan 3x de reticulegrootte) een nog hogere geleidbaarheid vereisen om warmte te verwijderen dan bestaande thermische interfacematerialen (TIM's). Uiteindelijk zullen waarschijnlijk metalen TIM's nodig zijn.

Simpel gezegd: dicht bij elkaar geplaatste logica-chips hebben de neiging op te warmen als één grote logica-chip in een pakket, waarbij HBM zich aan de systeemrand bevindt. Dit is de reden waarom ASE zijn brugtechnologie promoot, waarbij wordt opgemerkt dat de silicium-interposer (koper/SiO2) lagen in de orde van grootte van 1 µm lijnen en ruimtes die de neiging hebben hogere invoegverliezen en overspraak tussen koperlijnen te veroorzaken dan in FOCoS-interposers, die bredere koper- en polyimide-afmetingen hebben (3 tot 4 µm). Een belangrijk voordeel, naast de hoge bandbreedte en hoge snelheidscommunicatie in siliciuminterposers, is de flexibiliteit in de routering van grondsporen rond de I/O-signalen, waardoor de overspraak wordt verminderd. [2]

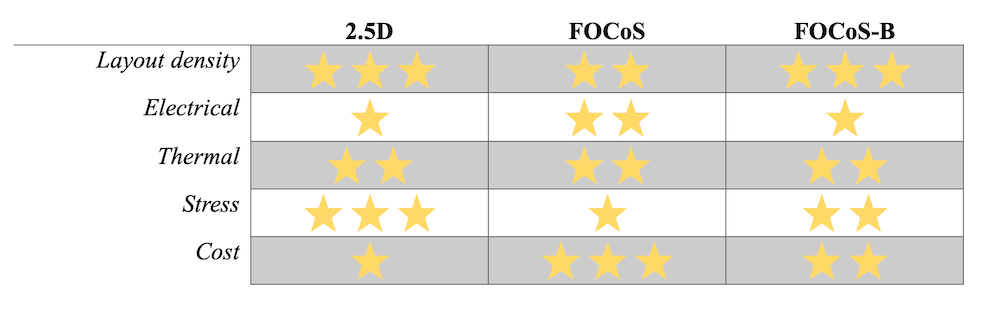

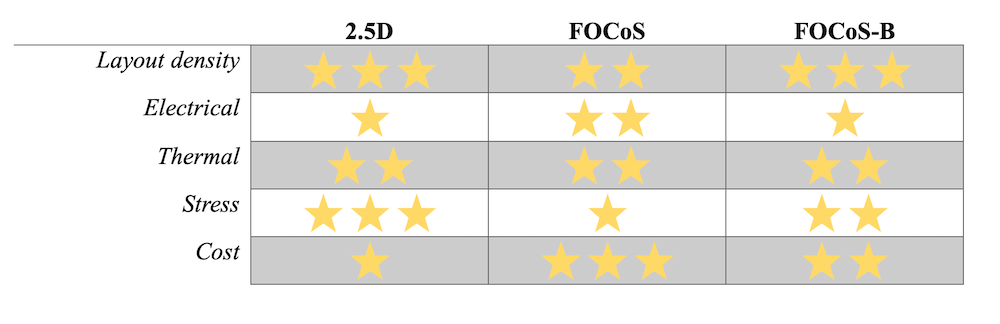

Als gevolg hiervan hebben ingenieurs en pakketontwerpers binnen de 2.5D-, FOCoS- en FOCoS-bridge-technologieën opties om de lay-outdichtheid, elektrische/thermische/stressprestaties en kosten af te wegen, afhankelijk van de specifieke toepassing van de module (zie figuur 3), zoals samengevat door ASE-ingenieurs. “Er kan worden verwacht dat de omvang van geavanceerde verpakkingen steeds groter zal worden, en dat de prestaties op het gebied van kromtrekken en spanningen tijdens het assemblageproces belangrijker zullen worden”, zeiden ze.

Fig. 3: De verschillende kenmerken van 2.5D-, FOCoS- en bridge-technologieën. Een brug beheert spanningen beter dan FOCoS, maar niet zo goed als 2.5D-benaderingen. Bron: ASE

Tegelijkertijd zullen binnenkort co-verpakte optica beschikbaar zijn voor datacenters. Babak Sabi van Intel, senior vice-president van de ontwikkeling van assemblagetesttechnologie bij Intel, hield een connector met optische ingangen omhoog tijdens een paneldiscussie op de recente Semicon West. "Bij verpakking draait alles om onderlinge verbindingen, en we brengen veel kernen en geheugen samen, en mensen praten over de integratie van producten op waferniveau", zei hij. “Dit is waar het glassubstraat uiterst belangrijk is, omdat we de interposer volledig kunnen elimineren.”

Naast een routekaart voor het integreren van glassubstraten voor betere prestaties en grootschalige controle op kromtrekken, sprak Sabi over de adoptie van optische verbindingen. "Tegen het einde van dit decennium zullen we optische apparaten in veel verschillende formaten gaan zien", zei hij, waarbij hij opmerkte dat Intel en zijn partners werken aan een "standaard" connector voor optische interfaces met chips. Hij gebruikte de analogie van een verbinding waar consumenten heel vertrouwd mee zijn: USB-C. Voor hyperscale netwerken kan een industriestandaard optische connector de bungelende vezels en semi-geautomatiseerde benaderingen van hedendaagse verbinding met siliciumfotonica elimineren, waardoor superieure produceerbaarheid en automatisering mogelijk worden.

De noodzaak om front-end waferverwerking te integreren met geavanceerde verpakkingen zorgt ook voor veranderingen in de procesontwikkeling. Applied Materials presenteerde onlangs zijn routekaart voor de gezamenlijke ontwikkeling van hybride bonding- en geavanceerde matrijsplaatsingstools van verschillende leveranciers met het nieuwste op vacuüm gebaseerde meerkamerplatform van Applied Materials. De noodzaak om processen zoals CMP te integreren met hybride bonding en geavanceerde plaatsingstools leidt bijvoorbeeld tot partnerschappen tussen Applied, EV Group en BESI, en dit gebeurt ook onder andere leveranciers en R&D-hubs wereldwijd.

Hoe dun kunnen wafers en apparaten worden?

Al deze ontwikkelingen vereisen dunnere siliciumwafels, die op hun beurt onder meer slankere mobiele telefoons, horloges en implanteerbare apparaten mogelijk maken.

Dat maakt ze ook moeilijker om mee te werken en gevoeliger voor procesvariaties en defecten. Maar wafers moeten worden uitgedund voor integratie op 3D-apparaatniveau, en ze zullen nieuwe soorten verbindingen vereisen, zoals hybride bonding, een technologie die door Sony is ontwikkeld met CMOS-beeldsensoren. Over het algemeen worden wafers verdund van ongeveer 600 tot 50 µm en minder.

De vooruitgang van apparaten van millimeterformaat naar kleinere microLED's of microOLED's die op de rand van een bril passen, en wegwerpbare biotechtesters, vereist ook nieuwe manieren om naar de montage te kijken. En hoewel het erop lijkt dat silicium-interposers veilig binnen het domein van de fabrieken zullen blijven, werken de OSAT's, materiaal- en apparatuurleveranciers samen om nieuwe of substantieel gewijzigde processen te leveren.

“In de biotechnologie komt veel complexe chemie kijken omdat ze gebruik maken van een soort moleculaire interactie – die de elektronica, chemie of MEMS detecteren en proberen te matchen – waaruit blijkt dat er een ziekteverwekker aanwezig is of niet”, zegt Otte van Promex. “Dus hebben we het assemblageproces aangepast om schade aan die onderdelen te voorkomen, bijvoorbeeld door een uithardingsproces bij kamertemperatuur te ontwikkelen.”

Otte legde uit dat biotech-apparaten, omdat ze interactie hebben met de patiënt en vervolgens signalen naar de buitenwereld sturen, geen standaard halfgeleiderprocessen kunnen ondergaan, zoals massareflow bij 220 °C, blootstelling aan UV-licht of ultrasone agitatie in gedeïoniseerd water. Het kan twee of meer jaar duren voordat de ontwikkeling volgens specificaties in de biotech- of medische elektronica aan de specificaties voldoet, en modules vereisen doorgaans mechanische structuren (microfluïdica) die niet aan water kunnen worden blootgesteld. Dergelijke nieuwe vereisten zullen nieuwe processen blijven aandrijven

Achterkantkracht, hybride binding en nieuwe materialen

Er zijn ook andere veranderingen op komst. Wat er in principe wordt gebruikt, komt neer op natuurkunde, scheikunde, apparaatprestaties en kosten, maar dat omvat veel opties die kunnen worden aangepast voor een specifieke toepassing of gebruikssituatie.

De stroomafgifte aan de achterkant zal als eerste verschijnen bij de best presterende chips. Deze aanpak plaatst de stroomtoevoer naar transistors op de achterkant van de wafer, die bredere verbindingen vereisen, terwijl alleen signaallijnen aan de voorkant van de apparaten worden gevoerd, waardoor CD voor de toepassing wordt geoptimaliseerd. BPD kan de betrouwbaarheid verbeteren en tegelijkertijd de weg vrijmaken voor de integratie van eenvoudige apparaten aan de achterkant.

BPD en hybride bonding zijn tegenwoordig twee van de populairste onderwerpen op het gebied van halfgeleiders. Elk omvat verschillende benaderingen, en deze benaderingen omvatten verschillende niveaus van complexiteit. Hetzelfde geldt voor dragers gemaakt van siliciumwafels of glas, die elk hun voor- en nadelen hebben. Glas is bijvoorbeeld erg vlak en wordt doorgaans hergebruikt in dragertoepassingen.

Een ander relatief nieuw proces is het onthechten van dragers om dunne wafelverwerking mogelijk te maken. In een recent werk onthulden imec en Brewer Science de details van een de-bondingproces van glasdragers dat wordt geoptimaliseerd voor ultradunne wafers (50 µm tot 20 µm). [3] Op glaswafels van 300 mm combineerden ingenieurs drie chemische stoffen, waaronder een verwijderaar van randkralen, tijdelijk hechtmateriaal en een loslaatlaag die waren geoptimaliseerd voor een schone loslating van dunne siliciumwafels van 300 mm van een drager met behulp van een mechanisch (blad) loslaatmechanisme.

Het proces is geoptimaliseerd om compatibiliteit met oxiden aan de achterkant van wafers en dual-damasceneverwerking te garanderen, terwijl onbedoeld verlies of contaminatie van waferadhesie wordt voorkomen, terwijl wordt voldaan aan de specificaties voor de diktevariatie (TTV) over de wafer heen. Het mogelijk maken van het vrijgeven van dunne wafers is slechts een van de vele processen die belangrijk zijn om benaderingen van stroomverdeling aan de achterkant te laten werken.

Conclusie

As OSAT's ervaring opdoen met het integreren van nieuwe brugtechnologieën, kan de aanpak prestatie- en kostenvoordelen opleveren die tussen FOCoS- en 2.5D-integratiebenaderingen liggen, waardoor de opties die beschikbaar zijn voor ontwerpers worden uitgebreid. Het gebruik van deze verpakkingsbenaderingen met hoge dichtheid is echter nog steeds beperkt tot chipfabrikanten met interne wafer-tot-pakket-integratieniveaus.

Ondertussen bedenken ingenieurs creatieve oplossingen voor het assembleren van biotech- en medische elektronica.

Bedrijven werken samen om de wereld van de wafelproductie, de assemblage en de verpakking beter te overbruggen. Het verbinden en onthechten van wafer- en glasdragers zal waarschijnlijk een steeds grotere rol gaan spelen nu chipmakers lagen in driedimensionale apparaten blijven combineren.

Referenties

- H. Jang et al., “Reliability Performance of S-Connect Module (Bridge Technology) for Heterogeneous Integration Packaging”, 2023 IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, VS, 2023, pp. 1027-1031 , doi: 10.1109/ECTC51909.2023.00175.

- C. -C. Wang et al., “Creative Design and Structure Applied to Chiplets Packaging”, 2023 IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, VS, 2023, pp. 1353-1358, doi: 10.1109/ECTC51909.2023.00231.

- K. Kennes et al., "Procesuitdagingen tijdens CVD-oxideafzetting op de achterkant van 20 µm dunne wafers van 300 mm die tijdelijk zijn gebonden aan glasdragers", 2023 IEEE 73e Electronic Components and Technology Conference (ECTC), Orlando, FL, VS. , 2023, blz. 1584-1589, doi: 10.1109/ECTC51909.2023.00269.

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- PlatoData.Network Verticale generatieve AI. Versterk jezelf. Toegang hier.

- PlatoAiStream. Web3-intelligentie. Kennis versterkt. Toegang hier.

- PlatoESG. carbon, CleanTech, Energie, Milieu, Zonne, Afvalbeheer. Toegang hier.

- Plato Gezondheid. Intelligentie op het gebied van biotech en klinische proeven. Toegang hier.

- Bron: https://semiengineering.com/building-better-bridges-in-advanced-packaging/