Mijn IC-ontwerpcarrière begon met DRAM-ontwerp in 1978, dus ik heb de ontwikkelingen op dit gebied van geheugenontwerp in de gaten gehouden om onderweg de ontwerpuitdagingen, procesupdates en innovaties op te merken. Synopsys organiseerde een geheugentechnologie symposium in november 2022, en ik kreeg de kans om een presentatie te bekijken van SK hynix-ingenieurs, Tae-Jun Lee en Bong-Gil Kang. DRAM-chips hebben een hoge capaciteit en snelle datasnelheden van 9.6 gigabit per seconde bereikt, zoals de recente LPDDDR5T bekendmaking op 25 januari. Gegevenssnelheden kunnen worden beperkt door de integriteit van het Power Delivery Network (PDN), maar het analyseren van een full-chip DRAM met PDN zal de simulatietijden te veel vertragen.

De piekgeheugenbandbreedte per x64-kanalen is gedurende verschillende generaties gestaag gegroeid:

- DDR1, 3.2 GB/s bij 2.5 V voeding

- DDR2, 6.4 GB/s bij 1.8 V voeding

- DDR3, 12.8 GB/s bij 1.5 V voeding

- DDR4, 25.6 GB/s bij 1.2 V voeding

- DDR5, 51.2 GB/s bij 1.1 V voeding

Een grote uitdaging bij het behalen van deze agressieve timingdoelen is het beheersen van de parasitaire IR-drop-problemen die worden veroorzaakt tijdens de IC-lay-out van de DRAM-array. vertraagt de prestaties van het geheugen.

De geëxtraheerde parasitaire gegevens voor een IC worden opgeslagen in een SPF-bestandsindeling, en het toevoegen van deze parasitaire gegevens voor de PDN aan een SPICE-netlijst zorgt ervoor dat de circuitsimulator met een factor 64x vertraagt, terwijl het aantal parasitaire RC-elementen dat door de PDN wordt toegevoegd, is 3.7x meer dan alleen signaalparasieten.

Bij SK hynix kwamen ze met een pragmatische aanpak om de simulatielooptijden te verkorten bij het gebruik van de PrimeSim™ Pro circuitsimulator op SPF-netlijsten inclusief de PDN door gebruik te maken van drie technieken:

- Verdeling van de netlijst tussen Power en andere signalen

- Vermindering van RC-elementen in het PDN

- Tolerantie voor simulatiegebeurtenissen regelen

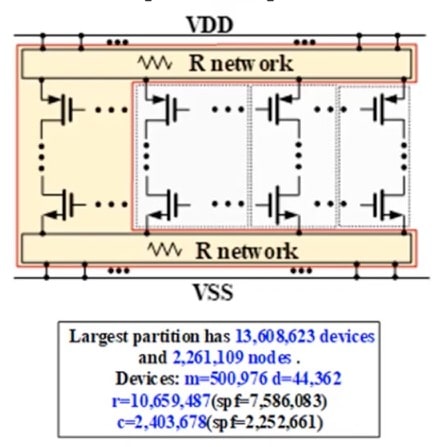

PrimeSim Pro gebruikt partitionering om de netlijst op te delen op basis van connectiviteit, en standaard zouden de PDN en andere signalen samen zeer grote partities vormen, wat op zijn beurt de simulatietijden te veel vertraagde. Zo zag de grootste partitie eruit met standaard simulatorinstellingen:

Een optie in PrimeSim Pro (primesim_pwrblock) werd gebruikt om de grootte van de grootste partitie te verkleinen, waardoor de PDN werd gescheiden van andere signalen.

De geëxtraheerde PDN in SPF-indeling had te veel RC-elementen, waardoor de looptijd van circuitsimulatie vertraagde, dus een optie genaamd primesim_postl_rcred werd gebruikt om het RC-netwerk te verkleinen, terwijl tegelijkertijd de nauwkeurigheid behouden bleef. De RC-reductieoptie kon het aantal RC-elementen tot 73.9% verminderen.

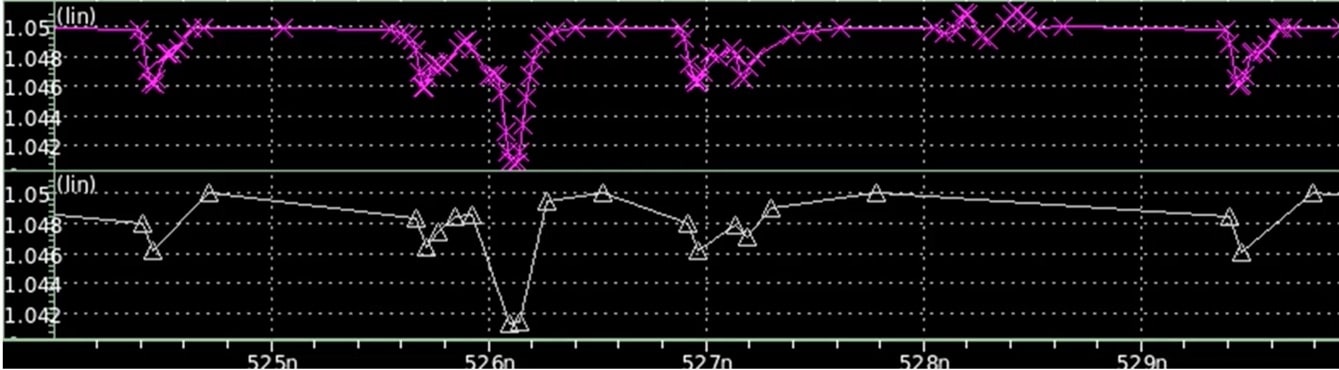

Circuitsimulatoren zoals PrimSim Pro gebruiken matrixberekeningen om stroom en spanningen in de netlijstpartities op te lossen, dus looptijd is direct gerelateerd aan matrixgrootte en hoe vaak een spanningsverandering herberekening vereist. De simulatoroptie primesim_evtgrid_for_pdn werd gebruikt, en het vermindert het aantal keren dat een matrix moet worden opgelost wanneer er kleine spanningsveranderingen zijn in de PDN. De hieronder in paars weergegeven grafiek heeft een X op elk tijdstip waarop het oplossen van matrixen in de PDN standaard vereist was, vervolgens worden in het wit driehoeken weergegeven op elk tijdstip waarop het oplossen van matrixen wordt gebruikt met de simulatoroptie. De witte driehoeken komen veel minder vaak voor dan de paarse X's, waardoor hogere simulatiesnelheden mogelijk zijn.

Een laatste FineSim Pro-simulatoroptie die werd gebruikt om looptijden te verkorten, was primesim_pdn_event_control=a:b, en het werkt door een ideale voedingsbron toe te passen voor a:b, wat resulteert in minder matrixberekeningen voor de PDN.

De verbeteringen in de looptijd van de simulatie door alle FineSim Pro-opties gecombineerd te gebruiken, waren een versnelling van 5.2x.

Samengevat

Ingenieurs bij SK hynix hebben zowel de FineSim- als de PrimeSim-circuitsimulators gebruikt voor analyse in hun geheugenchipontwerpen. Het gebruik van vier opties in PrimeSim Pro heeft voldoende snelheidsverbeteringen opgeleverd om full-chip PDN-analyse mogelijk te maken, inclusief SPF-parasieten. Ik verwacht dat Synopsys zal blijven innoveren en hun circuitsimulatorfamilie zal blijven verbeteren om de groeiende uitdagingen van geheugenchips en andere IC-ontwerpstijlen het hoofd te bieden.

Gerelateerde blogs

Deel dit bericht via:

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- Platoblockchain. Web3 Metaverse Intelligentie. Kennis versterkt. Toegang hier.

- Bron: https://semiwiki.com/eda/324168-power-delivery-network-analysis-in-dram-design/