Hergebruik van ontwerpen heeft IC-ontwerpteams in staat gesteld ontwerpen van miljarden transistors te creëren waarbij honderden IP-blokken vooraf zijn opgebouwd uit interne of externe bronnen. Het bijhouden van waar elk van deze IP-blokken vandaan komt, wat hun versiestatus is, het beheren van IP, of zelfs het achterhalen van hun licentiestatus kan een fulltimebaan zijn als dit met handmatige methoden wordt bijgehouden. Andere grote vragen die moeten worden beantwoord, zijn waar u het juiste IP-adres kunt vinden, of hoe u anderen ervan bewust kunt maken dat u een nieuw IP-adres heeft gecreëerd dat voor nieuwe projecten kan worden hergebruikt.

Bedrijven als Cliosoft, nu onderdeel van Keysight-EDA, automatiseren al jaren functies voor IP-hergebruik, zoals het vinden van IP, het creëren van nieuwe IP en het veilig hergebruiken van IP in systemen. Er is een webinar op 1 november om 10:00 uur PT gepland, Beheersing van de kunst van het beheren van IP, chiplets en ontwerpgegevens.

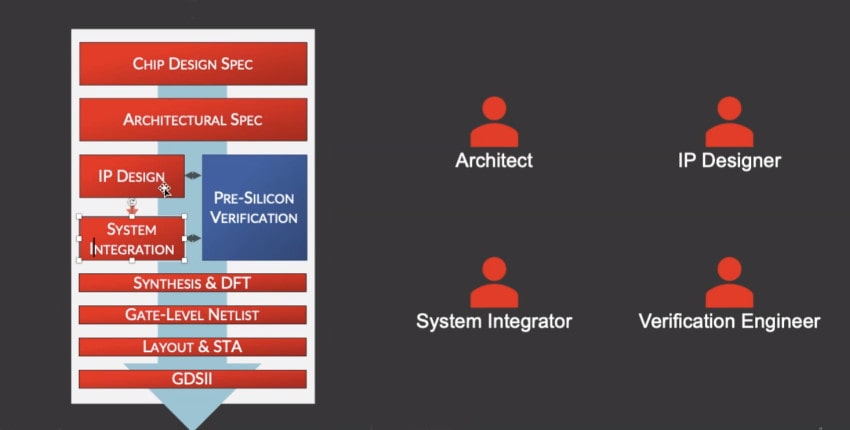

De basis SoC-ontwerpstroom zal in het webinar worden besproken, samen met de meerdere technische rollen die het ontwerp- en verificatieteam vormen. Het is cruciaal voor succes dat elk van deze teamleden een manier heeft om te communiceren en samen te werken tijdens de projectideeën en -implementatie.

Het vinden van het juiste IP-blok, zowel intern als bij externe leveranciers, wordt geautomatiseerd met Keysight IP-beheer (HUB) hulpmiddel. Systeemarchitecten verdelen een complex ontwerp doorgaans in kleinere stukken, waarbij ze hiërarchie als abstractie gebruiken, en identificeren vervolgens alle benodigde IP-blokken. De leden van de ontwerp- en verificatieteams kunnen geografisch verspreid zijn, wat communicatie- en documentatieproblemen veroorzaakt. Goede tools voor gegevensbeheer helpen bij deze taken: het verdelen van een elektronisch ontwerp, het beveiligen van de benodigde IP-blokken en zelfs het geofencing van IP om te voldoen aan licentieovereenkomsten.

In het webinar komen zowel de SoC-stroom als de Chiplet-ontwerpstromen aan bod in termen van het beheren van IP- en ontwerpgegevens. Veel voorkomende uitdagingen bij het systeemontwerp zijn onder meer het beheren van de stuklijst, het oplossen van IP-versieconflicten, het samenstellen van IP-subsystemen, het veilig verbinden van IP-blokken met een NoC en het hergebruiken van ontwerpkennis van het verbinden met NoC's.

Een teamlid kan de status van een IP-blok bijwerken door een tag aan dat blok te koppelen, zoals Verification Ready, en vervolgens automatisch andere teamleden op de hoogte stellen van de statuswijziging, zodat iedereen de geschiedenis en volgorde kent van wie aan elk IP-blok heeft gewerkt. en wat de volgende stap is in de ontwerpstroom. Een ingenieur kan een IP-blok taggen als RTL Signoff, waarna een workflow een momentopname of versie van die hiërarchie activeert die wordt gebruikt voor toekomstige audits, en uiteindelijk e-mails naar alle belanghebbenden stuurt. Industrieën als het Ministerie van Defensie en de lucht- en ruimtevaart stellen strenge eisen aan het volgen van specificaties en vereisten tot implementatie, dus het uitvoeren van audits is vereist voor traceerbaarheid.

Juridische teams willen ook weten welk IP-adres is opgenomen in elk ontwerp dat wordt verzonden, zodat ze contractovereenkomsten voor gelicentieerde IP-blokken goed kunnen beheren.

De Cliosoft-tools zijn volledig geïntegreerd in de Keysight EDA-toolflow, samen met IC-toolflows van Cadence en Synopsys. Gebruikers van EDA-tools blijven binnen hun favoriete leverancierstool en hebben toegang tot alle Data Management (DM)-functies, wat zorgt voor een snelle leercurve. Projectmanagementtools zoals Jira zijn ook geïntegreerd, samen met tools voor het volgen van bugs zoals Bugzilla.

Samengevat

Woon het webinar bij op 1 november om 10:00 uur PT voor meer informatie over data- en IP-beheer, en zelfs over het beheer van de technische levenscyclus, van chipspecificatie tot tapeout. Zowel SoC- als chiplet-ontwerpbenaderingen profiteren van het gebruik van automatisering die verder gaat dan wat een typisch PLM-systeem kan bieden.

Gerelateerde blogs

Deel dit bericht via:

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- PlatoData.Network Verticale generatieve AI. Versterk jezelf. Toegang hier.

- PlatoAiStream. Web3-intelligentie. Kennis versterkt. Toegang hier.

- PlatoESG. carbon, CleanTech, Energie, Milieu, Zonne, Afvalbeheer. Toegang hier.

- Plato Gezondheid. Intelligentie op het gebied van biotech en klinische proeven. Toegang hier.

- Bron: https://semiwiki.com/eda/336838-managing-ip-chiplets-and-design-data/