Op 13 september 2021 heeft Andes Technology Corporation met succes zijn openbare aanbieding van de DDR (Global Depositary Receipt) uitgegeven op de beurs van Luxemburg. Destijds maakte het Andes tot de enige internationale openbare RISC-V Instruction set architecture (ISA) CPU IP-leverancier. Hierdoor konden investeerders over de hele wereld deelnemen aan de groei die Andes voor ogen had voor RISC-V. Deze kapitaalinjectie zou de ambitie van Andes voeden om leider te worden in de snel evoluerende, snelgroeiende, open standaard RISC-V-markt. In 2015 erkende Andes het enorme potentieel voor de RISC-V ISA en werd hij oprichter en premier van RISC-V International.

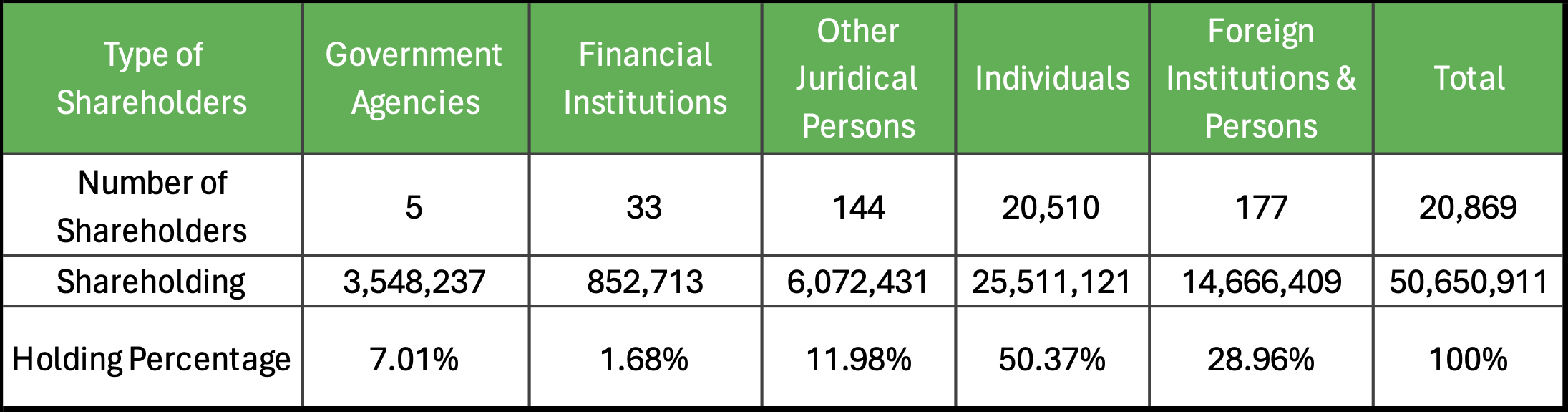

Vanaf 2 april 2023; Eenheid: aandelen, %

De investering heeft aanzienlijk vruchten afgeworpen, vooral omdat deze samenviel met de ratificatie van de RISC-V Vector Extension in november 2021. Deze gebeurtenis markeerde een keerpunt in de evolutie van de RISC-V-instructiesetarchitectuur. De RISC-V-vectorextensie kwam op een moment dat datacentercomputers aan het veranderen waren van verwerking voor algemene doeleinden naar AI-verwerking, die extreem grote datasets verwerkt. Vectorverwerking blinkt uit in efficiënte verwerking van grote arrays of gestructureerde gegevens. Vectorverwerking heeft het potentieel om van RISC-V de volgende grote wereldwijde ISA te maken.

De zeer parallelle architectuur van een vectorprocessor vermindert de latentie en overhead. Het bereikt een betere energie-efficiëntie door het maximaliseren van het gebruik van CPU-bronnen en het minimaliseren van inactieve cycli, waardoor hogere prestaties per watt worden gerealiseerd. Bovendien is de hardware voor het implementeren van RISC-V Vectorverwerkingseenheden (VPU's) en vectorregisters eenvoudiger dan zeer parallelle architecturen die worden gebruikt voor grafische verwerking. En VPU's bieden een veel minder complex programmeermodel.

De R&D-teams van Andes in zowel de Noord-Amerikaanse vestiging als het uitgebreide personeelsbestand in Taiwan hebben zich geconcentreerd op het ontwikkelen van geavanceerde architecturen voor hoogwaardige RISC-V-processors. De twee bereikten met name een belangrijke mijlpaal door de eerste RISC-V vector (RVV)-motor te ontwikkelen, de AndesCore™ NX27V, gebaseerd op de RISC-V International RVV-specificatie. Het ontwerp, dat de behendigheid en innovatie van het technische team van Andes demonstreert, werd binnen een jaar voltooid en was gebaseerd op versie V0.8 van de RISC-V-vectorextensiespecificatie, en later aangepast naar versie V1.0 toen RVV werd geratificeerd. Deze prestatie leidde tot een aantal grote OEM-ontwerpoverwinningen.

Vorig jaar presenteerde META op de International Symposium on Computer Architecture (ISCA) 2023-conferentie in Orlando, Florida, haar paper, "MTIA: First Generation Silicon Targeting Meta's Recommendation Systems", het datacenter en AI-serversproject van het bedrijf. Er zijn 64 verwerkingselementen (PE) in het serverontwerp die de op maat gemaakte eigen accelerator van MRETA ondersteunen. Elke PE bevat twee processors: één scalair en één vector. Beide zijn Andes IP die META-ingenieurs sterk hebben aangepast, met behulp van Andes Custom Extensions (ACE) om een volledig unieke oplossing te produceren die is gericht op META's specifieke AI-computervereisten.

Het ontwerp valideerde de doeltreffendheid van RISC-V met Vector Extensions als een krachtige oplossing voor de computerbehoeften van AI-datacenters in een tijd waarin de vraag naar hardware voor datacenterverwerking explodeert. Volgens Toekomstige marktinzichten' rapport 'Data Center CPU Market Outlook (2023 to 2033)': de CPU-markt voor datacenters zal naar verwachting de komende jaren aanzienlijk groeien, aangedreven door de toenemende vraag naar cloud computing, big data-analyse en kunstmatige intelligentie (AI) . Belangrijke aanjagers van deze groei zijn onder meer de behoefte aan snellere gegevensverwerking, verhoogde efficiëntie en lagere kosten.

In 2021 ratificeerde RISC-V International, naast vectorextensies, nog eens 11 extensies. Figuur 1 illustreert de Andes-productroutekaart om deze uitbreidingen te ondersteunen. Op weg naar eind 2022 zijn de N25F-SE, 27-serie en 45-serie sindsdien geleverd, in 2023 heeft Andes zes nieuwe RISC-V-cores op de markt gebracht, zoals D25F-SE, D23, N225, NX45V, AX45MPV evenals AX65. De routekaart strekt zich uit van de energiezuinige en sterk beveiligde instapmodel RISC-V-processor AndesCore™ D23 tot de AX65, de eerste in de 60-serie, die in het vierde kwartaal van 2023 werd uitgebracht en nu naar ontwerpen van klanten wordt verzonden.

De AX65 is een 13-traps, 4-weg 64-bits buitengebruikstellingsprocessor met RVA 22-profiel (RVA22U64-profiel specificeert de ISA-functies die beschikbaar zijn voor uitvoeringsomgevingen in gebruikersmodus in 64-bits applicatieprocessors). Uitgerust met 13-traps pijplijn, 4-brede decodering, 8-brede out-of-order uitvoering, richt de serie zich op de Linux-applicatieprocessorsockets van computers, netwerken en high-end controllers.

De AX65 maakt multicore-clusters van één tot vier tot acht cores mogelijk. De prestaties zijn van wereldklasse en werken op een klokfrequentie van 2.4 gigahertz in een TSMC-proces van zeven nanometer. De prestaties van de spec-gehele getallen (Specint 2006) zijn 8.25 per gigahertz, en een SpecFp2006 is 10.2 per gigahertz, wat de bekendste SPEC CPU® 2006-prestaties zijn met een cache-ontwerp op twee niveaus. Daarna worden de AX66, AX63 en AX67 geleverd.

Een ander gebied waarin Andes aanzienlijk heeft geïnvesteerd, is de hoogwaardige RISC-V CPU IP voor auto's. Volgens The SHD Group zal de penetratie van RISC-V SoC’s in auto-ontwerpen in 21.4 naar verwachting 2030% bedragen. “RISC-V-marktrapport: toepassingsvoorspellingen in een heterogene wereld.” Andes heeft functionele, veiligheidsconforme producten ontwikkeld, waaronder de N25F-SE, 's werelds eerste volledig ISO 26262-compatibele RISC-V CPU IP; D25F-SE, die DSP-extensie-instructies ondersteunt; en de 45-SE-serie processors die voldoen aan het hoogste ASIL-niveau, zal de ASIL D. ACE-functie worden verbeterd om ondersteuning toe te voegen voor 45-serie processors.

Dankzij de vraag die Andes RISC-V-producten hebben ervaren, blijft het bedrijf winstgevend en blijft het een snelle groei kennen. Van 2021 tot 2023 vertoonde de omzet van Andes een groei van bijna 30%. Dit werd mogelijk gemaakt door meer dan 300 commerciële licentiehouders en meer dan 600 ondertekende licentieovereenkomsten met geografisch verspreide klanten in Taiwan, China, Korea, Japan, Europa en de VS. Het wereldwijde personeelsbestand van het bedrijf groeide in dezelfde periode met bijna 70%.

Conclusie

In een tijdperk dat wordt gekenmerkt door snelle technologische evolutie, loopt Andes Technology Corp. voorop op het gebied van innovatie op de RISC-V CPU IP-markt. Van de baanbrekende uitgifte van overzeese certificaten (DDR) tot de baanbrekende vooruitgang in de RISC-V-architectuur, Andes Technology blijft industriestandaarden herdefiniëren en de toekomst van computergebruik vormgeven. Terwijl de vraag naar efficiënte, krachtige computeroplossingen blijft stijgen, blijft Andes Technology zich inzetten voor het leveren van ongeëvenaarde RISC-V-oplossingen om transformatieve veranderingen in het mondiale technologielandschap te stimuleren.

Lees ook:

LIVE WEBINAR: RISC-V-instructiesetarchitectuur: verbetering van de rekenkracht

WEBINAR: Maak gebruik van gecertificeerde RISC-V IP om ASIL ISO 26262-kwaliteit autochips te maken

Deel dit bericht via:

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- PlatoData.Network Verticale generatieve AI. Versterk jezelf. Toegang hier.

- PlatoAiStream. Web3-intelligentie. Kennis versterkt. Toegang hier.

- PlatoESG. carbon, CleanTech, Energie, Milieu, Zonne, Afvalbeheer. Toegang hier.

- Plato Gezondheid. Intelligentie op het gebied van biotech en klinische proeven. Toegang hier.

- Bron: https://semiwiki.com/ip/343097-andes-technology-pioneering-the-future-of-risc-v-cpu-ip/