저전력 SoC에 대한 끊임없는 수요는 많은 시장에서 분명하게 나타납니다. AI 및 5G/6G 통신에 대한 높은 컴퓨팅 수요와 함께 최첨단 모바일, IoT, 웨어러블 장치를 예로 들 수 있습니다. 저전력 드라이버에는 배터리 수명, 열 관리 및 고성능 컴퓨팅 애플리케이션의 경우 전체 운영 비용이 포함됩니다. 저전력을 달성하기 위해 여러 가지 접근 방식을 사용할 수 있습니다. 많은 사람들의 공통점은 최적의 Foundation IP, 즉 임베디드 메모리와 로직 라이브러리가 필요하다는 것입니다. 이는 Synopsys가 상당한 투자를 하고 시장 리더십을 발휘하는 영역입니다. 현재 이용 가능한 옵션과 혜택을 이해하는 데 도움이 되는 두 가지 정보 간행물을 이용할 수 있습니다. Synopsys Foundation IP 메모리 컴파일러와 로직 라이브러리를 사용하면 극도의 저전력 달성이 가능해졌습니다.

제공되는 정보를 살펴보겠습니다.

기술 게시판

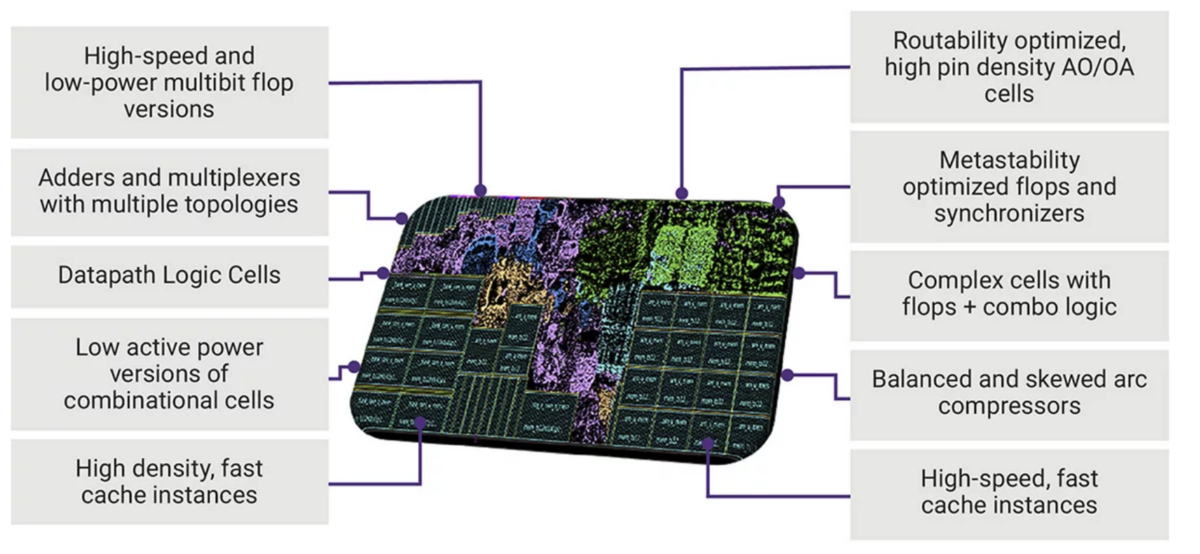

나는 시작한다 Synopsys Foundation IP를 사용하여 HPC 및 AI 애플리케이션용 PPA 최적화, 논리 라이브러리에 초점을 맞춘 기술 게시판입니다. 이 기사는 Synopsys의 도구 인식 Foundation IP 솔루션에 대한 세부 정보를 제공합니다. 최적화된 회로, 광범위한 작동 전압 범위 지원 및 고객별 최적화를 추가할 수 있는 유연성과 같은 주제가 논의됩니다. 또한 이 기사에서는 가능한 최대 성능 또는 최고의 전력 성능 균형을 달성하는 방법에 대한 관점도 제공합니다. 아래 그림에는 HPC 디자인 키트에서 사용할 수 있는 로직 라이브러리 회로가 요약되어 있습니다.

전력 개선이 어떻게 달성되는지에 대한 자세한 내용은 다양한 애플리케이션과 설계 전략 전반에 걸쳐 제공됩니다. 다루는 주제에는 넓은 작동 전압 범위에 걸친 동적 전압 스케일링, AI 최적화 및 애플리케이션별 가속기 블록 PPA, 네트워크 온 칩용 솔루션, 효율적인 SoC 구현을 위해 Synopsys HPC 설계 키트가 Synopsys EDA와 공동 최적화되는 방법이 포함됩니다.

이 기술 게시판은 풍부한 정보와 예제를 제공합니다. 당신은 할 수 있습니다 여기에서 이 정보에 액세스하세요.

백지

또한 다음과 같은 제목의 포괄적인 백서도 제공됩니다. 얼마나 낮은 수준으로 갈 수 있나요? 트랜지스터의 한계를 뛰어넘다. 이 작품은 임베디드 메모리와 로직 라이브러리를 모두 파헤칩니다. 극도로 낮은 전력을 달성하는 데 필요한 세부 사항을 살펴봅니다. 모바일, Bluetooth 및 IoT, 고성능 컴퓨팅, 자동차 및 암호화를 포함한 여러 응용 분야에 대해 논의합니다.

임베디드 메모리의 경우 보조 기술 및 공급 전압 분할을 포함한 여러 가지 접근 방식이 논의됩니다. 저전압에서 고밀도 저전력 메모리 작동을 제공하려면 기술과 메모리 보조 회로 설계 간의 세심한 공동 최적화가 필요하다는 지적이 있습니다. 몇 가지 향상된 지원 기술이 검토됩니다. 전력 범위가 10%에서 37%로 향상되었습니다.

기억의 신뢰성에 대해서도 논의됩니다. 이 기사는 전압이 감소함에 따라 SRAM 셀이 저하되기 시작한다고 설명합니다. 이러한 성능 저하로 인해 읽기 오류, 비트셀이 뒤집히지 않음, SER이 뚜렷해지고 감지 실패, 제어 신호 이탈, BL 신호 약화 등 여러 문제가 발생할 수 있습니다. 따라서 최첨단 저전력 애플리케이션에 필요한 더 낮은 극저전압을 지원하려면 보조 기술이 필요합니다.

여기서 Synopsys가 취하는 접근 방식은 상당한 차이를 만듭니다. 신뢰성을 향상시키는 전략과 노화를 시뮬레이션하는 방법이 논의됩니다. 자세한 내용은 직접 읽어보시기 바랍니다. 링크가 곧 제공될 예정입니다. 데이터는 5~10년의 수명이 추가된 놀라운 결과를 보여줍니다.

0.4V 이하에서 깊은 저전압 작동을 가능하게 하는 전략과 함께 로직 라이브러리도 논의됩니다. 아키텍처 최적화도 검토됩니다. 동적 전력과 누설 전력을 모두 줄이기 위해 표준 셀 아키텍처 기술을 사용할 수 있습니다. 예를 들어 Synopsys는 극저전압 작동을 위한 최적의 토폴로지를 위해 스택 기반 대 스테이지 기반 아키텍처 기술을 사용합니다. 이 접근 방식의 전략이 제시됩니다.

특성화 최적화도 다룹니다. 특성화의 중요한 부분 중 하나는 OCV(On Chip Variation)라고 하는 SoC 전반의 프로세스 변화를 모델링하는 것입니다. 정확성을 높이고 성능과 전력을 최적화하기 위한 기계 학습을 포함하여 여러 가지 고급 기술이 여기에 사용됩니다.

백서는 깊은 저전압 작동을 달성하기 위해 SoC 수준에서 모든 것을 통합하는 방법에 대한 개요로 마무리됩니다. 동적 전압 및 주파수 스케일링(DVFS) 기술과 라이트 슬립, 딥 슬립, 완전 셧다운 및 POFF(주변 꺼짐) 모드와 같은 다양한 셧다운 전략과 함께 전압 감소에 대해 논의합니다.

이 백서에서는 다양한 전력 최적화 주제를 아주 자세하게 다루고 있습니다. 나는 그것을 강력히 추천합니다. 당신은 할 수 있습니다 여기에서 사본을 받으십시오. Synopsys Foundation IP 메모리 컴파일러와 로직 라이브러리를 사용하면 극도의 저전력 달성이 가능해집니다.

다음을 통해이 게시물 공유 :

- SEO 기반 콘텐츠 및 PR 배포. 오늘 증폭하십시오.

- PlatoData.Network 수직 생성 Ai. 자신에게 권한을 부여하십시오. 여기에서 액세스하십시오.

- PlatoAiStream. 웹3 인텔리전스. 지식 증폭. 여기에서 액세스하십시오.

- 플라톤ESG. 탄소, 클린테크, 에너지, 환경, 태양광, 폐기물 관리. 여기에서 액세스하십시오.

- PlatoHealth. 생명 공학 및 임상 시험 인텔리전스. 여기에서 액세스하십시오.

- 출처: https://semiwiki.com/ip/341966-achieving-extreme-low-power-with-synopsys-foundation-ip-memory-compilers-and-logic-libraries/