끊임없이 증가하는 데이터 속도를 끊임없이 추구하는 가운데, 1.6Tbps(초당 테라비트) 시대가 다가오고 있으며 데이터 센터 내에서 전례 없는 수준의 연결성과 대역폭을 약속합니다. 데이터 집약적인 애플리케이션이 급증하고 실시간 처리에 대한 수요가 증가함에 따라 강력하고 효율적인 통신 인프라의 필요성이 중요해졌습니다. 이 인프라의 중심에는 고속, 낮은 대기 시간 및 전력 효율적인 기능을 결합하여 데이터 전송에 혁명을 일으킬 준비가 된 전기 광학 상호 연결이 있습니다. 224G 직렬 링크의 채택은 엔드 투 엔드 1.6Tbps 트래픽 용량을 달성하는 데 중요한 요소로 등장합니다. 이러한 고속 직렬 링크는 데이터 전송의 백본 역할을 하여 네트워크 내 다양한 구성 요소 간의 원활한 통신을 촉진합니다. 초고속 데이터 전송률과 대역폭 수요를 처리하는 능력은 차세대 통신 시스템을 실현하는 데 없어서는 안 될 요소입니다. 모든 주요 기술 발전과 마찬가지로 극복해야 할 본질적인 과제가 있습니다. 광 채널과 광 엔진 모두 비선형 동작을 도입합니다. 기존의 시뮬레이션 지원 설계 방법은 선형 채널을 가정하고 전기 회로 언어 및 시뮬레이터를 사용하여 광학 엔진을 모델링하는 경우가 많으므로 상호 연결 성능을 지나치게 낙관적으로 평가하게 됩니다.

최근 개최된 DesignCon 2024 컨퍼런스에서 Synopsys는 기본 전기 및 광학 신호 표현을 사용한 전기-광 공동 시뮬레이션 연구 결과를 발표했습니다. 이 연구의 하이라이트는 활용된 시스템 설계 방법론이 선형 및 비선형 손상, 기술 불가지론, 데이터 속도 및 변조 형식을 모두 설명한다는 것입니다. XNUMXD덴탈의 “224Gbps 직렬 링크의 시스템 설계 방법론, 시뮬레이션 및 실리콘 검증” 논문 제출 DesignCon 2024 최우수 논문상을 수상했습니다.

다음은 Synopsys가 DesignCon에 제출한 두 편의 논문, 즉 "Direct-Drive 광학 엔진을 갖춘 고속 112G/224G SerDes에 대한 성능 평가"와 "224Gbps 직렬 링크의 시스템 설계 방법론, 시뮬레이션 및 실리콘 검증"에서 발췌한 내용입니다. ”

1.6T 시대의 순방향 오류 정정

FEC(순방향 오류 정정) 메커니즘은 특히 1.6Tbps 트래픽 환경에서 고속 링크를 통한 데이터 전송의 신뢰성을 향상시키는 데 중추적인 역할을 합니다. FEC는 오류를 방지하고 데이터 무결성을 보장하는 데 도움이 되지만 이를 구현하면 전력 소비 및 대기 시간과 같은 추가적인 고려 사항이 발생합니다. 1.6T 시대에 효율적인 통신 시스템을 설계하려면 비트 오류율(BER), 전력 효율성 및 대기 시간 간의 올바른 균형을 유지하는 것이 필수적입니다.

전기광학 인터페이스의 출현

1.6Tbps 시대의 진화하는 요구를 충족하기 위해 전기광학 인터페이스는 혁신적인 역할을 할 준비가 되어 있습니다. 이러한 인터페이스는 광학 기술의 장점을 활용하여 고속, 짧은 대기 시간 및 전력 효율적인 통신 솔루션을 제공합니다. CPO(Co-packaged Optics) 및 D2D(Die-to-Die) 상호 연결과 같은 기술은 광학 구성 요소를 기존 데이터 센터 아키텍처에 원활하게 통합하여 효율성과 성능의 새로운 시대를 여는 유망한 방법을 제공합니다.

종단 간 링크의 손상 탐색

그러나 엔드투엔드 224G 링크를 배포하는 데 어려움이 없는 것은 아닙니다. 전기 회로 언어와 시뮬레이터를 사용하여 광 상호 연결을 시뮬레이션하는 기존 접근 방식은 어떤 경우에는 효과적이지만 몇 가지 장단점이 있습니다. 잡음, 지터, 왜곡 및 누화와 같은 장애는 신호 품질을 크게 저하시키고 전체 성능에 영향을 줄 수 있습니다. 이러한 문제를 해결하려면 장애를 모델링하고 완화하는 데 세심한 주의를 기울여야 하며, 광학 및 전기 광학 인터페이스에 내재된 비선형 효과에 직면하여 통신 인프라의 견고성과 신뢰성을 보장해야 합니다.

정확한 시스템 모델링의 역할

정확한 시스템 모델링은 전기광학 상호 연결의 복잡성을 탐색하고 광 전송에 내재된 비선형 효과에 대응하는 데 매우 중요합니다. 다양한 구성 요소와 그 상호 작용을 꼼꼼하게 시뮬레이션함으로써 설계자는 시스템 동작에 대한 귀중한 통찰력을 얻고 잠재적인 최적화 영역을 식별할 수 있습니다. 또한 실리콘 구현과의 상관 관계를 통해 시뮬레이션 결과가 실제 성능과 밀접하게 일치하므로 정보에 입각한 의사 결정과 효율적인 설계 반복이 가능합니다.

시스템 시뮬레이션과 실리콘 상관 관계 비교

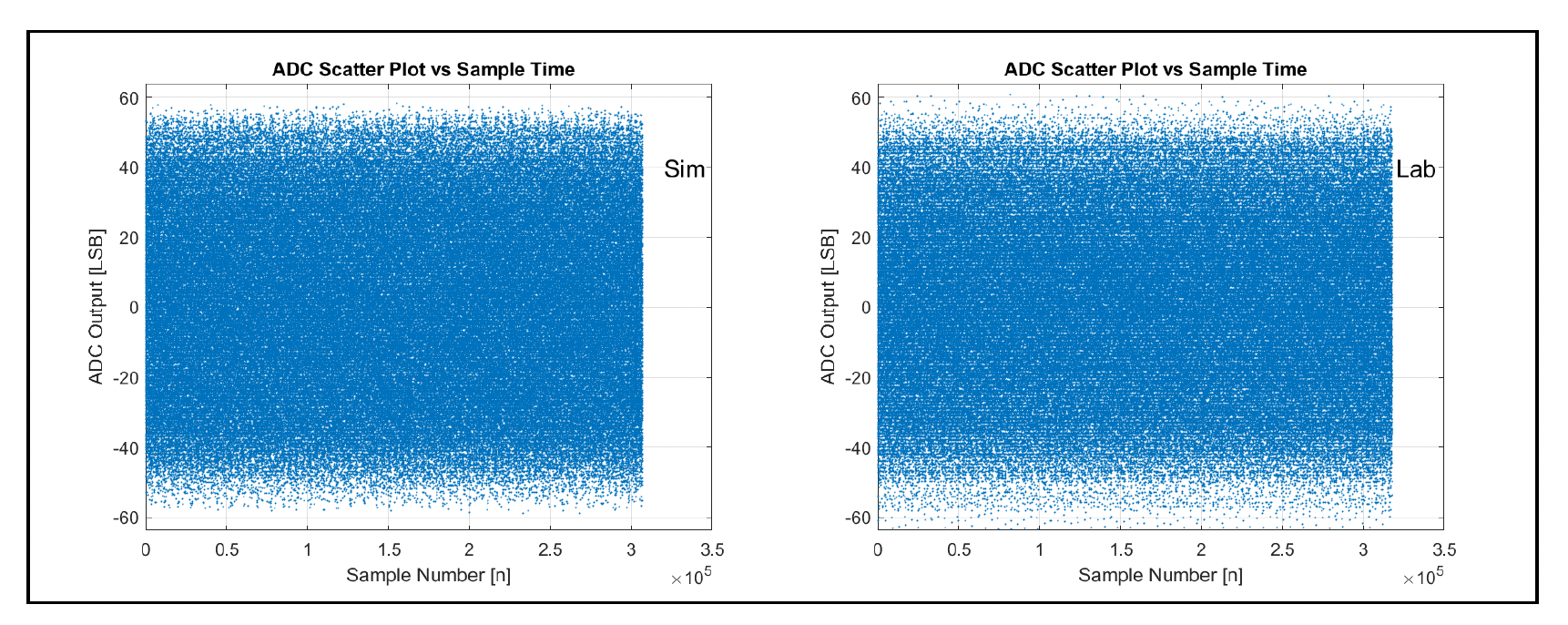

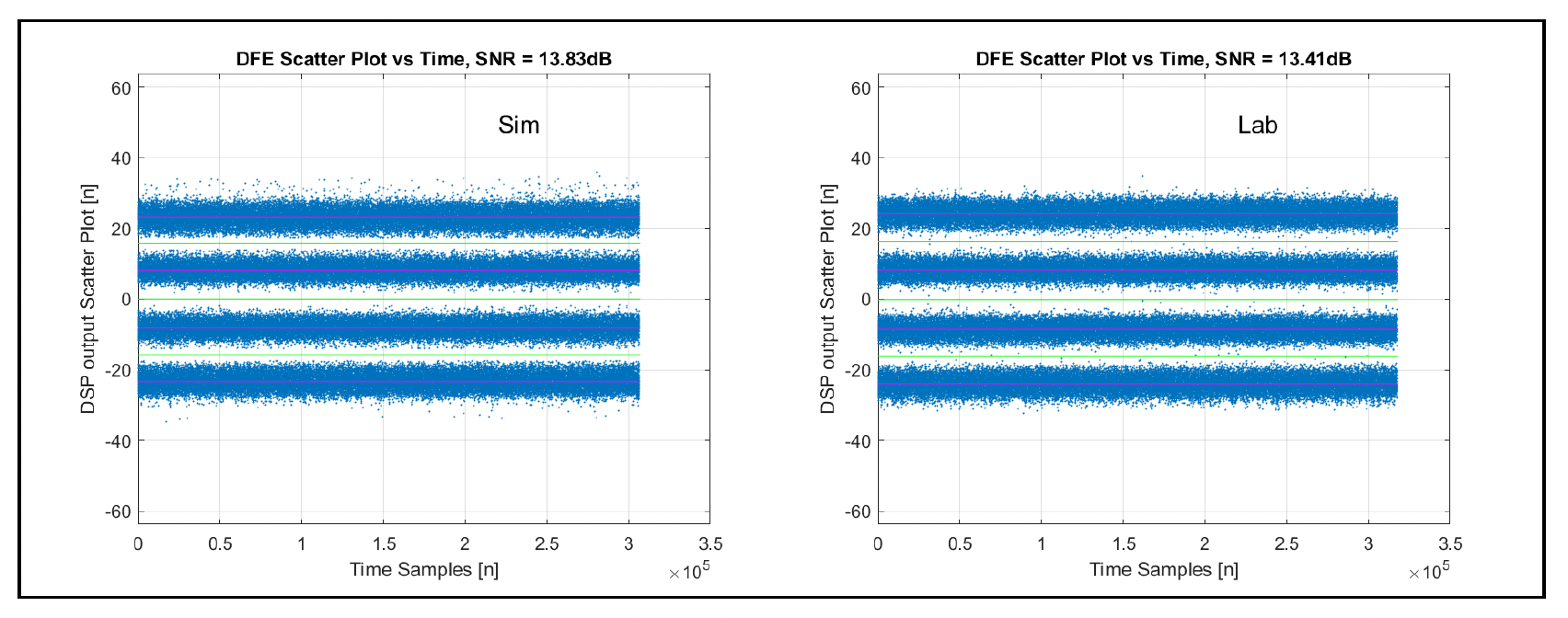

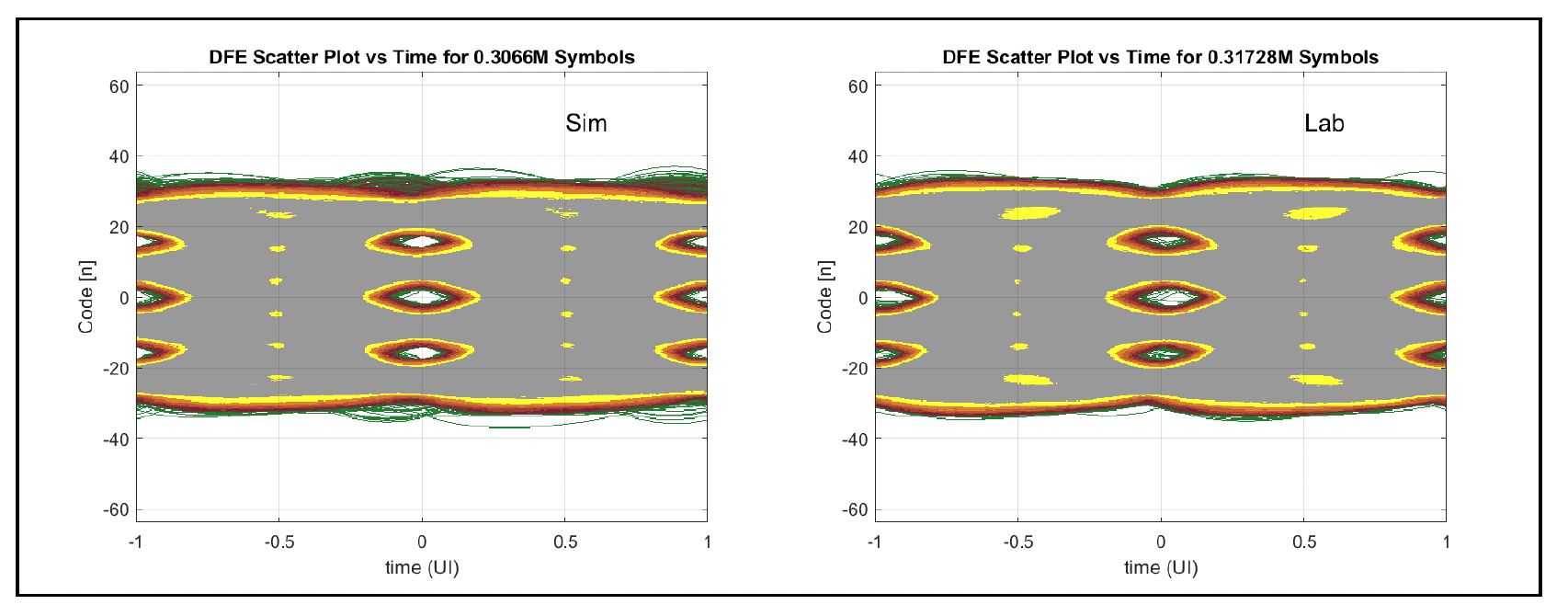

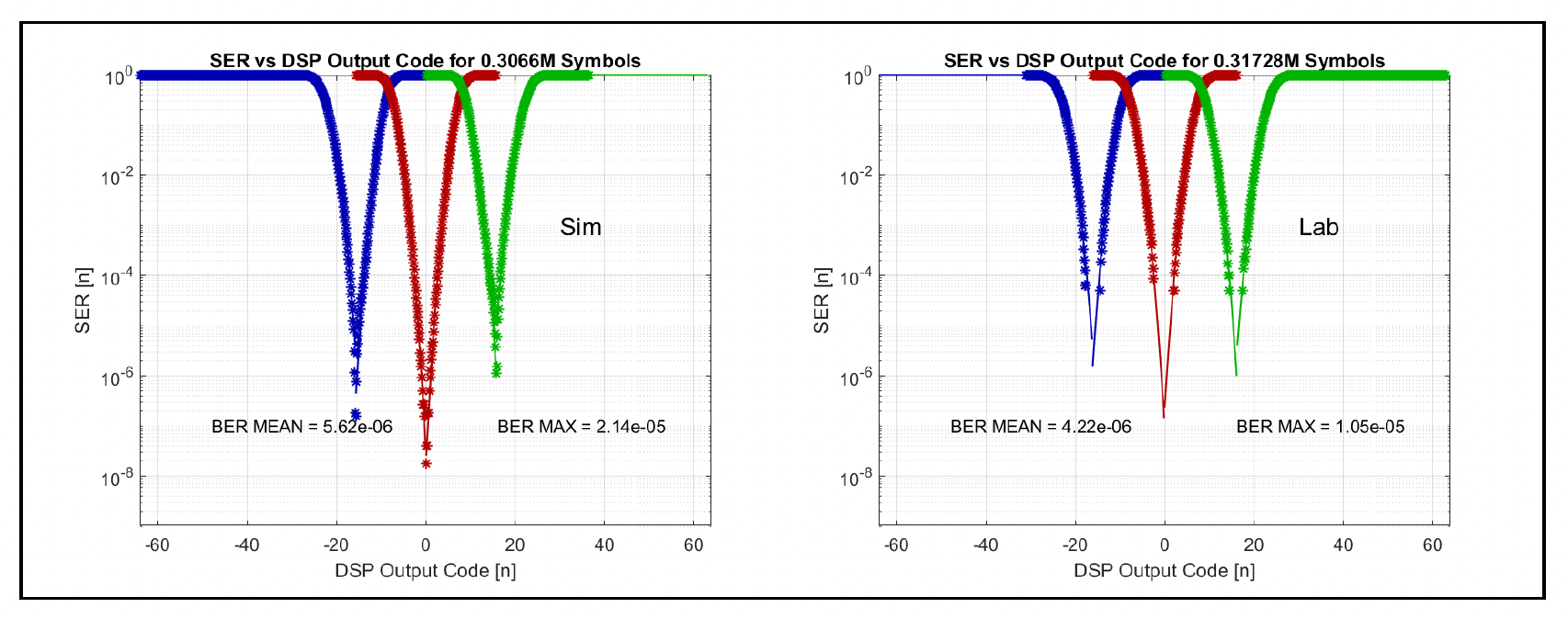

Synopsys의 전기광학 공동 시뮬레이션 연구에서 시스템 시뮬레이션을 실리콘과 연관시키는 프로세스에는 실험실에서 성능 특성화를 위한 세부 설정이 포함되었습니다. 이 설정에는 BERT, 케이블, 테스트 보드 도터 카드, Ironwood 소켓에 있는 테스트 중인 장치를 포함한 다양한 구성 요소가 포함되었습니다. 시스템 모델에서 고려된 s-파라미터에는 Wildriver, taconic fastrise 12층 도터 카드 및 테스트칩 패키지의 응답이 포함되었습니다. 실리콘 결과와 시스템 시뮬레이션 출력 간의 비교는 둘 사이의 상관관계를 보여주었습니다. 전반적으로, 연구 결과는 실리콘 동작을 포착하는 데 있어 시스템 시뮬레이션 모델의 효율성을 강조하고 시스템 성능 및 최적화에 대한 귀중한 통찰력을 제공했습니다.

아래 4개의 차트는 시뮬레이션과 실리콘을 비교했을 때 PAMXNUMX 수준, EYE 개방 및 BER 성능의 유사성을 나타냅니다.

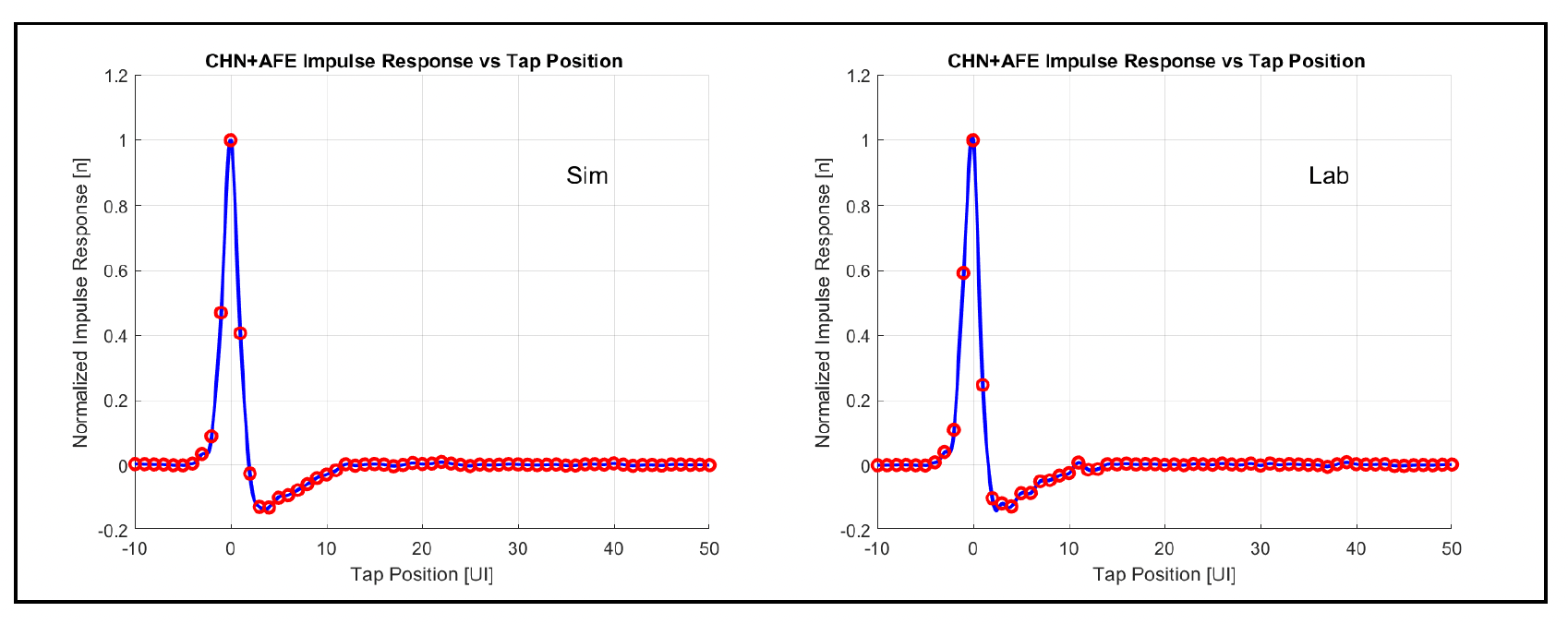

아래의 임펄스 응답 비교는 시뮬레이션과 실리콘 간의 잠금 지점에 약간의 차이가 있지만 모양에서는 전체적인 상관 관계를 보여줍니다.

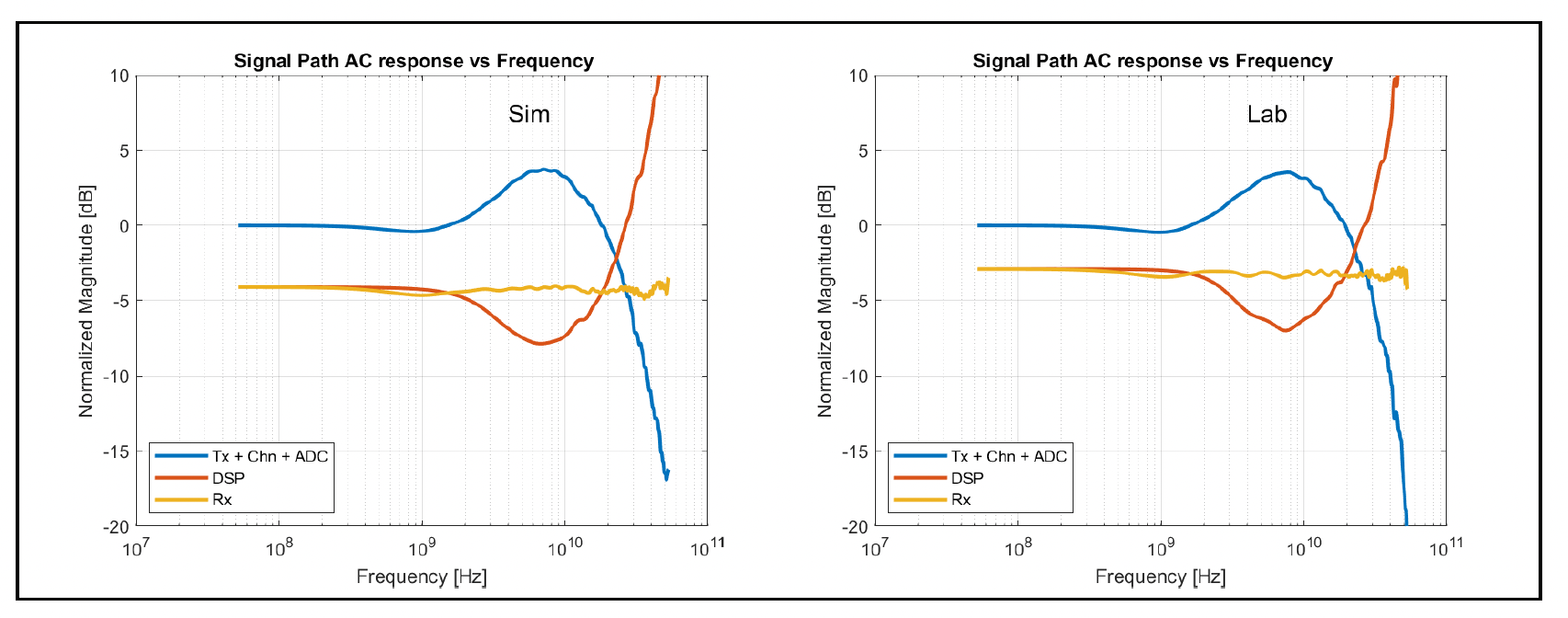

아래 차트는 DSP가 ISI를 보상하고 전체 채널 응답을 평탄화하는 수신기의 이퀄라이제이션 기능을 보여줍니다.

아래 차트는 시뮬레이션 및 실리콘 판독값에서 FFE 및 DFE 계수를 캡처하며, 이는 AFE 전달 함수 및 CDR 잠금 지점의 변화로 인한 일부 차이점을 나타냅니다.

요약

데이터 센터가 1.6Tbps 시대로 전환함에 따라 전기광학 상호 연결의 통합은 전례 없는 수준의 연결성, 대역폭 및 효율성을 실현하는 열쇠를 쥐고 있습니다. 세심한 시스템 모델링, 시뮬레이션 및 실리콘 구현과의 상관관계를 통해 설계자는 이러한 기술의 잠재력을 최대한 활용하여 데이터 센터 인프라의 혁신과 성능의 새로운 시대를 열 수 있습니다. 고속 직렬 링크, 고급 FEC 메커니즘 및 새로운 전기 광학 인터페이스의 융합을 통해 데이터 센터는 현대 컴퓨팅 및 네트워킹 애플리케이션의 증가하는 요구를 충족하고 전례 없는 연결성과 효율성을 위한 길을 열었습니다.

DesignCon에서 발표된 전체 논문에 대한 자세한 내용과 액세스를 원하시면 Synopsys에 문의하시기 바랍니다.

Synopsys 고속 이더넷 솔루션에 대한 자세한 내용을 보려면 다음을 방문하십시오. www.synopsys.com/ethernet

또한 읽기 :

Synopsys가 실제로 Ansys를 인수한 이유는 무엇입니까?

복잡한 SoC 설계에 대한 IP의 자동화된 제약 조건 승격 방법론

다음을 통해이 게시물 공유 :

- SEO 기반 콘텐츠 및 PR 배포. 오늘 증폭하십시오.

- PlatoData.Network 수직 생성 Ai. 자신에게 권한을 부여하십시오. 여기에서 액세스하십시오.

- PlatoAiStream. 웹3 인텔리전스. 지식 증폭. 여기에서 액세스하십시오.

- 플라톤ESG. 탄소, 클린테크, 에너지, 환경, 태양광, 폐기물 관리. 여기에서 액세스하십시오.

- PlatoHealth. 생명 공학 및 임상 시험 인텔리전스. 여기에서 액세스하십시오.

- 출처: https://semiwiki.com/eda/342124-navigating-the-1-6tbps-era-electro-optical-interconnects-and-224g-links/