시 고맥텍 지난 주 사우스 캐롤라이나에서 열린 컨퍼런스 저는 Mirabilis Design Inc.의 창립자이자 기술 부사장인 Deepak Shankar와 Zoom 통화를 통해 질문을 하고 라이브 데모를 보았습니다. 비주얼심 – 전자 제품 및 SoC 개발을 위한 모델링, 시뮬레이션, 탐색 및 협업 플랫폼입니다. VisualSim이 특별한 이유는 바로 사용할 수 있는 약 500개의 고급 IP 블록(35개 ARM 프로세서, 약 100개 프로세서, 30개 이상의 상호 연결 포함)이 번들로 제공된다는 점입니다. VisualSim 사용자는 이러한 IP 블록을 시각적으로 신속하게 연결하여 네트워크가 포함된 시스템을 만듭니다. 자동차 설계자는 VisualSim을 사용하여 5G 통신, 이더넷, SDA 및 OTA 업데이트를 포함한 전체 네트워크를 모델링할 수 있습니다.

상위 수준 모델을 사용하면 RTL 코드로 구현을 시작하기도 전에 가장 빠른 아키텍처 탐색과 아키텍처 절충이 가능합니다. 버스, 메모리, 심지어 캐시와 같은 복잡한 활동을 모델링하여 엔드투엔드 지연 및 대기 시간과 같은 항목을 측정할 수 있습니다. 엔지니어는 캐시 적중/실패 비율과 L2 캐시에 대한 요청에 어떤 일이 발생하는지 측정할 수 있습니다. AXI, CHI, CMN600, Arteris NOC, UCIe 등 널리 사용되는 모든 네트워크 프로토콜이 모델링되었습니다.

이 모델링 접근 방식을 통해 건축가는 SoC, 전체 항공기 또는 자동차 시스템을 모델링한 다음 성능 측정을 시작하여 요구 사항을 충족하는지 확인할 수 있습니다. VisualSim은 아날로그, 소프트웨어, 전력 시스템, 디지털 및 네트워킹을 단일 모델로 통합할 수 있는 다중 도메인 시뮬레이터입니다.

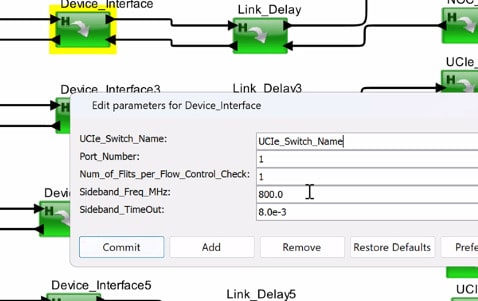

라이브 데모를 위해 Deepak은 UCIe를 사용하여 모두 함께 연결된 DSP, GPU, AI 프로세서 및 CPU에 대한 별도의 칩렛이 있는 칩렛 기반 디자인을 보여줬고, 각 IP 블록은 사용자 정의 및 탐색이 가능하도록 매개변수화되었습니다.

UCIe 블록을 밀어 넣으면 UCIe 스위치라는 IP가 있으며 사용자는 이 블록을 모두 높은 수준에서 5개의 매개변수로 사용자 정의할 수 있습니다.

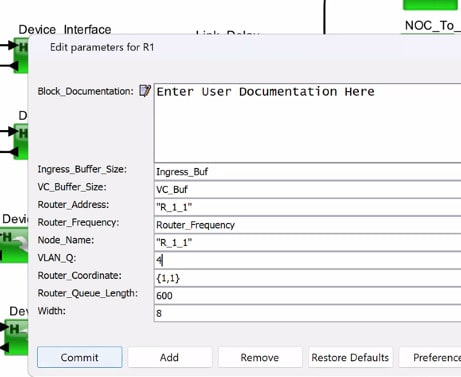

라우터 IP 블록에는 사용자 정의를 위한 10개의 매개변수가 있습니다.

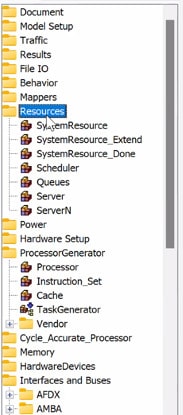

각 IP 블록을 찾으려면 라이브러리의 각 IP 제품군과 함께 GUI 왼쪽에 스크롤 가능한 목록이 있습니다. 몇 초 안에 IP를 찾아보고 선택하고 사용자 정의를 시작할 수 있습니다.

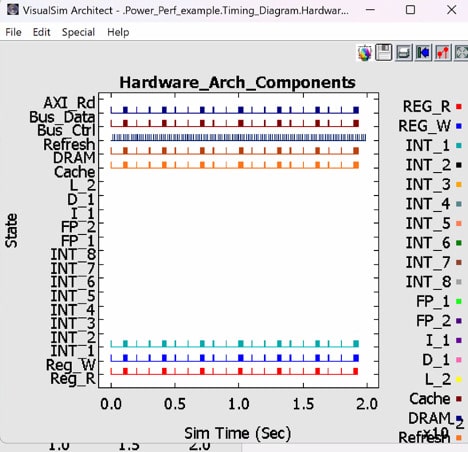

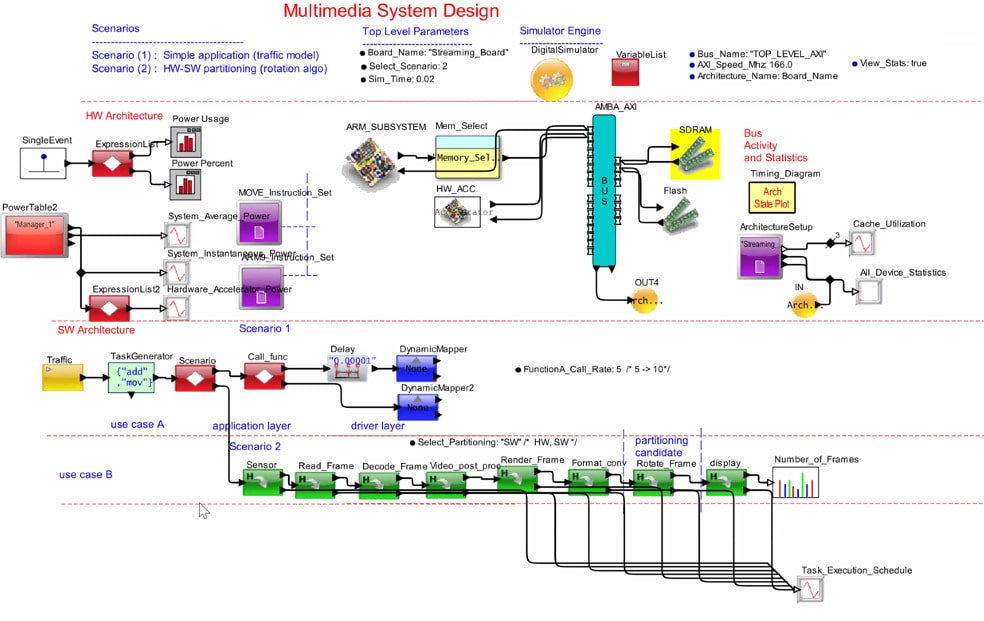

VisualSim에서는 높은 수준을 유지하면서 데이터 흐름의 각 IP를 연결합니다. 다음 라이브 데모는 멀티미디어 시스템 설계에 대한 것이었고, 20ms를 시뮬레이션하는 데 랩톱에서 실행되는 벽 시간은 약 15초가 걸렸습니다. 시뮬레이션이 실행되는 동안 시스템 성능을 순간 전력으로 확인하고 파이프라인 활용도, 캐시 활용도, 메모리 사용량을 측정하고 타이밍 다이어그램도 볼 수 있습니다. 이 실시간 시뮬레이션은 7.5만 개의 이벤트를 유발했으며 고객은 전체 SoC가 포함된 이 모델을 2주 이내에 구축했습니다.

Deepak이 언급한 또 다른 고객 사례에는 45명의 마스터가 포함되어 있으며 약 4주 만에 완료되었으며 완전한 테스트를 거쳤습니다.

IP 블록 내부를 살펴보고 통과/실패와 같은 지표를 분석한 다음 실패한 이유를 이해할 수 있습니다. 오류를 일으킨 버퍼 오버플로를 찾는 등 데이터를 보다 효율적으로 분석하는 데 도움이 되는 AI 엔진도 있습니다. 모델이 실행되는 동안 시스템 성능을 측정하고 아키텍처 병목 현상을 식별하는 데 도움이 되는 분석이 캡처됩니다.

VisualSim은 1년에 두 번 업데이트되며, 새로운 IP 블록이 추가될 때를 위한 패치 업데이트가 있습니다. 설계자는 대기 시간 제한 및 버퍼 점유와 같은 지표를 사용하여 Excel 파일에서 요구 사항을 정의합니다.

VisualSim 사용자는 바이트, 속도 범위 및 기본 값 측면에서 페이로드 크기 범위를 정의할 수 있습니다. 시스템 모델을 여러 조합으로 탐색하여 최상의 매개변수 세트를 찾을 수 있습니다. 시뮬레이터는 최소값, 최대값 및 기본 값을 탐색하는 방법까지 이해합니다. 탐색할 시스템 매개변수를 정의할 수 있습니다. 멀티미디어 시스템 데모가 다음에 보여졌고 실시간으로 시뮬레이션되었습니다.

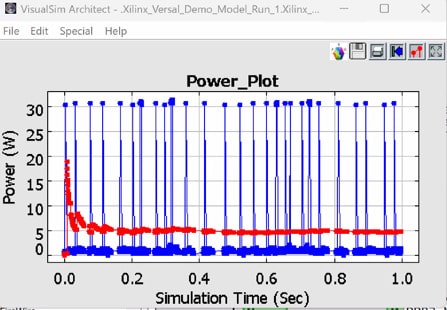

FPGA 블록의 경우 공급업체와 부품 번호를 선택하면 시뮬레이션이 실행된 후 각 작업의 대기 시간과 NOC의 채널 통계를 볼 수 있습니다. Xilinx Versal 부품을 사용할 때 1초 작동에 대한 전력 플롯이 표시되었습니다.

모든 라이브 데모는 Windows 노트북에서 실행되었습니다. 기타 지원되는 OS는 Unix, Mac입니다. VisualSim을 실행하려면 모델이 높은 수준이므로 최소한의 HW 인프라가 필요합니다.

VisualSim 사용자는 안테나, 트랜시버, 베이스밴드가 있는 FPGA 및 이더넷 인터페이스를 갖춘 완전한 통신 시스템과 같이 신속하게 시작할 수 있도록 사전 구축된 500개 이상의 예제를 받습니다. VisualSim을 사용하는 시스템 설계자는 RTL 설계자와 같은 모든 하위 수준 전문가와 협력할 수 있습니다.

다음과 같이 시스템 수준의 균형을 모델링하고 평가할 수 있습니다.

- 64-QAM에서 QPSK 변조로 변경

- 빠른 프로세서에서 느린 프로세서로

- 이더넷 사양 변경

VisualSim으로 시작하여 모델링, 구현, 측정을 수행하면 RTL 구현 결과와 비교하여 95% 정확도를 기대할 수 있습니다. 높은 수준의 모델을 사용하면 구현 또는 통합 전에 성능 문제를 제거할 수 있습니다. 실제로 전체 시스템 모델에는 코딩이 필요하지 않습니다.

Mirabilis는 지금까지 전 세계적으로 65개의 고객을 보유하고 있으며 약 250개의 프로젝트가 완료되었습니다. 잘 알려진 클라이언트로는 NASA, Samsung, Qualcomm, Broadcom, GM, Boeing, HP, Imagination, Raytheon, AMD, Northrup Grumman이 있습니다.

요약

예전에는 시스템 디자이너가 레스토랑에서 식사를 하면서 냅킨에 자신의 아이디어를 그린 다음 직장으로 돌아가 Excel 스프레드시트를 난해한 방정식으로 엮어 모델을 만들었습니다. 오늘은 새로운 선택이 생겼습니다. 비주얼심 Mirabilis에서 시도해 보세요. 이제 자세한 구현 세부 사항을 살펴보기 전에 실제 시뮬레이션을 실행하면서 아키텍처 균형을 맞추는 동시에 단 몇 주 만에 전체 시스템을 모델링할 수 있습니다.

관련 블로그

다음을 통해이 게시물 공유 :

- SEO 기반 콘텐츠 및 PR 배포. 오늘 증폭하십시오.

- PlatoData.Network 수직 생성 Ai. 자신에게 권한을 부여하십시오. 여기에서 액세스하십시오.

- PlatoAiStream. 웹3 인텔리전스. 지식 증폭. 여기에서 액세스하십시오.

- 플라톤ESG. 탄소, 클린테크, 에너지, 환경, 태양광, 폐기물 관리. 여기에서 액세스하십시오.

- PlatoHealth. 생명 공학 및 임상 시험 인텔리전스. 여기에서 액세스하십시오.

- 출처: https://semiwiki.com/ip/343387-a-modeling-simulation-exploration-and-collaborative-platform-to-develop-electronics-and-socs/