칩렛은 자동차 시장에서 다시 주목을 받고 있습니다. 자동차 시장에서는 전기화가 증가하고 경쟁이 치열해 기업이 설계 및 생산 일정을 가속화해야 합니다.

전기화는 매우 짧은 시장 기회와 끊임없이 변화하는 요구 사항에 직면하여 경쟁력을 유지하기 위해 고군분투하고 있는 가장 크고 잘 알려진 일부 자동차 제조업체에 불을 지폈습니다. 자동차 제조업체가 일반적으로 5~7년의 설계 주기를 사용했던 과거와 달리, 오늘날 자동차의 최신 기술은 몇 년 이내에 출시된 것으로 간주될 수 있습니다. 그리고 그들이 따라잡을 수 없다면, 소프트웨어 업데이트만큼 빠르게 기능을 업데이트하거나 변경할 수 있는 능력을 갖춘 값싼 차량을 생산하는 완전히 새로운 스타트업이 있습니다.

그러나 소프트웨어에는 속도, 보안 및 신뢰성의 한계가 있으며, 하드웨어를 맞춤화할 수 있는 기능은 현재 많은 자동차 제조업체가 노력하고 있는 부분입니다. 이것이 바로 칩렛이 적합한 곳이며, 이제 초점은 대규모 생태계 전반에 걸쳐 이를 플러그 앤 플레이 시장으로 만들기 위해 충분한 상호 운용성을 구축하는 방법에 있습니다. 자동차 칩렛 상호 운용성을 가능하게 하는 주요 요소에는 표준화, 상호 연결 기술, 통신 프로토콜, 전력 및 열 관리, 보안, 테스트 및 생태계 협업이 포함됩니다.

보드 수준의 비자동차 애플리케이션과 유사하게 많은 설계 노력이 다이 투 다이 접근 방식에 초점을 맞추고 있으며, 이로 인해 수많은 새로운 설계 고려 사항과 절충점이 발생합니다. 칩 수준에서 다양한 프로세서, 칩, 메모리 및 I/O 간의 상호 연결은 설계 성능 요구 사항의 증가로 인해 더욱 복잡해지고 있으며, 이로 인해 수많은 표준 활동이 촉발되고 있습니다. 다양한 목적을 달성하기 위해 다양한 상호 연결 및 인터페이스 유형이 제안되었습니다. 칩렛 프로세서, 메모리, I/O 등 전용 기능을 위한 기술이 칩 설계에 대한 접근 방식을 바꾸고 있습니다.

Siemens EDA의 가상 및 하이브리드 시스템 담당 부사장인 David Fritz는 “자동차 OEM은 자신의 운명을 제어하려면 자체 SoC를 제어해야 한다는 사실을 깨닫고 있습니다. “그러나 그들은 1982년 대학에 입학한 이후 EDA가 얼마나 발전했는지 이해하지 못합니다. 또한 그들은 마스크 세트 비용이 100억 달러에 달하는 최신 프로세스 노드로 가야 한다고 믿습니다. 그들은 그럴 여유가 없습니다. 또한 인재 풀이 상당히 작기 때문에 인재에 접근할 수 없습니다. 이 모든 것을 통해 OEM은 자신의 운명을 통제하려면 다른 사람이 개발한 기술이 필요하다는 사실을 깨닫게 되지만, 이를 결합할 수는 있지만 고유하고 차별화된 제품을 만드는 데 필요하며 적어도 일부는 미래에도 사용할 수 있다고 확신합니다. 모델년. 그러면 경제적으로 실행 가능해집니다. 청구서에 맞는 유일한 것은 칩렛입니다.”

Chiplet은 특정 기능에 맞게 최적화될 수 있으며, 이를 통해 자동차 제조업체는 여러 차량 설계에서 입증된 기술을 통해 신뢰성, 안전성, 보안 요구 사항을 충족할 수 있습니다. 또한 출시 기간을 단축하고 궁극적으로 다양한 기능의 비용을 절감할 수 있습니다.

칩에 대한 수요는 지난 49.8년 동안 증가해 왔습니다. Allied Market Research에 따르면 전 세계 자동차 칩 수요는 2021년 121.3억 달러에서 2031년 XNUMX억 달러로 증가할 것입니다. 이러한 성장은 더욱 많은 자동차 칩 혁신과 투자를 유치할 것이며 칩렛은 큰 수혜자가 될 것으로 예상됩니다.

그러나 칩렛 시장은 성숙하는 데 시간이 걸리며 단계적으로 출시될 가능성이 높습니다. 처음에 공급업체는 다양한 종류의 독점 다이를 제공합니다. 그런 다음 파트너는 이미 일부 공급업체에서 발생한 것처럼 서로를 지원하기 위한 칩렛을 공급하기 위해 협력할 것입니다. 최종 단계는 UCIe 또는 기타 상호 연결 방식이 지원하는 보편적으로 상호 운용 가능한 칩렛이 될 것입니다.

마지막 단계에 도달하는 것이 가장 어려울 것이며 상당한 변화가 필요할 것입니다. 상호 운용성을 보장하려면 하드웨어 및 소프트웨어 개발자, 파운드리, OSAT, 재료 및 장비 공급업체를 포함하여 자동차 생태계와 공급망의 충분한 부분이 함께 모여야 합니다.

모멘텀이 형성되고 있다

긍정적인 측면에서는 이 모든 것이 처음부터 시작되는 것은 아닙니다. 보드 수준에서 모듈과 하위 시스템은 항상 온보드 칩-칩 인터페이스를 사용해 왔으며 앞으로도 계속 사용할 것입니다. Cadence, Diode, Microchip, NXP, Renesas, Rambus, Infineon, Arm 및 Synopsys를 포함한 다양한 칩 및 IP 제공업체는 기성 인터페이스 칩 또는 IP를 제공하여 인터페이스 실리콘을 생성합니다.

UCIe(Universal Chiplet Interconnect Express) 컨소시엄 다이투다이 개방형 상호 연결 표준을 뒷받침하는 원동력입니다. 이 그룹은 1.1년 2023월에 최신 UCIe XNUMX 사양을 출시했습니다. 이사회 구성원으로는 Alibaba, AMD, Arm, ASE, Google Cloud, Intel, Meta, Microsoft, NVIDIA, Qualcomm, Samsung 등이 있습니다. 업계 파트너들은 폭넓은 지지를 보이고 있습니다. AIB와 BoW(Bunch of Wires)도 제안되었습니다. 또한 Arm은 최근 칩렛용 프로토콜을 표준화하기 위해 업데이트된 AMBA 사양과 함께 자체 칩렛 시스템 아키텍처를 출시했습니다.

Cadence의 디자인 IP 부문 수석 제품 마케팅 그룹 이사인 Arif Khan은 "필요에 따라 칩렛이 이미 등장했습니다."라고 말했습니다. “프로세서와 SoC 크기가 증가함에 따라 레티클 한계와 규모의 불경제에 직면하고 있습니다. 공정 기술 발전으로 인한 점진적인 이득은 트랜지스터 및 설계당 비용 상승보다 낮습니다. 패키징 기술(2.5D/3D)의 발전과 UCIe와 같은 다이-투-다이 수준의 인터페이스 표준화는 칩렛 개발을 촉진할 것입니다.”

오늘날 사용되는 거의 모든 칩렛은 Intel, AMD, Marvell과 같은 대형 칩 제조업체가 자체 개발한 것입니다. 왜냐하면 칩렛의 특성과 동작을 엄격하게 제어할 수 있기 때문입니다. 그러나 이 시장을 더 많은 플레이어에게 개방하기 위한 작업이 모든 수준에서 진행 중입니다. 그런 일이 발생하면 소규모 기업은 지금까지 주목을 받는 선구자들이 달성한 성과를 활용하고 이러한 개발을 중심으로 혁신을 시작할 수 있습니다.

Arteris의 전략 마케팅 수석 이사인 Guillaume Boillet는 "우리 중 많은 사람들은 기성품의 상호 운용 가능한 칩렛 포트폴리오를 갖는 꿈이 현실이 되려면 수년이 걸릴 것이라고 믿습니다."라고 말하면서 상호 운용성은 다음과 같은 파트너 그룹에서 나타날 것이라고 덧붙였습니다. 불완전한 사양의 위험을 해결하고 있습니다.

이는 또한 현장의 하드웨어에 대한 맞춤화 및 업데이트 수준을 제공할 수 있는 FPGA 및 eFPGA의 매력을 높이고 있습니다. Flex Logix의 CEO인 Geoff Tate는 "칩렛은 현실입니다."라고 말했습니다. “현재 두 개 이상의 칩렛을 만드는 회사는 수율이 거의 없는 레티클 크기에 가까운 다이를 만드는 회사보다 훨씬 더 경제적으로 운영할 수 있습니다. Chiplet 표준화는 아직 갈 길이 멀은 것 같습니다. UCIe조차도 아직은 고정된 표준이 아닙니다. UCIe, 베어 다이 테스트, 통합 패키지가 작동하지 않을 때의 문제 책임 등에 대해 모든 사람이 동의하는 것은 아닙니다. UCIe와 같이 표준이 유동적인 인터페이스에 대해 eFPGA를 사용하거나 평가하는 일부 고객이 있습니다. 지금 실리콘을 구현하고 나중에 eFPGA를 사용하여 표준 변경 사항을 준수할 수 있습니다.”

칩렛을 지원하는 다른 노력도 있지만, 그 이유는 다소 다르지만 특히 장치 확장 비용의 상승과 가장 발전된 노드에서 레티클이 제한된 칩에 더 많은 기능을 통합해야 할 필요성이 있습니다. 그러나 이러한 노력은 자동차 분야의 칩렛 개발의 길을 열었으며, 이 모든 것이 가능하도록 업계에서 강력한 지원을 제공하고 있습니다. 예를 들어, SEMI, ASME 및 2.5개 IEEE 협회의 후원을 받는 새로운 이종 통합 로드맵(HIR)은 다양한 마이크로 전자공학 설계, 재료 및 패키징 문제를 조사하여 반도체 산업을 위한 로드맵을 제시합니다. 현재 중점 분야에는 3D, XNUMXD-IC, 웨이퍼 레벨 패키징, 통합 포토닉스, MEMS 및 센서, SiP(시스템 인 패키지), 항공우주, 자동차 등이 포함됩니다.

최근 열린 이종 통합 글로벌 서밋 2023에는 AMD, Applied Materials, ASE, Lam Research, MediaTek, Micron, Onto Innovation, TSM 대표들이 참석했습니다.C, 그리고 다른 사람들은 칩렛에 대한 강력한 지원을 보여주었습니다. 칩렛을 지원하는 또 다른 그룹은 Chiplet 디자인 교환 (CDX) 워킹 그룹의 일부입니다. 개방형 도메인 특정 아키텍처 (ODSA) 및 오픈 컴퓨팅 프로젝트 재단(OCP). CDX(Chiplet Design Exchange) 헌장은 2.5D 스택 및 3D 집적 회로(3D-IC)의 전기, 기계 및 열 설계 교환 표준을 포함하여 칩렛 및 칩렛 통합의 다양한 특성에 중점을 둡니다. 그 대표자는 다음과 같습니다 안 시스, Applied Materials, Arm, Ayar Labs, Broadcom, Cadence, Intel, Macom, Marvell, Microsemi, NXP, Siemens EDA, Synopsys 등

Siemens의 Fritz는 “각 칩렛의 기능 측면에서 자동차 회사가 원하는 것은 여전히 격변 모드에 있습니다.”라고 말했습니다. “한 극단에는 이런 문제가 있고, 다른 극단에는 이런 문제가 있습니다. 이것이 바로 좋은 장소입니다. 이것이 필요한 것입니다. 그리고 이들은 나가서 그런 종류의 일을 할 수 있는 유형의 회사이고, 그런 다음 그들을 하나로 모을 수 있습니다. 그렇다면 이 상호 운용성은 큰 문제가 아닙니다. OEM은 '가능성의 모든 스펙트럼을 처리해야 합니다.'라고 말함으로써 이를 너무 복잡하게 만들 수 있습니다. 대안은 '마치 고속 PCIe와 같다'라고 말할 수 있다는 것이다. 서로 의사소통하고 싶다면 나는 이미 그 방법을 알고 있습니다. 내 운영 체제를 실행하는 드라이버가 있습니다. 그렇게 하면 엄청나게 많은 문제가 해결될 것이고, 결국은 거기서 끝나리라 믿습니다.”

범용 칩렛 개발을 위한 한 가지 경로는 무엇입니까?

앞으로 칩렛은 자동차 및 칩 산업 모두의 중심이 되며, 여기에는 칩렛 IP부터 메모리 상호 연결, 맞춤화 옵션 및 제한 사항까지 모든 것이 포함됩니다.

예를 들어 Renesas Electronics는 2023년 XNUMX월에 차세대 SoC 및 MCU에 대한 계획을 발표했습니다. 이 회사는 고급 인패키지 칩렛 통합 기술을 갖춘 고성능 애플리케이션을 위한 XNUMX세대 R-Car SoC에 대한 고급 정보를 포함하여 자동차 디지털 도메인 전반의 모든 주요 애플리케이션을 목표로 삼고 있습니다. 이는 자동차 엔지니어에게 맞춤화할 수 있는 더 큰 유연성을 제공하기 위한 것입니다. 그들의 디자인.

Renesas는 첨단 운전자 지원 시스템(ADAS)에 더 많은 AI 성능이 필요한 경우 엔지니어가 AI 가속기를 단일 칩에 통합할 수 있는 기능을 갖게 될 것이라고 말했습니다. 회사는 이 로드맵이 하드웨어가 출시되기 전에도 소프트웨어 설계 및 검증을 포함하여 품질 저하 없이 개발을 가속화할 수 있는 방법을 모색해 온 Tier 1 및 OEM 고객과의 수년간의 협력 및 논의 끝에 나온 것이라고 밝혔습니다.

"온디맨드 컴퓨팅을 증가시켜야 하는 필요성이 점점 증가하고 미래 자동차의 자율성에 대한 요구가 증가함에 따라 향후 몇 년간 시장의 성능 요구 사항을 확장하고 제공하는 모놀리식 솔루션에 어려움이 있을 것으로 보입니다."라고 말했습니다. Renesas의 SoC 비즈니스 및 전략 담당 수석 이사인 Vasanth Waran입니다. "Chiplets를 사용하면 컴퓨팅 솔루션을 시장의 요구 이상으로 확장할 수 있습니다."

르네사스는 다음과 같은 계획을 발표했습니다. Chiplet 기반 제품군 특히 2025년부터 자동차 시장을 목표로 하고 있습니다.

표준 인터페이스를 통해 SoC 맞춤화 가능

오늘날 대부분의 칩렛이 사용되는 표준 프로세서와 자동차 애플리케이션용으로 개발된 칩렛 사이에 얼마나 많은 중복이 있을지는 완전히 명확하지 않습니다. 그러나 이 기술이 새로운 시장으로 전환됨에 따라 기본 기술과 개발은 확실히 서로 강화될 것입니다.

Synopsys의 IP 가속 솔루션 그룹 수석 제품 관리자인 David Ridgeway는 “AI 가속기이든 ADAS 자동차 애플리케이션이든 고객에게는 표준 인터페이스 IP 블록이 필요합니다.”라고 말했습니다. “고객의 SoC에 사용되는 하위 시스템 구성 요소를 지원하려면 IP 사용자 정의 요구 사항에 대해 완전히 검증된 IP 하위 시스템을 제공하는 것이 중요합니다. 사용자 정의라고 하면 지난 10~20년 동안 PHY 측과 컨트롤러 측에서 IP가 어떻게 사용자 정의 가능해졌는지 모르실 수도 있습니다. 예를 들어, PCI Express는 PCIe Gen 3에서 Gen 4, Gen 5, 이제 Gen 6으로 전환되었습니다. 컨트롤러는 x16 8개, x4 XNUMX개 또는 xXNUMX XNUMX개를 포함하여 더 작은 링크 폭의 여러 분기 모드를 지원하도록 구성할 수 있습니다. 우리의 하위 시스템 IP 팀은 고객과 협력하여 모든 사용자 정의 요구 사항이 충족되도록 합니다. AI 애플리케이션의 경우 신호 및 전력 무결성은 성능 요구 사항을 충족하는 데 매우 중요합니다. 거의 모든 고객은 TPU가 초당 더 많은 트랜잭션을 처리할 수 있도록 가능한 최고의 메모리 대역폭 속도를 달성하기 위해 한계를 뛰어넘기를 원합니다. 애플리케이션이 클라우드 컴퓨팅이나 인공 지능일 때마다 고객은 가능한 가장 빠른 응답 속도를 원합니다.”

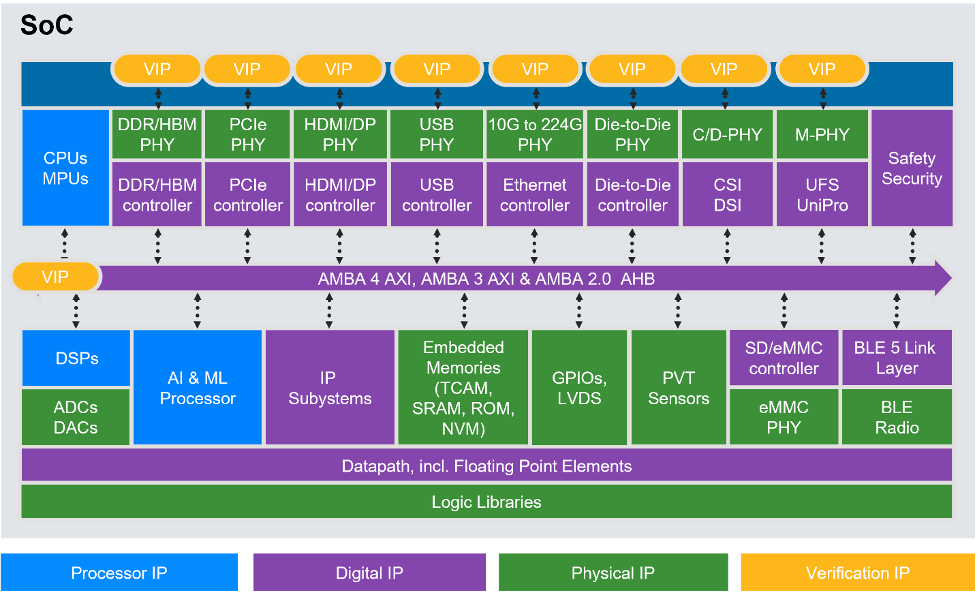

그림 1: 프로세서, 디지털, PHY 및 검증을 포함한 IP 블록은 개발자가 전체 SoC를 구현하는 데 도움이 됩니다. 출처 : Synopsys

PPA 최적화는 효율성 향상이라는 궁극적인 목표를 달성하며, 이는 자동차 애플리케이션에서 칩렛을 특히 매력적으로 만듭니다. UCIe가 성숙해지면 전반적인 성능이 기하급수적으로 향상될 것으로 예상됩니다. 예를 들어 UCIe는 표준 패키지에서 28~224GB/s/mm, 고급 패키지에서 165~1317GB/s/mm의 해안선 대역폭을 제공할 수 있습니다. 이는 20~100배의 성능 향상을 의미합니다. 지연 시간을 20ns에서 2ns로 낮추면 10배 개선됩니다. 10pJ/b(표준 패키지) 및 0.5pJ/b(고급 패키지)에서 약 0.25배 향상된 전력 효율성도 또 다른 장점입니다. 핵심은 가능할 때마다 인터페이스 거리를 줄이는 것입니다.

칩렛 설계를 최적화하기 위해 UCIe 컨소시엄은 몇 가지 제안을 제공합니다.

- 아키텍처 컷라인(예: 칩렛 경계)을 신중하게 계획하여 전력, 대기 시간, 실리콘 영역 및 IP 재사용을 최적화합니다. 예를 들어, 최첨단 프로세스 노드가 필요한 하나의 칩렛을 사용자 정의하는 동시에 기존 노드에서 다른 칩렛을 재사용하면 비용과 시간에 영향을 미칠 수 있습니다.

- 패키지 열 봉투, 핫스팟, 칩렛 배치, I/O 라우팅 및 브레이크아웃에 대한 열 및 기계 패키징 제약 조건을 계획해야 합니다.

- 프로세스 노드는 특히 관련 전력 공급 방식의 맥락에서 신중하게 선택해야 합니다.

- 칩렛 및 패키지/조립 부품에 대한 테스트 전략은 패키지로 조립된 이후가 아닌 칩렛 수준 테스트 단계에서 실리콘 문제를 포착할 수 있도록 사전에 개발되어야 합니다.

결론

다이-투-다이 인터페이스를 표준화하려는 아이디어는 빠르게 인기를 얻고 있지만 거기에 도달하려면 시간과 노력이 필요하며 서로 거의 대화하지 않는 회사 간의 많은 협업이 필요합니다. 차량을 만들려면 자동차 제조업체를 결정해야 합니다. 칩렛으로 차량을 제작하려면 개발자, 파운드리, OSAT, 재료 및 장비 공급업체를 포함하는 전체 생태계가 함께 협력해야 합니다.

자동차 OEM은 시스템을 통합하고 비용을 절감할 수 있는 혁신적인 방법을 찾는 전문가입니다. 그러나 상호 운용 가능한 칩렛의 생태계를 얼마나 빠르고 효과적으로 구축하고 활용하여 설계 주기를 단축하고, 맞춤화를 개선하고, 최첨단 기술이 완전히 설계되고 테스트될 때 구식이 될 수 있는 세상에 적응할 수 있는지는 아직 알 수 없습니다. , 소비자에게 제공됩니다.

— Ann Mutschler가 이 보고서에 기여했습니다.

- SEO 기반 콘텐츠 및 PR 배포. 오늘 증폭하십시오.

- PlatoData.Network 수직 생성 Ai. 자신에게 권한을 부여하십시오. 여기에서 액세스하십시오.

- PlatoAiStream. 웹3 인텔리전스. 지식 증폭. 여기에서 액세스하십시오.

- 플라톤ESG. 탄소, 클린테크, 에너지, 환경, 태양광, 폐기물 관리. 여기에서 액세스하십시오.

- PlatoHealth. 생명 공학 및 임상 시험 인텔리전스. 여기에서 액세스하십시오.

- 출처: https://semiengineering.com/why-chiplets-are-so-critical-in-automotive/