Il 13 settembre 2021, Andes Technology Corporation ha lanciato con successo la sua offerta pubblica GDR (Global Depositary Receipt) sulla Borsa del Lussemburgo. All'epoca Andes era l'unico fornitore pubblico internazionale di IP CPU con architettura del set di istruzioni RISC-V (ISA). Ciò ha consentito agli investitori di tutto il mondo di partecipare alla crescita andina prevista per RISC-V. Questa infusione di capitale alimenterebbe l’ambizione delle Ande di diventare leader nel mercato RISC-V con standard aperti, in rapida evoluzione e ad alta crescita. Nel 2015, riconoscendo il vasto potenziale dell'ISA RISC-V, Andes è diventata membro fondatore e Premier di RISC-V International.

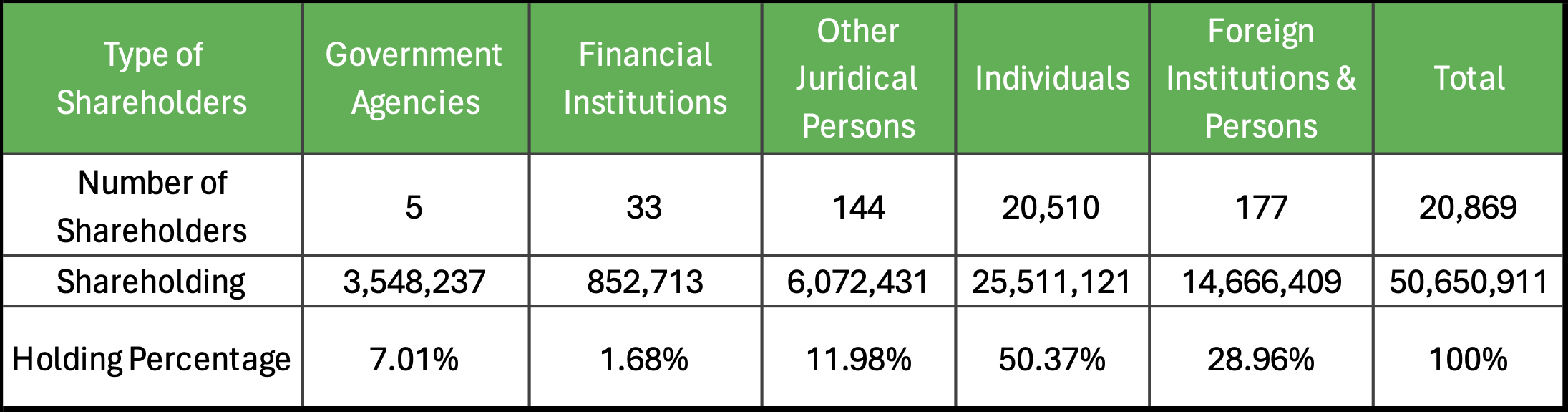

A partire dal 2 aprile 2023; Unità: Azioni, %

L’investimento ha dato i suoi frutti in modo significativo soprattutto perché è coinciso con la ratifica dell’estensione vettoriale RISC-V nel novembre 2021. Questo evento ha segnato un punto di svolta nell’evoluzione dell’architettura del set di istruzioni RISC-V. L'estensione vettoriale RISC-V è arrivata in un momento in cui l'elaborazione dei data center stava passando dall'elaborazione per scopi generici all'elaborazione AI, che gestisce set di dati estremamente grandi. L'elaborazione vettoriale eccelle nell'elaborazione efficiente di array di grandi dimensioni o dati strutturati. L'elaborazione vettoriale ha il potenziale per rendere RISC-V il prossimo grande ISA a livello mondiale.

L'architettura altamente parallela di un processore vettoriale riduce la latenza e il sovraccarico. Raggiunge una migliore efficienza energetica massimizzando l'utilizzo delle risorse della CPU e riducendo al minimo i cicli di inattività, realizzando così prestazioni più elevate per watt. Inoltre, l'hardware per implementare le unità di elaborazione vettoriale (VPU) RISC-V e i registri vettoriali è più semplice rispetto alle architetture altamente parallele utilizzate per l'elaborazione grafica. E le VPU forniscono un modello di programmazione molto meno complesso.

I team di ricerca e sviluppo andini sia nelle operazioni nordamericane che nel personale ampliato di Taiwan si sono concentrati sullo sviluppo di architetture all'avanguardia per processori RISC-V di fascia alta. In particolare, i due hanno raggiunto un traguardo significativo sviluppando il primo motore vettoriale RISC-V (RVV), l'AndesCore™ NX27V, basato sulla specifica RISC-V International RVV. Dimostrando l'agilità e l'innovazione del team di ingegneri andini, il progetto è stato completato entro un anno e basato sulla versione V0.8 della specifica di estensione vettoriale RISC-V, e successivamente modificato alla versione V1.0 quando RVV è stato ratificato. Questo risultato ha portato ad alcune importanti vittorie di progettazione OEM.

L'anno scorso alla conferenza International Symposium on Computer Architecture (ISCA) 2023 a Orlando, in Florida, META ha presentato il suo documento, "MTIA: First Generation Silicon Targeting Meta's Recommendation Systems", che è il data center dell'azienda, progetto di server AI. Nella progettazione del server sono presenti 64 elementi di elaborazione (PE) che supportano l'acceleratore proprietario personalizzato di MRETA. Ogni PE contiene due processori: uno scalare e uno vettoriale. Entrambi sono IP andini che META ingegnerizza altamente personalizzati, utilizzando Andes Custom Extensions (ACE) per produrre una soluzione completamente unica mirata ai requisiti specifici di elaborazione AI di META.

Il progetto ha convalidato l'efficacia di RISC-V con Vector Extensions come potente soluzione alle esigenze di elaborazione dei data center con intelligenza artificiale in un momento in cui la domanda di hardware di elaborazione dei data center è in forte espansione. Secondo Approfondimenti sul mercato futuro' rapporto "Data Center CPU Market Outlook (2023 to 2033)", Si prevede che il mercato delle CPU per data center crescerà in modo significativo nei prossimi anni, guidato dalla crescente domanda di cloud computing, analisi dei big data e intelligenza artificiale (AI) . I fattori chiave di questa crescita includono la necessità di un’elaborazione dei dati più rapida, una maggiore efficienza e costi ridotti.

Nel 2021, oltre alle estensioni vettoriali, RISC-V International ha ratificato altre 11 estensioni. La Figura 1 illustra la roadmap del prodotto Andes per supportare queste estensioni. Lungo il percorso fino alla fine del 2022, sono state consegnate le serie N25F-SE, 27 e 45, nel 2023, Andes ha consegnato al mercato sei nuovi core RISC-V, come D25F-SE, D23, N225, NX45V, AX45MPV così come AX65. La road map spazia dal processore RISC-V entry-level a basso consumo e altamente protetto AndesCore™ D23 all'AX65, il primo della serie 60, che è stato rilasciato nel quarto trimestre del 2023 e ora è disponibile per i progetti dei clienti.

L'AX65 è un processore fuori servizio a 13 bit a 4 stadi e 64 vie con profilo RVA 22 (il profilo RVA22U64 specifica le funzionalità ISA disponibili per gli ambienti di esecuzione in modalità utente nei processori di applicazioni a 64 bit). Dotata di pipeline a 13 stadi, decodifica a 4 ampi, esecuzione fuori ordine a 8 ampi, la serie si rivolge ai socket dei processori delle applicazioni Linux di elaborazione, rete e controller di fascia alta.

L'AX65 consente cluster multicore da uno a quattro fino a otto core. Le prestazioni sono di prima classe, funzionando con una frequenza di clock di 2.4 gigahertz in un processo TSMC a sette nanometri. Le prestazioni degli interi specifici (Specint 2006) sono 8.25 per gigahertz e SpecFp2006 è 10.2 per gigahertz, che sono le prestazioni SPEC CPU® 2006 più note con design della cache a due livelli. Successivamente verranno consegnati gli AX66, AX63 e AX67.

Un'altra area in cui Andes ha investito in modo significativo è l'IP CPU RISC-V di livello automobilistico ad alte prestazioni. Si prevede che la penetrazione dei SoC RISC-V nella progettazione automobilistica raggiungerà il 21.4% entro il 2030, secondo The SHD Group "Rapporto sul mercato RISC-V: previsioni applicative in un mondo eterogeneo." Andes ha sviluppato prodotti conformi alla sicurezza funzionale, tra cui N25F-SE, il primo IP CPU RISC-V al mondo completamente conforme allo standard ISO 26262; D25F-SE, che supporta le istruzioni di estensione DSP; e i processori della serie 45-SE che soddisfano il livello ASIL più elevato, ASIL D. La funzione ACE verrà migliorata per aggiungere il supporto per i processori della serie 45.

Forte della domanda che i prodotti Andes RISC-V hanno riscontrato, l'azienda continua a rimanere redditizia e continua a godere di una rapida crescita. Dal 2021 al 2023, le entrate delle Ande hanno mostrato una crescita di quasi il 30%. Ciò è stato alimentato da oltre 300 licenziatari commerciali e oltre 600 accordi di licenza firmati con clienti geograficamente distribuiti a Taiwan, Cina, Corea, Giappone, Europa e Stati Uniti. Nello stesso periodo l'organico mondiale dell'azienda è cresciuto di quasi il 70%.

Conclusione

In un'era definita dalla rapida evoluzione tecnologica, Andes Technology Corp. è in prima linea nell'innovazione nel mercato IP delle CPU RISC-V. Dall'emissione pionieristica di ricevute di deposito all'estero (GDR) ai progressi rivoluzionari nell'architettura RISC-V, Andes Technology continua a ridefinire gli standard di settore e a plasmare il futuro dell'informatica. Poiché la domanda di soluzioni informatiche efficienti e ad alte prestazioni continua ad aumentare, Andes Technology continua a impegnarsi a fornire soluzioni RISC-V senza precedenti per guidare il cambiamento trasformativo nel panorama tecnologico globale.

Leggi anche:

Condividi questo post tramite:

- Distribuzione di contenuti basati su SEO e PR. Ricevi amplificazione oggi.

- PlatoData.Network Generativo verticale Ai. Potenzia te stesso. Accedi qui.

- PlatoAiStream. Intelligenza Web3. Conoscenza amplificata. Accedi qui.

- PlatoneESG. Carbonio, Tecnologia pulita, Energia, Ambiente, Solare, Gestione dei rifiuti. Accedi qui.

- Platone Salute. Intelligence sulle biotecnologie e sulle sperimentazioni cliniche. Accedi qui.

- Fonte: https://semiwiki.com/ip/343097-andes-technology-pioneering-the-future-of-risc-v-cpu-ip/