Pendant GOMACTech conférence tenue en Caroline du Sud la semaine dernière, j'ai eu un appel Zoom avec Deepak Shankar, fondateur et vice-président de la technologie chez Mirabilis Design Inc. pour poser des questions et voir une démo en direct de VisualSim – une plateforme de modélisation, de simulation, d’exploration et collaborative pour développer l’électronique et les SoC. Ce qui rend VisualSim si distinctif, c'est qu'il est livré avec environ 500 blocs IP de haut niveau prêts à l'emploi, dont 35 processeurs ARM, une centaine de processeurs et plus de 100 interconnexions différentes. Les utilisateurs de VisualSim connectent rapidement ces blocs IP entre eux visuellement pour créer leurs systèmes, dotés de réseaux. Un concepteur automobile peut modéliser l'ensemble du réseau, y compris les communications 30G, les mises à jour Ethernet, SDA et OTA avec VisualSim.

Un modèle de haut niveau permet une exploration architecturale plus rapide et des compromis architecturaux, bien avant même que la mise en œuvre ne commence avec le code RTL. Vous pouvez modéliser des activités complexes comme un bus, des mémoires et même un cache, en mesurant des éléments tels que les retards et la latence de bout en bout. Les ingénieurs peuvent mesurer le taux de réussite/échec du cache et ce qui se passe avec les requêtes adressées aux caches L2. Tous les protocoles réseaux courants sont modélisés : AXI, CHI, CMN600, Arteris NOC, UCIe, etc.

Avec cette approche de modélisation, un architecte peut modéliser un SoC, un avion ou un système automobile complet, puis commencer à mesurer ses performances pour voir s'il répond aux exigences. VisualSim est un simulateur multidomaine qui peut intégrer les systèmes analogiques, logiciels, électriques, numériques et réseau dans un seul modèle.

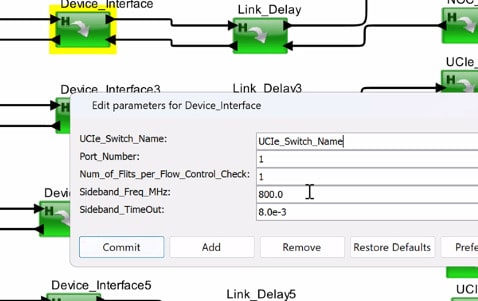

Pour la démo en direct, Deepak m'a montré une conception basée sur des chipsets comportant des chipsets distincts pour le DSP, le GPU, le processeur AI et le CPU, tous connectés ensemble à l'aide d'UCIe, et chaque bloc IP a été paramétré pour permettre la personnalisation et l'exploration.

En poussant dans le bloc UCIe, il y avait une adresse IP appelée commutateur UCIe, et un utilisateur peut personnaliser ce bloc avec cinq paramètres, tous à un niveau élevé.

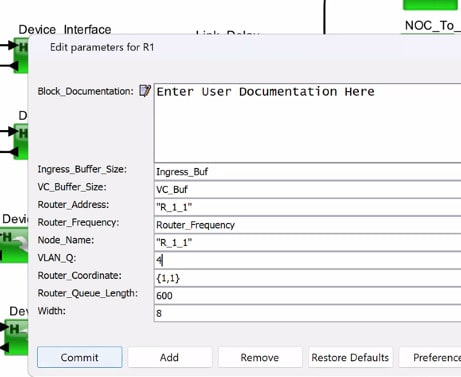

Un bloc IP de routeur comportait 10 paramètres de personnalisation.

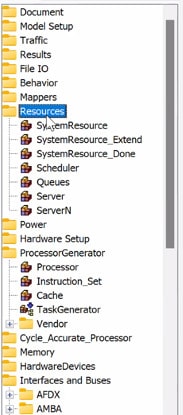

Pour trouver chaque bloc IP, il y avait une liste déroulante sur le côté gauche de l'interface graphique, avec chaque famille d'IP dans la bibliothèque. En quelques secondes, vous pouvez parcourir, sélectionner et commencer à personnaliser une adresse IP.

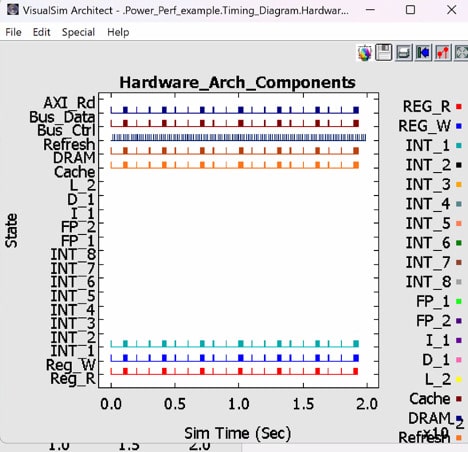

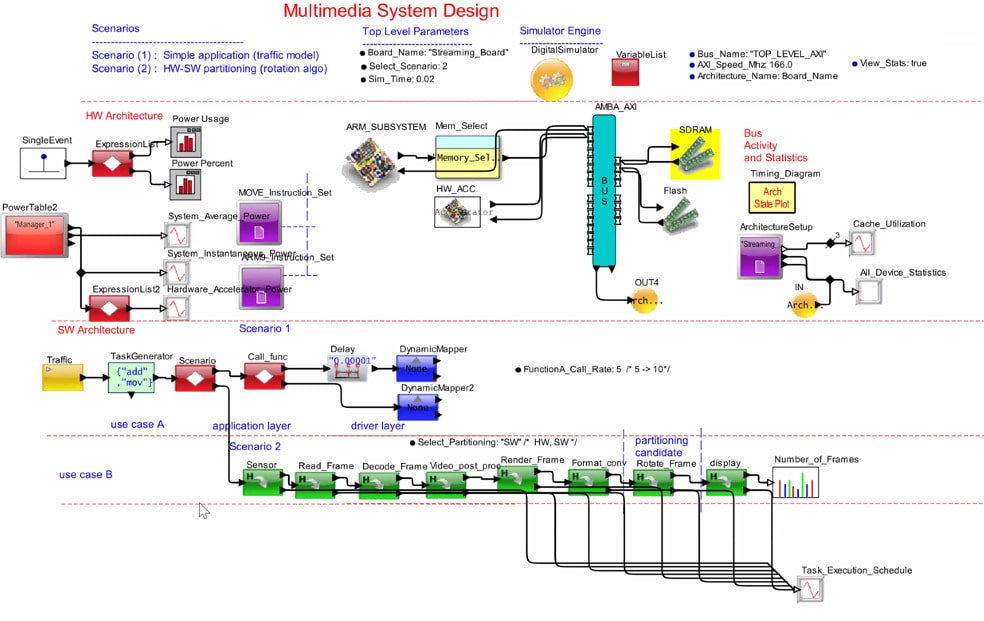

Dans VisualSim, vous connectez chaque IP du flux de données, en restant à un niveau élevé. La démonstration en direct suivante concernait la conception d'un système multimédia, et pour simuler 20 ms, il fallait environ 15 secondes de temps mural, exécuté sur un ordinateur portable. Pendant l'exécution de la simulation, vous pouvez visualiser les performances du système sous forme de puissance instantanée, mesurer l'utilisation du pipeline, l'utilisation du cache, l'utilisation de la mémoire et même afficher un chronogramme. Cette simulation en temps réel a déclenché 7.5 millions d'événements et le client a construit ce modèle en moins de 2 semaines, incluant l'intégralité du SoC.

Un autre exemple de client mentionné par Deepak comprend 45 maîtres et a été achevé en 4 semaines environ, entièrement testé.

Vous pouvez examiner l’intérieur de n’importe quel bloc IP et analyser des métriques telles que réussite/échec, puis comprendre pourquoi il a échoué. Il existe même un moteur d'IA pour aider à analyser les données plus efficacement, comme trouver un débordement de tampon qui a provoqué une panne. Pendant l'exécution de votre modèle, des analyses sont capturées pour vous aider à mesurer les performances du système et à identifier les goulots d'étranglement architecturaux.

VisualSim est mis à jour deux fois par an, puis il existe des mises à jour de correctifs lorsque de nouveaux blocs IP sont ajoutés. Un architecte définit les exigences dans un fichier Excel, avec des mesures telles que les limites de latence et l'occupation de la mémoire tampon.

Les utilisateurs de VisualSim peuvent définir la plage de taille de charge utile en termes d'octets, de plages de vitesse et de valeurs préférées. Votre modèle de système peut être balayé à travers les combinaisons pour trouver le meilleur ensemble de paramètres. Le simulateur comprend même comment explorer les valeurs min, max et préférées. Vous pouvez définir quels paramètres du système seront explorés. Une démonstration du système multimédia a ensuite été présentée, puis simulée en direct.

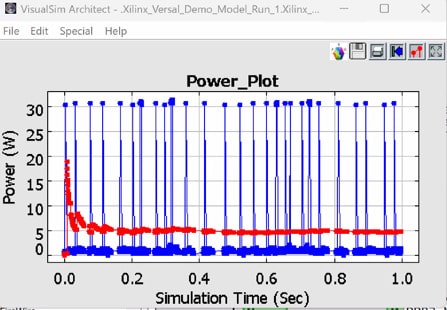

Pour un bloc FPGA, vous choisissez le fournisseur et le numéro de pièce, puis vous pouvez voir la latence de chaque tâche et les statistiques de canal du NOC après l'exécution d'une simulation. Un tracé de puissance a été affiché pendant 1 seconde de fonctionnement lors de l'utilisation de pièces Xilinx Versal.

Toutes les démos en direct étaient exécutées sur un ordinateur portable Windows. Les autres systèmes d'exploitation pris en charge sont : Unix, Mac. L'exécution de VisualSim nécessite une infrastructure matérielle minimale, car les modèles sont de haut niveau.

Les utilisateurs de VisualSim reçoivent plus de 500 exemples prédéfinis pour vous aider à démarrer rapidement, comme un système de communication complet avec une antenne, un émetteur-récepteur, un FPGA avec bande de base et une interface Ethernet. Les architectes système utilisant VisualSim peuvent collaborer avec tous les spécialistes de bas niveau, comme les concepteurs RTL.

Les compromis au niveau du système peuvent être modélisés et évalués, comme :

- Passage de la modulation 64-QAM à la modulation QPSK

- Processeur plus rapide à plus lent

- Modification des spécifications Ethernet

Si vous commencez avec VisualSim pour modéliser, implémenter, puis mesurer, attendez-vous à obtenir une précision de 95 % par rapport aux résultats de l'implémentation RTL. La promesse de l’utilisation de modèles de haut niveau est d’éliminer les problèmes de performances avant la mise en œuvre ou l’intégration. Aucun codage n’est vraiment requis pour un modèle de système complet.

Mirabilis compte à ce jour 65 clients dans le monde et quelque 250 projets réalisés. Certains des clients bien connus incluent : NASA, Samsung, Qualcomm, Broadcom, GM, Boeing, HP, Imagination, Raytheon, AMD, Northrup Grumman.

Résumé

Autrefois, un concepteur de systèmes dessinait peut-être ses idées sur une serviette en mangeant au restaurant, puis retournait au travail et bricolait des feuilles de calcul Excel avec des équations obscures pour créer un modèle. Aujourd'hui, il y a un nouveau choix, et cela donne VisualSim de Mirabilis, un essai. Vous pouvez désormais modéliser un système entier en quelques semaines seulement, tout en faisant des compromis architecturaux tout en exécutant des simulations réelles, le tout avant d'entrer dans les détails détaillés de la mise en œuvre.

Blogs connexes

Partagez cet article via:

- Contenu propulsé par le référencement et distribution de relations publiques. Soyez amplifié aujourd'hui.

- PlatoData.Network Ai générative verticale. Autonomisez-vous. Accéder ici.

- PlatoAiStream. Intelligence Web3. Connaissance Amplifiée. Accéder ici.

- PlatonESG. Carbone, Technologie propre, Énergie, Environnement, Solaire, La gestion des déchets. Accéder ici.

- PlatoHealth. Veille biotechnologique et essais cliniques. Accéder ici.

- La source: https://semiwiki.com/ip/343387-a-modeling-simulation-exploration-and-collaborative-platform-to-develop-electronics-and-socs/