Pour le Symposium de stratégie internationale SEMI 2024, les membres du comité organisateur m'ont mis au défi de déterminer où en sera la logique dans dix ans du point de vue de la technologie, de l'économie et de la durabilité. Ce qui suit est une discussion de ma présentation.

Pour comprendre la logique, je pense qu’il est utile de comprendre ce qui constitue les dispositifs logiques de pointe. TechInsights produit des rapports d'analyse détaillés de l'empreinte et j'ai rédigé des rapports pour dix appareils de classe 7 nm et 5 nm, notamment des microprocesseurs Intel et AMD, des processeurs Apple A Series et M Series, un GPU NVIDIA et d'autres appareils. La figure 1 illustre ce qui constitue la zone de la matrice.

D'après la figure 1, la logique représente un peu moins de la moitié de la surface de la puce, la mémoire un peu moins d'un tiers de la puce et les E/S, analogiques et autres, le reste. Je trouve intéressant que les zones de mémoire SRAM réellement mesurées soient beaucoup plus petites que le pourcentage dont j'entends généralement parler pour les produits System On a Chip (SOC). Le graphique en bas à droite montre qu’il existe une valeur aberrante, mais sinon les valeurs sont étroitement regroupées.

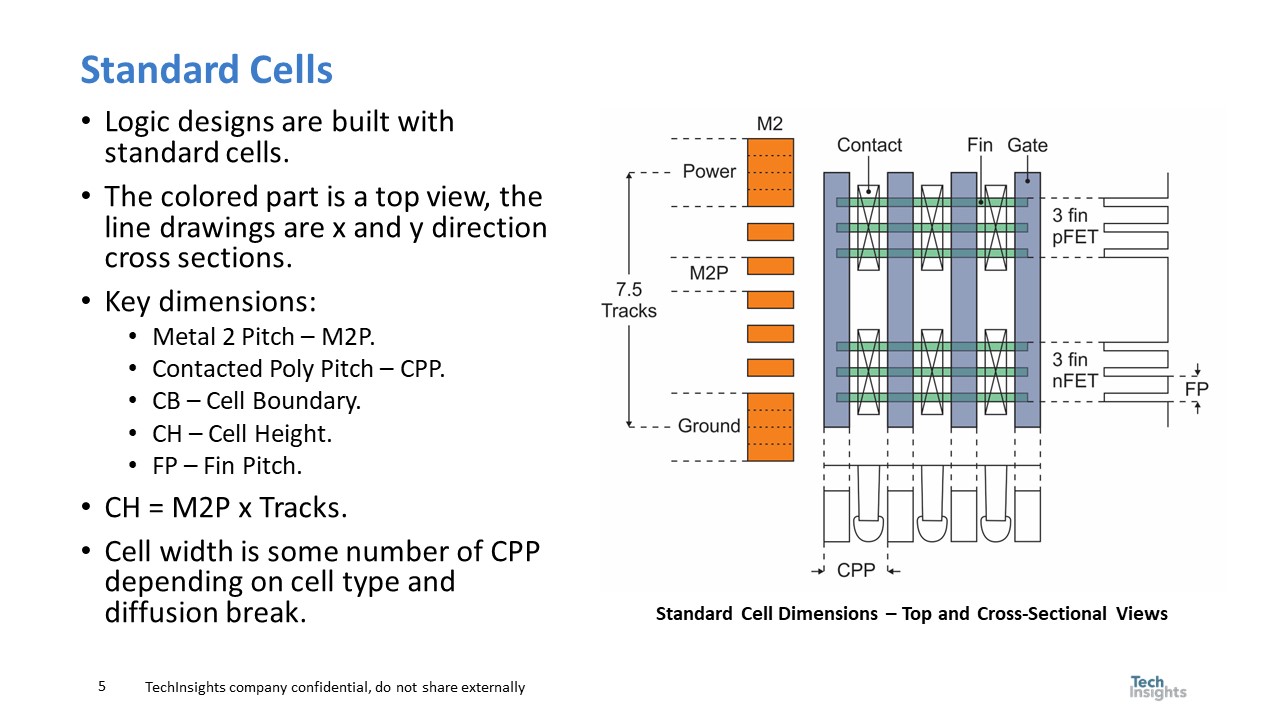

La logique unique représente près de la moitié de la surface de la puce, il est logique de commencer par la partie logique de la conception. Les conceptions logiques sont réalisées avec des cellules standard et la figure 2 est une vue en plan d'une cellule standard.

La hauteur d'une cellule standard est généralement caractérisée par le pas métallique 2 (M2P) multiplié par le nombre de pistes, mais en regardant le côté droit de la figure, vous trouverez une vue en coupe transversale de la structure de l'appareil qui doit également correspondre à la hauteur de la cellule. et est limité par la physique des appareils. Il en va de même pour la largeur de cellule qui dépend du pas poly contacté (CPP) et en regardant au bas de la figure, vous trouverez une vue en coupe transversale de la structure du dispositif qui est encore une fois contrainte par la physique.

La figure 3 présente le résultat d'une analyse visant à déterminer les limites pratiques de la mise à l'échelle de la largeur et de la hauteur des cellules. J'ai une présentation qui détaille les contraintes de mise à l'échelle et dans cette présentation il y a des dizaines de diapositives entre la figure 2 et la figure 3, mais avec un temps limité, je n'ai pu montrer que la conclusion.

La mise à l'échelle de la largeur des cellules dépend du CPP, et le côté gauche de la figure illustre comment le CPP est composé de la longueur de grille (Lg), de la largeur de contact (Wc) et de deux épaisseurs d'espacement de contact à grille (Tsp). Lg est limité par les fuites et le Lg minimum avec une fuite acceptable dépend du type d'appareil. Les dispositifs planaires avec une seule porte contrôlant la surface d'un canal avec une épaisseur non contrainte sont limités à environ 30 nm. Les FinFET et les nanofeuilles horizontales (HNS) limitent l'épaisseur du canal (~ 5 nm) et disposent respectivement de 3 et 4 portes. Enfin, les matériaux 2D introduisent une épaisseur de canal <1 nm, des matériaux sans silicium et peuvent produire du Lg jusqu'à ~ 5 nm. Wc et Tsp ont tous deux une capacité d'évolution limitée en raison de parasites. En fin de compte, un appareil 2D peut probablement produire un CPP d'environ 30 nm par rapport aux CPP actuels qui sont d'environ 50 nm.

La mise à l'échelle de la hauteur des cellules est illustrée sur le côté droit de la figure. HNS propose des piles de nanofeuilles uniques à la place de plusieurs ailettes. Ensuite, l'évolution vers des dispositifs empilés avec un CFET élimine l'espacement horizontal np et empile le nFet et le pFET. Les hauteurs de cellules actuellement comprises entre 150 et 200 nm peuvent être réduites à environ 50 nm.

La combinaison du CPP et de la mise à l'échelle de la hauteur de cellule peut produire des densités de transistors d'environ 1,500 XNUMX millions de transistors par millimètre carré (MTx/mm2) contre aujourd'hui <300MTx/mm2. Il convient de noter que les matériaux 2D sont probablement une technologie prévue pour le milieu ou la fin de 2030, donc 1,500 XNUMX MTx/mm.2 est en dehors du calendrier discuté ici.

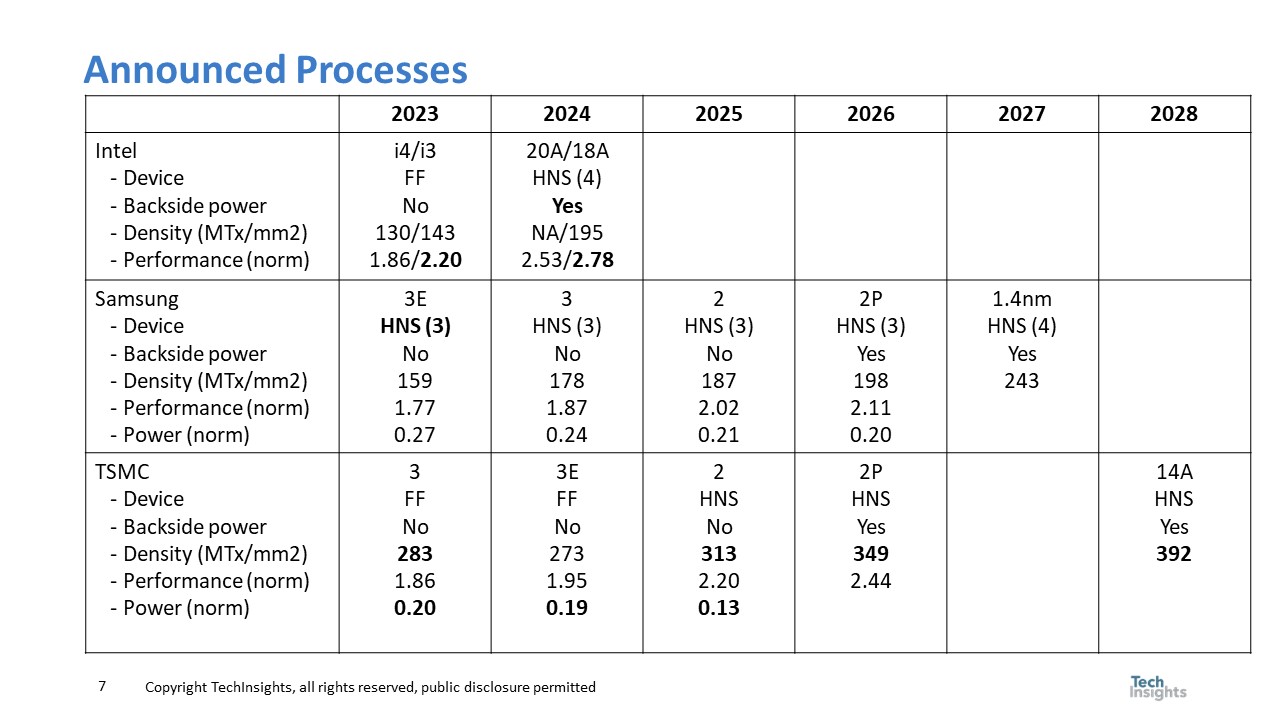

La figure 4 présente un résumé des processus annoncés par Intel, Samsung et TSMC.

Pour chaque entreprise et année, le type d'appareil, l'utilisation ou non de l'alimentation arrière, la densité, la puissance et les performances sont affichés si disponibles. La puissance et les performances sont des mesures relatives et la puissance n'est pas disponible pour Intel.

Dans la figure 4, les principales innovations technologiques et en matière de performances sont mises en évidence en gras. Samsung est le premier à mettre le HNS en production en 2023, tandis qu'Intel n'introduira le HNS qu'en 2024 et le TSMC avant 2025. Intel est le premier à introduire l'alimentation arrière en production en 2024 et Samsung et TSMC ne l'introduiront qu'en 2026.

Mon analyse conclut qu'Intel est le leader en termes de performances avec i3 et maintient ce statut pour la période illustrée, TSMC étant en tête en termes de puissance (données Intel non disponibles) et de densité.

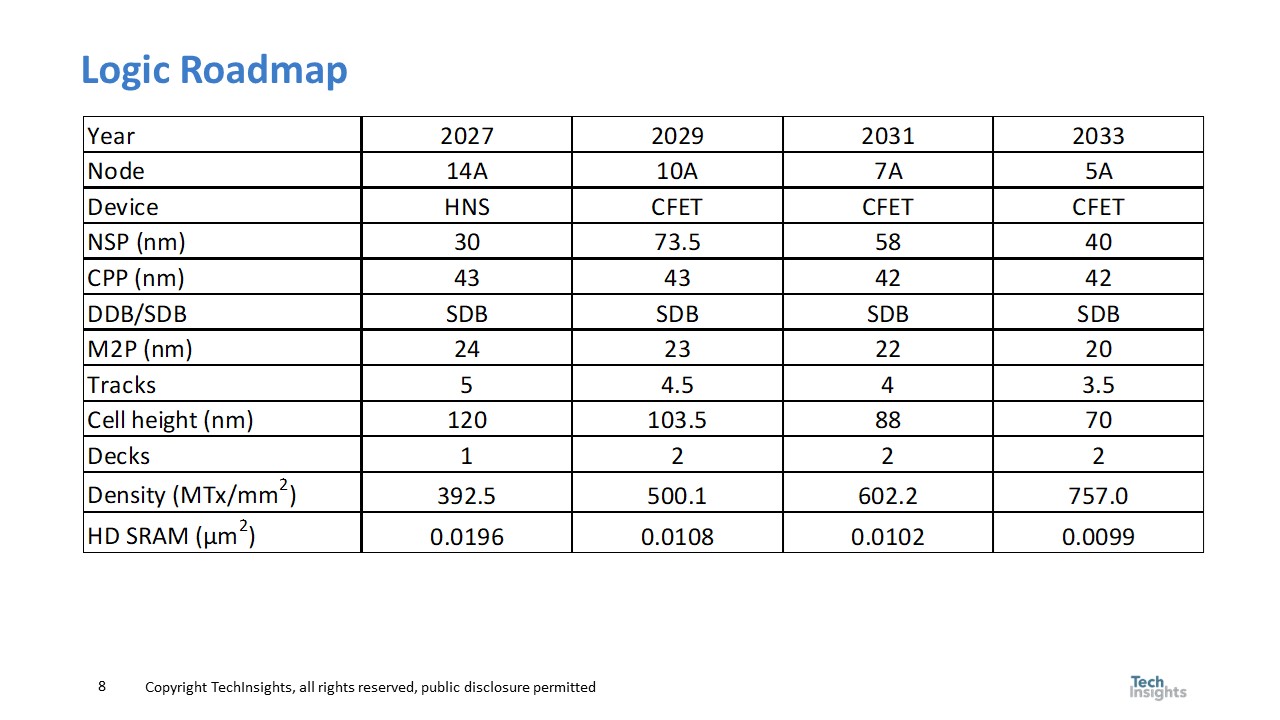

La figure 5 présente nos feuilles de route logiques et inclut les tailles projetées des cellules SRAM (nous en parlerons plus tard).

D'après la figure 5, nous nous attendons à ce que les CFET soient introduits vers 2029, offrant une augmentation de la densité logique et réduisant également de près de moitié la taille des cellules SRAM (la mise à l'échelle de la taille des cellules SRAM s'est pratiquement arrêtée au bord d'attaque). Nous nous attendons à ce que la densité logique atteigne ~757MTx/mm2 dès 2034.

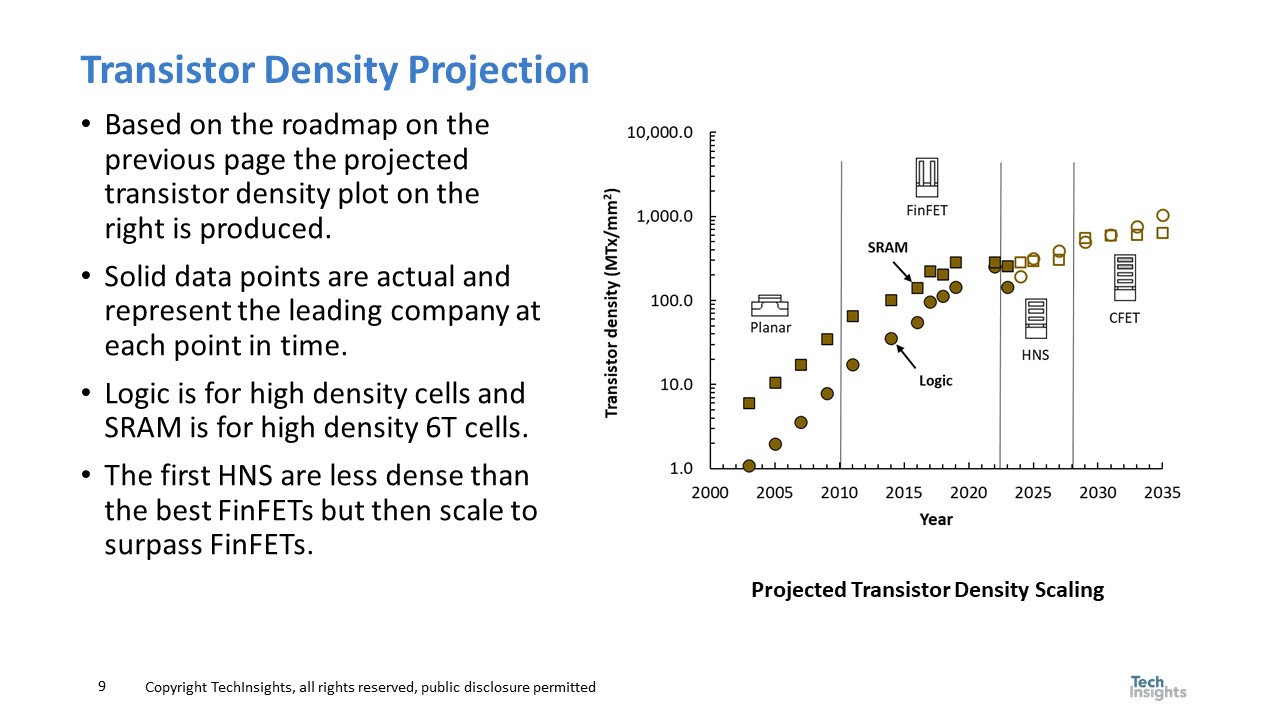

Les projections de densité de transistors logiques et les projections de densité de transistors SRAM sont illustrées dans la figure 6.

La mise à l'échelle de la densité des transistors logiques et SRAM ralentit, mais la SRAM dans une plus grande mesure et la logique a désormais une densité de transistors similaire à celle de la SRAM.

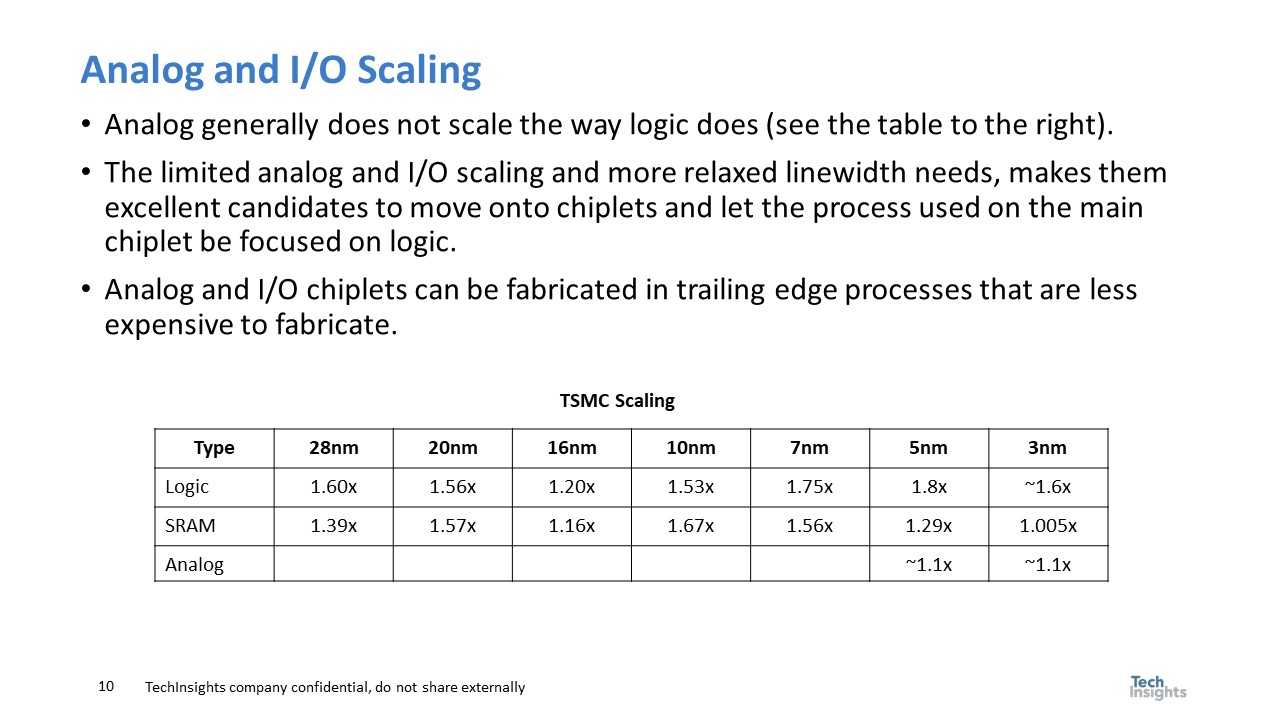

La diapositive 7 résume les données TSMC sur la mise à l'échelle analogique par rapport à Logic et SRAM. La mise à l'échelle analogique et des E/S est également plus lente que la mise à l'échelle logique.

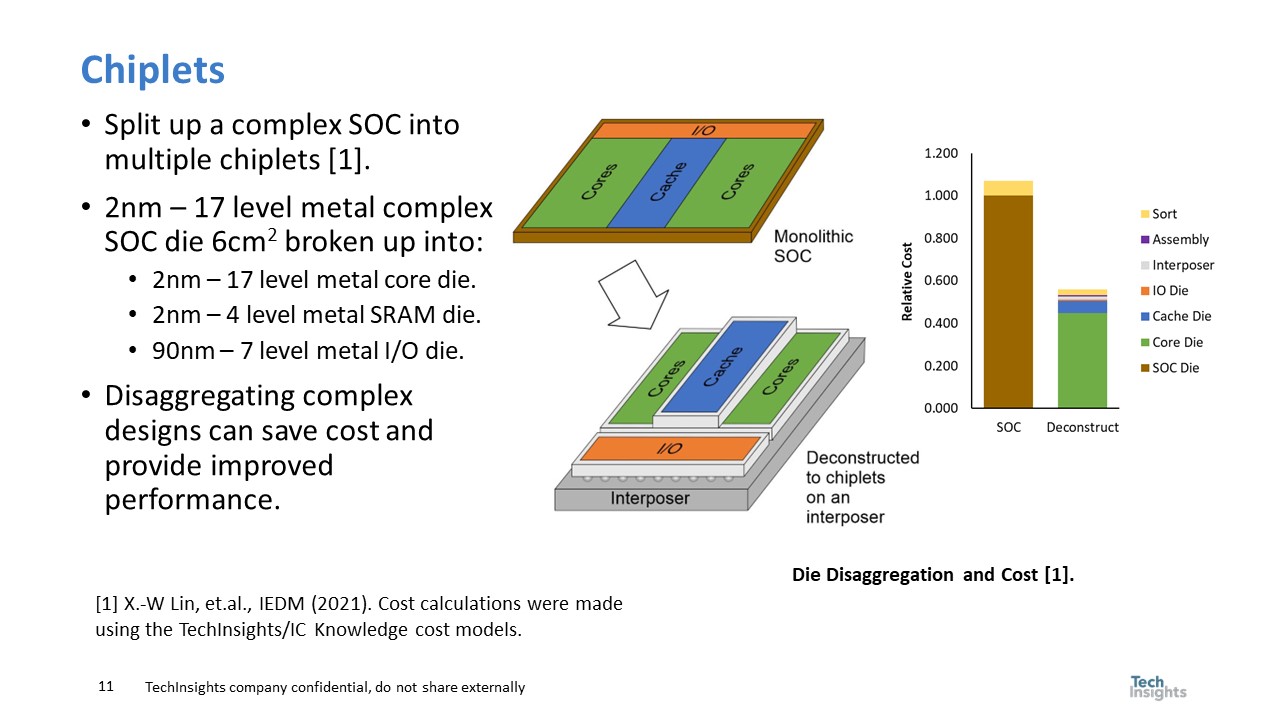

Les chipsets constituent une solution possible pour ralentir la mise à l'échelle de la SRAM et des E/S analogiques. Les chipsets peuvent permettre d'utiliser des processus moins coûteux et plus optimisés pour créer de la SRAM et des E/S.

La figure sur le côté droit de la figure 8 provient d'un article de 2021 que j'ai co-écrit avec Synopsys. Notre conclusion était que diviser un grand SOC en chipsets pouvait réduire le coût de moitié, même en tenant compte de l'augmentation des coûts d'emballage/d'assemblage.

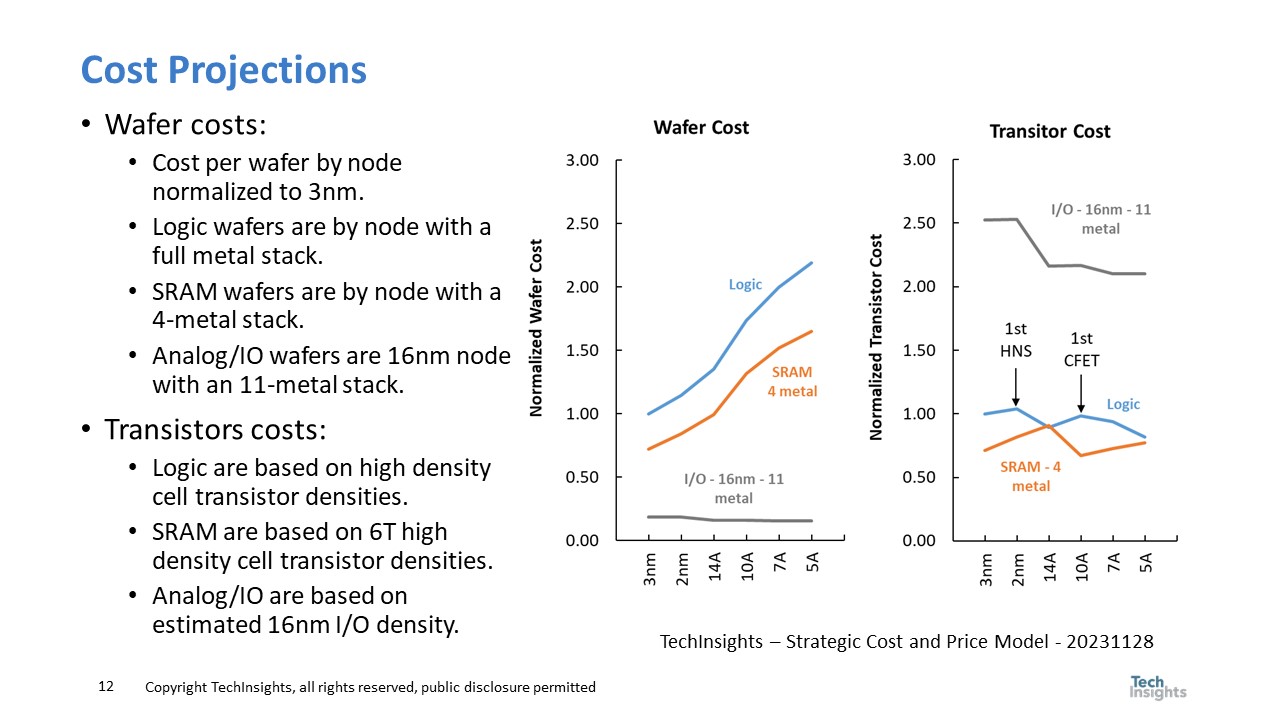

La figure 9 présente les coûts normalisés des tranches et des transistors pour la logique, la SRAM et les E/S (veuillez noter que la figure a été mise à jour par rapport à la présentation originale).

La figure de droite indique le coût normalisé de la tranche. Le coût de la plaquette logique correspond à une pile métallique complète dont le nombre de couches métalliques augmente. Les plaquettes SRAM sont les mêmes nœuds mais limitées à 4 couches métalliques en raison de la disposition plus régulière de la SRAM. Le coût de la plaquette d’E/S est basé sur un procédé métallique 16 nm – 11. J'ai sélectionné 16 nm pour obtenir un nœud FinFET à coût minimum afin de garantir des performances d'E/S adéquates.

Le chiffre de droite représente le coût de la plaquette converti en coût du transistor. Il est intéressant de noter que les transistors d'E/S sont si grands que même sur une tranche de 16 nm à faible coût, ils ont le coût le plus élevé (la taille du transistor d'E/S est basée sur les mesures TechInsights des transistors d'E/S réels). Les coûts des transistors logiques augmentent de 2 nm sur le premier nœud de feuille TSMC HNS où le rétrécissement est modeste. Nous nous attendons à ce que le rétrécissement à 14A soit plus important en tant que nœud HNS de deuxième génération (cela est similaire à ce que TSMC a fait avec son premier nœud FinFET). Encore une fois, le coût du premier nœud CFET augmente également le coût du transistor pour un nœud. Le coût des transistors SRAM a tendance à augmenter en raison d'une réduction limitée, à l'exception d'une réduction ponctuelle du CFET. L’essentiel de cette analyse est que la réduction du coût des transistors sera modeste, même si les chipsets peuvent offrir un avantage ponctuel.

Passant à la durabilité, la figure 10 explique les différents « périmètres » qui composent l'empreinte carbone.

Le scope 1 concerne les émissions directes du site dues aux produits chimiques de traitement et à la combustion (l'électricité peut également appartenir au scope 1 si elle est produite sur site), le scope 2 est dû à l'empreinte carbone de l'électricité achetée. Le scope 3 n'est pas inclus dans cette analyse mais est dû à l'empreinte carbone des matériaux achetés, de l'utilisation du produit fabriqué et d'éléments tels que les véhicules conduits par les employés d'une entreprise.

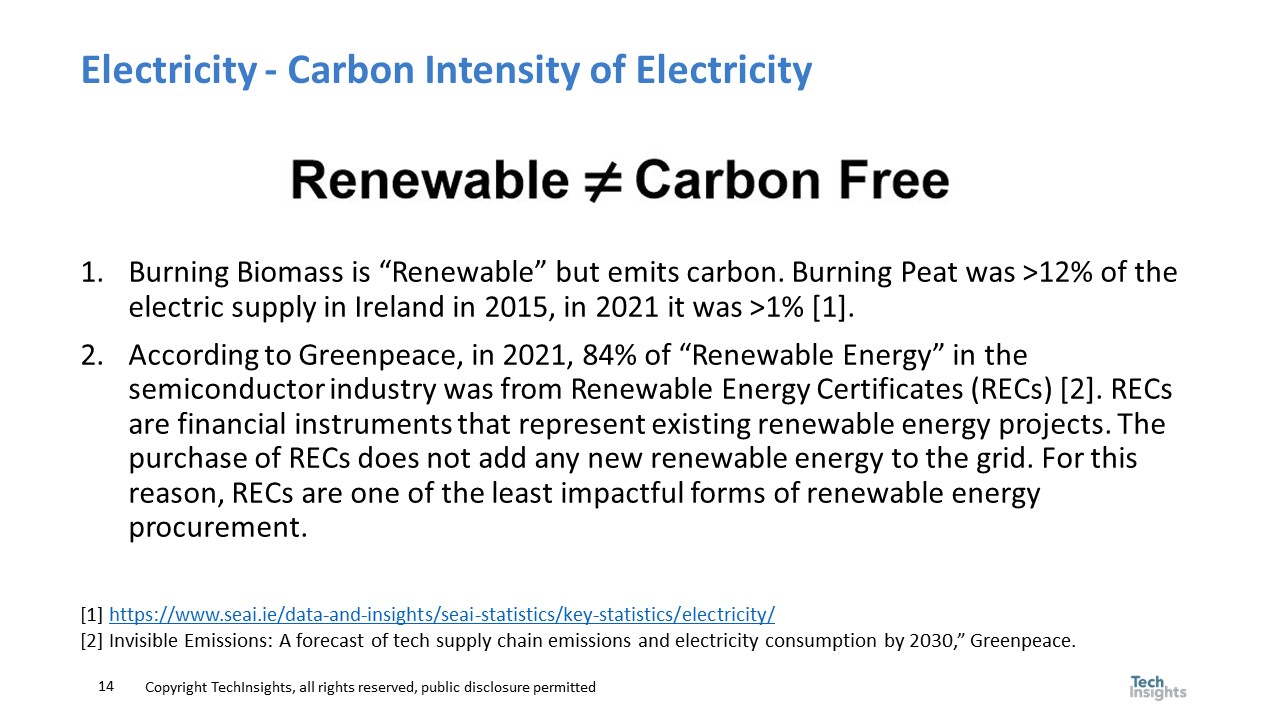

De nombreuses entreprises de l’industrie des semi-conducteurs affirment qu’elles n’émettent aucune émission de carbone due à l’électricité, car l’électricité est entièrement renouvelable. La figure 11 compare les énergies renouvelables aux énergies sans carbone.

Le principal problème est que Greenpeace a découvert que 84 % des énergies renouvelables dans l’industrie des semi-conducteurs en 2021 étaient des certificats d’énergie renouvelable dans le cadre desquels une entreprise achète les droits pour réclamer des réductions déjà effectuées par quelqu’un d’autre. Cela n’équivaut pas à installer des sources d’électricité à faible émission de carbone ou à payer d’autres personnes pour fournir de l’électricité à faible émission de carbone et ne réduit en fait pas l’empreinte carbone mondiale.

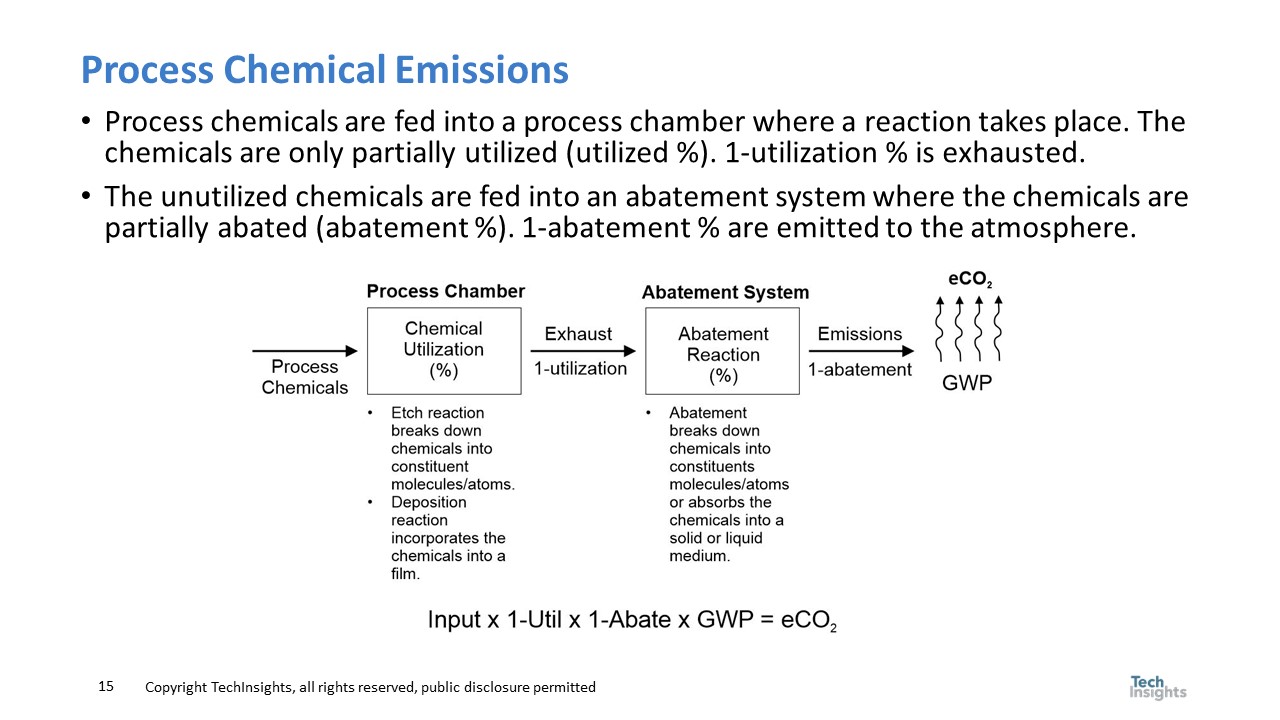

La figure 12 illustre comment les émissions de produits chimiques du procédé ont lieu et sont caractérisées.

Les produits chimiques de traitement entrent dans une chambre de traitement où un pourcentage des produits chimiques est utilisé dans une réaction de gravure ou de dépôt qui décompose les produits chimiques ou les incorpore dans un film déposé. 1-l'utilisation est la quantité de produit chimique qui s'échappe par l'échappement de l'outil. Les gaz d'échappement de l'outil peuvent ensuite entrer dans une chambre de réduction, décomposant davantage un pourcentage des produits chimiques et les émissions dans l'atmosphère résultant de la réduction sont de 1 réduction. Enfin, un potentiel de réchauffement global (GWP) est appliqué pour calculer l’équivalent carbone de l’émission. Le GWP prend en compte la durée de persistance du produit chimique dans l’atmosphère et la quantité de chaleur qu’il renvoie par rapport au dioxyde de carbone. Le dioxyde de carbone a un GWP de 1, les produits chimiques de traitement des semi-conducteurs tels que le SF6 et NF3 ont des valeurs GWP de 24,300 17,400 et 6 XNUMX respectivement (selon l'ARXNUMX du GIEC).

La figure 13 présente quelques options pour réduire les émissions.

Les sources d'électricité comme le charbon produisent 820 grammes de CO2 émissions équivalentes par kilowattheure (gCO2e/KWh) alors que les énergies solaire, hydroélectrique, éolienne et nucléaire produisent respectivement 48, 24, 12 et 12 gCO2e/KWh.

Des systèmes de réduction plus efficaces peuvent décomposer les gaz de procédé plus efficacement. L'efficacité du système de réduction Fab varie de 0 % pour certains sites américains signalés (pas de réduction) à environ 90 %. Nous estimons que la moyenne mondiale des usines de fabrication de tranches de 300 mm est d'environ 70 % et que la plupart des usines de fabrication de tranches de 200 mm et plus petites ne bénéficient d'aucune réduction. Des systèmes avec une efficacité allant jusqu'à 99 % sont disponibles.

Une chimie à faibles émissions peut également être utilisée. Tokyo Electron a annoncé un nouvel outil de gravure pour la NAND 3D qui utilise des gaz à GWP nul. Gaz tels que SF6 et NF3 sont principalement utilisés pour fournir du fluor (F) dans les chambres pour le nettoyage, en remplacement du F2 (GWP 0) ou COF2 (GWP 1) peut essentiellement éliminer cette source d’émissions.

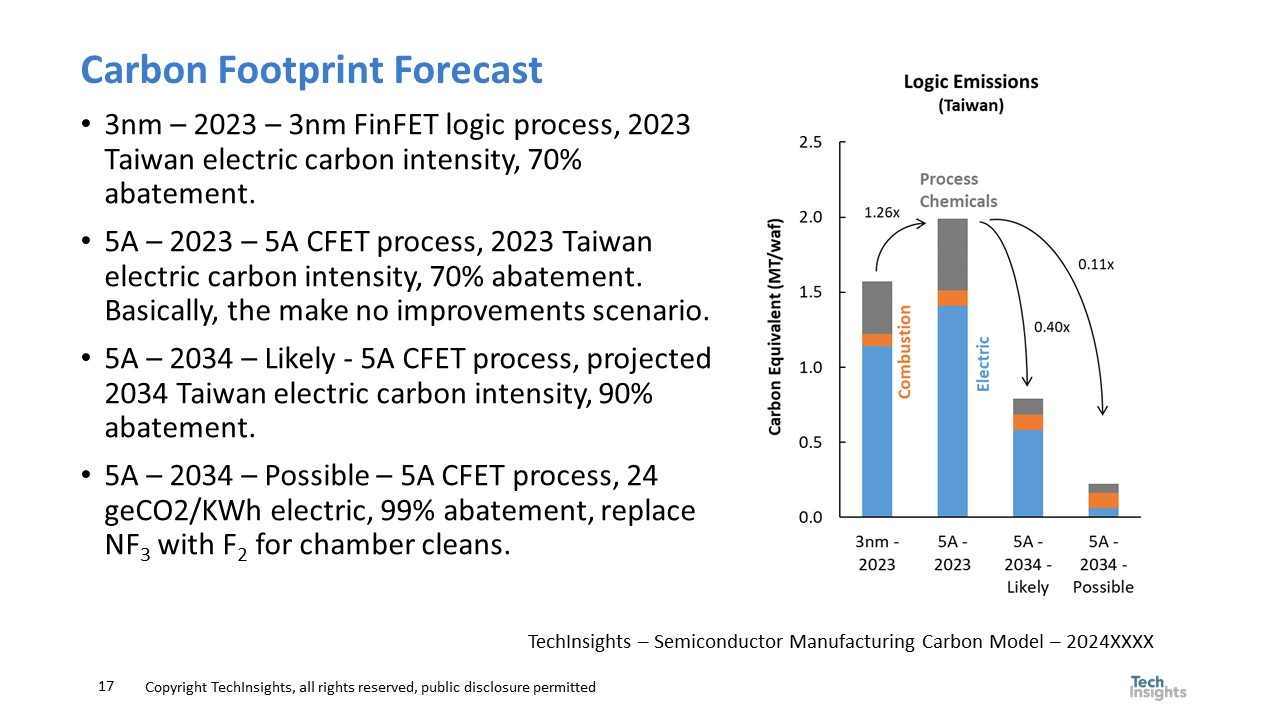

La figure 14 illustre une prévision de l'empreinte carbone pour la logique.

Dans la figure, la première barre à gauche représente un processus de 3 nm exécuté à Taïwan en 2023, en supposant l'empreinte carbone de l'électricité de Taïwan et une réduction de 70 %. La deuxième barre représente un processus 5A et les émissions qui résulteraient si la même intensité carbone de l'électricité de Taiwan en 2023 et la même réduction de 70 % étaient utilisées. L’augmentation de la complexité des processus entraînerait une multiplication par 1.26 de l’empreinte globale. D'ici 2034, l'électricité de Taiwan devrait se décarboner de manière significative, une réduction de 90 % devrait également être courante, et la troisième barre montre à quoi ressemblerait un processus 5A dans ces conditions. Même si cela représente une réduction des émissions de plus de moitié, la croissance du nombre de plaquettes exploitées par l’industrie d’ici 2034 annulerait probablement cette amélioration. La dernière barre à droite représente ce qui est possible avec un investissement suffisant, elle est basée sur une électricité à faible émission de carbone, une réduction de 99 % et l'utilisation de F2 pour le nettoyage de la chambre.

La figure 15 présente nos conclusions :

La densité des transistors et les estimations des coûts des plaquettes et des puces ont été générées à l'aide du modèle stratégique de coûts et de prix de TechInsights, une feuille de route industrielle qui produit des estimations de coûts et de prix ainsi que des exigences détaillées en matière d'équipement et de matériaux. Les estimations des émissions de GES ont été produites à l’aide du modèle carbone de TechInsights Semiconductor Manufacturing. Pour plus d'informations, veuillez contacter sales@techinsights.com

Je tiens à remercier mes collègues de l'unité commerciale d'ingénierie inverse de TechInsights, leur plan d'étage numérique et leurs rapports de processus ont été très utiles dans la création de cette présentation. Également, Alexandra Noguera de TechInsights pour avoir extrait les données de dimensionnement des transistors d'E/S pour ce travail.

Lisez aussi:

IEDM 2023 – Modélisation des émissions de carbone des usines de plaquettes de 300 mm

SMIC N+2 dans Huawei Mate Pro 60

Mise à jour ASML SEMICON West 2023

Partagez cet article via:

- Contenu propulsé par le référencement et distribution de relations publiques. Soyez amplifié aujourd'hui.

- PlatoData.Network Ai générative verticale. Autonomisez-vous. Accéder ici.

- PlatoAiStream. Intelligence Web3. Connaissance Amplifiée. Accéder ici.

- PlatonESG. Carbone, Technologie propre, Énergie, Environnement, Solaire, La gestion des déchets. Accéder ici.

- PlatoHealth. Veille biotechnologique et essais cliniques. Accéder ici.

- La source: https://semiwiki.com/semiconductor-manufacturers/342094-iss-2024-logic-2034-technology-economics-and-sustainability/