Für das SEMI International Strategy Symposium 2024 wurde ich von Mitgliedern des Organisationskomitees aufgefordert, herauszufinden, wo die Logik in zehn Jahren aus Technologie-, Wirtschafts- und Nachhaltigkeitsperspektive stehen wird. Im Folgenden wird meine Präsentation besprochen.

Um die Logik zu verstehen, ist es meiner Meinung nach hilfreich zu verstehen, was hochmoderne Logikgeräte ausmacht. TechInsights erstellt detaillierte Footprint-Analyseberichte, und ich habe Berichte für zehn Geräte der 7-nm- und 5-nm-Klasse erstellt, darunter Intel- und AMD-Mikroprozessoren, Prozessoren der Apple A-Serie und M-Serie, eine NVIDIA-GPU und andere Geräte. Abbildung 1 zeigt, was den Die-Bereich ausmacht.

Aus Abbildung 1 geht hervor, dass die Logik etwas weniger als die Hälfte der Chipfläche ausmacht, der Speicher etwas weniger als ein Drittel des Chips und I/O, Analog und andere den Rest ausmachen. Ich finde es interessant, dass die tatsächlich gemessenen SRAM-Speicherbereiche viel kleiner sind als der Prozentsatz, über den ich normalerweise bei System-On-a-Chip-Produkten (SOC) spreche. Das Diagramm unten rechts zeigt, dass es einen Ausreißer gibt, ansonsten sind die Werte jedoch eng geclustert.

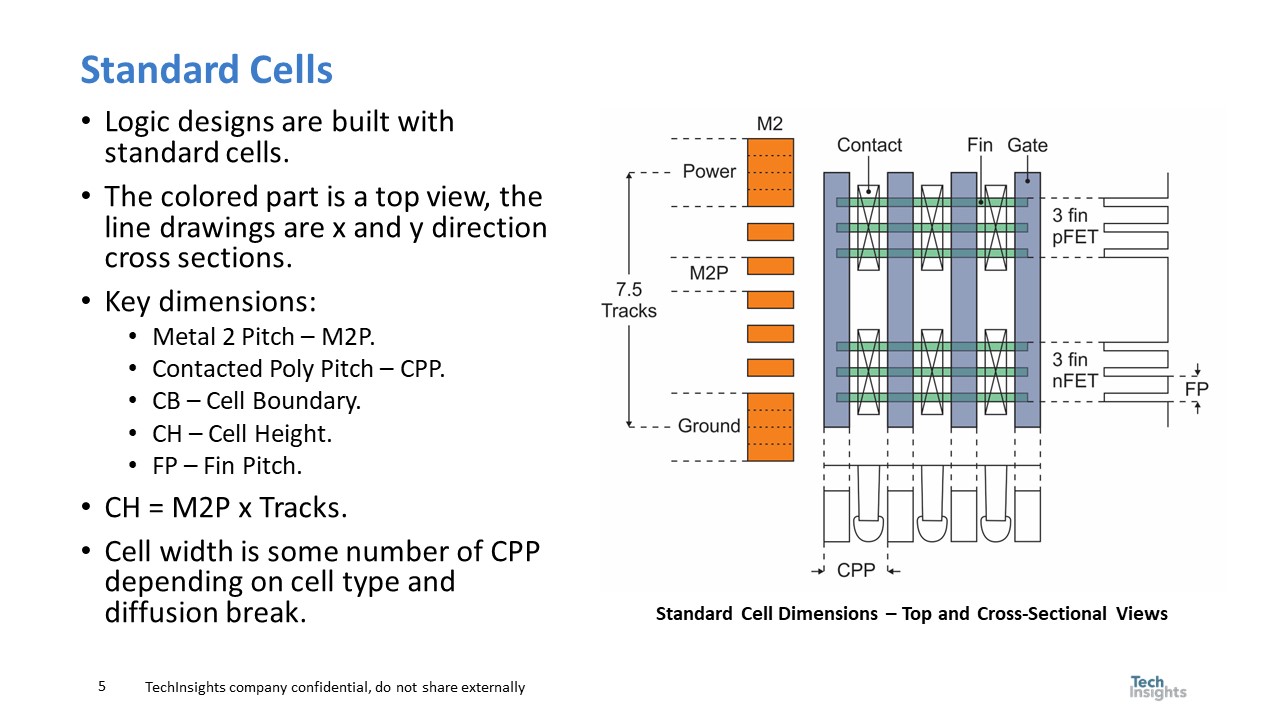

Die Einzellogik macht fast die Hälfte der Chipfläche aus, daher ist es sinnvoll, mit dem Logikteil des Designs zu beginnen. Logikentwürfe werden mit Standardzellen erstellt und Abbildung 2 ist eine Draufsicht einer Standardzelle.

Die Höhe einer Standardzelle wird normalerweise als Metal 2 Pitch (M2P) multipliziert mit der Anzahl der Spuren charakterisiert. Auf der rechten Seite der Abbildung ist jedoch eine Querschnittsansicht der Gerätestruktur zu sehen, die auch mit der Zellenhöhe übereinstimmen muss und wird durch die Gerätephysik eingeschränkt. Das Gleiche gilt für die Zellbreite, die vom Contacted Poly Pitch (CPP) abhängt. Unten in der Abbildung sehen Sie eine Querschnittsansicht der Gerätestruktur, die wiederum durch die Physik eingeschränkt ist.

Abbildung 3 zeigt das Ergebnis einer Analyse zur Bestimmung der praktischen Grenzen der Zellbreiten- und Zellhöhenskalierung. Ich habe eine Präsentation, in der die Skalierungsbeschränkungen detailliert beschrieben werden, und in dieser Präsentation gibt es Dutzende Folien zwischen Abbildung 2 und Abbildung 3, aber mit begrenzter Zeit konnte ich nur die Schlussfolgerung zeigen.

Die Skalierung der Zellenbreite hängt vom CPP ab, und die linke Seite der Abbildung zeigt, wie sich CPP aus der Gate-Länge (Lg), der Kontaktbreite (Wc) und zwei Kontakt-zu-Gate-Abstandsdicken (Tsp) zusammensetzt. Lg wird durch die Leckage begrenzt und die minimale Lg mit akzeptabler Leckage hängt vom Gerätetyp ab. Planare Bauelemente mit einem einzigen Gate, das die Oberfläche eines Kanals mit uneingeschränkter Dicke steuert, sind auf etwa 30 nm begrenzt. FinFETs und horizontale Nanoblätter (HNS) beschränken die Kanaldicke (~5 nm) und verfügen über 3 bzw. 4 Gates. Schließlich führen 2D-Materialien zu Kanaldicken von <1 nm, Nicht-Silizium-Materialien und können Lg bis zu ~5 nm erzeugen. Sowohl Wc als auch Tsp sind aufgrund von Parasiten nur begrenzt skalierbar. Unterm Strich kann ein 2D-Gerät wahrscheinlich einen CPP von ca. 30 nm erzeugen, im Vergleich zu heutigen CPPs von ca. 50 nm.

Die Skalierung der Zellenhöhe ist auf der rechten Seite der Abbildung dargestellt. HNS bietet einzelne Nanoblattstapel anstelle mehrerer Rippen an. Dann eliminiert die Entwicklung zu gestapelten Geräten mit einem CFET den horizontalen NP-Abstand und stapelt nFET und pFET. Zellhöhen, die derzeit 150 nm bis 200 nm betragen, können auf ~50 nm reduziert werden.

Die Kombination aus CPP und Zellhöhenskalierung kann Transistordichten von etwa 1,500 Millionen Transistoren pro Millimeter im Quadrat (MTx/mm) erzeugen2) im Vergleich zu heute <300MTx/mm2. Es ist zu beachten, dass es sich bei 2D-Materialien wahrscheinlich um eine Technologie Mitte bis Ende 2030 handelt, also 1,500 MTx/mm2 liegt außerhalb des hier besprochenen Zeitpunkts.

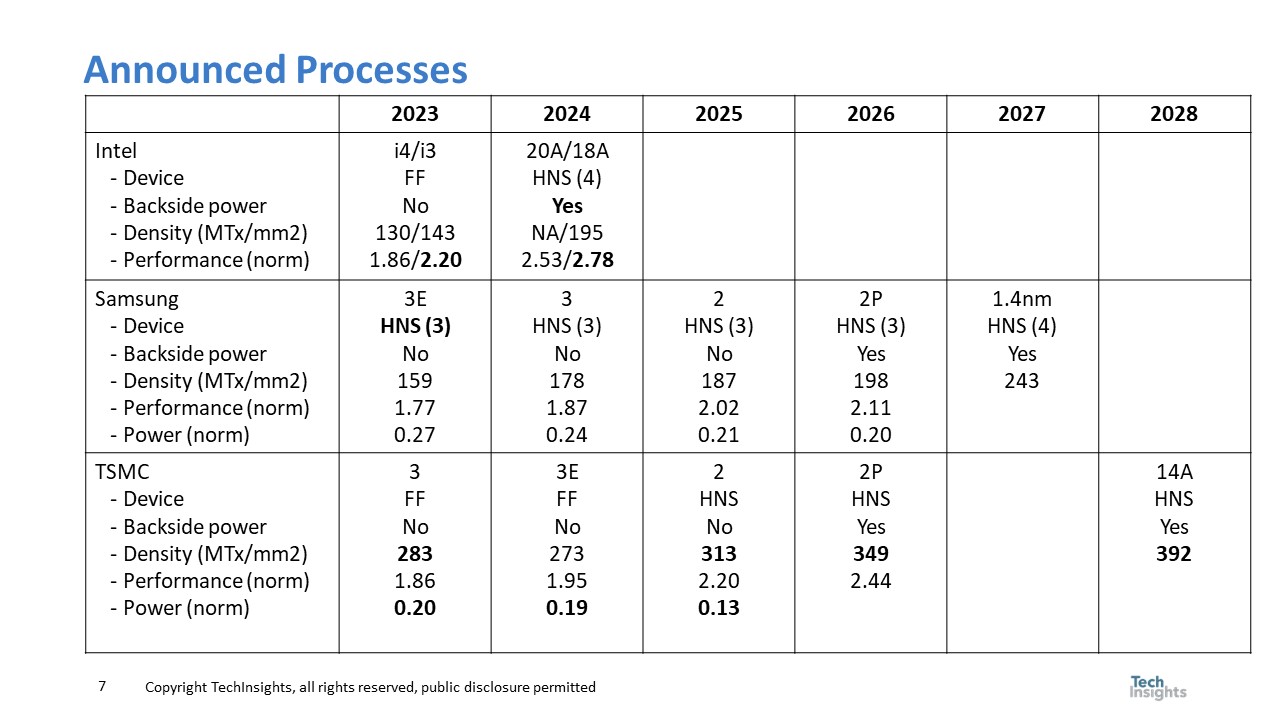

Abbildung 4 zeigt eine Zusammenfassung der angekündigten Prozesse von Intel, Samsung und TSMC.

Für jedes Unternehmen und jedes Jahr werden, sofern verfügbar, der Gerätetyp, ob Rückseitenstrom verwendet wird oder nicht, Dichte, Leistung und Leistung angezeigt. Leistung und Leistung sind relative Maßstäbe und Leistung ist für Intel nicht verfügbar.

In Abbildung 4 sind führende Leistungs- und Technologieinnovationen fett hervorgehoben. Samsung ist das erste Unternehmen, das HNS im Jahr 2023 in Produktion bringt, während Intel HNS erst 2024 und TSMC erst 2025 einführen wird. Intel ist das erste Unternehmen, das Backside Power im Jahr 2024 in Produktion bringt, und Samsung und TSMC werden es erst 2026 einführen.

Meine Analyse kommt zu dem Schluss, dass Intel mit i3 der Leistungsführer ist und diesen Status für den dargestellten Zeitraum beibehält, während TSMC die Führung in Sachen Leistung (Intel-Daten nicht verfügbar) und Dichte innehat.

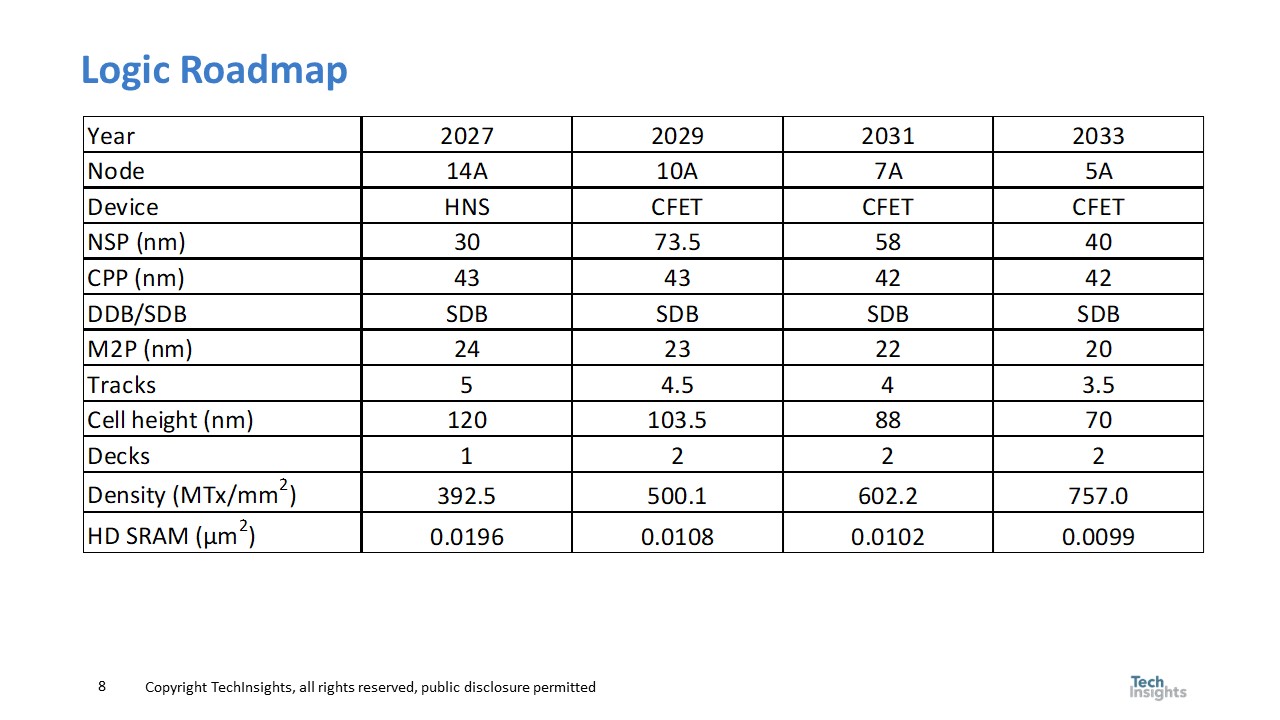

Abbildung 5 stellt unsere Logik-Roadmaps dar und enthält die prognostizierten SRAM-Zellengrößen (mehr dazu später).

Aus Abbildung 5 gehen wir davon aus, dass CFETs etwa im Jahr 2029 eingeführt werden, was zu einer Steigerung der Logikdichte führen und auch die SRAM-Zellengrößen nahezu halbieren wird (die Größenskalierung von SRAM-Zellen ist praktisch zum Stillstand gekommen). Wir gehen davon aus, dass die Logikdichte ~757 MTx/mm erreichen wird2 von 2034.

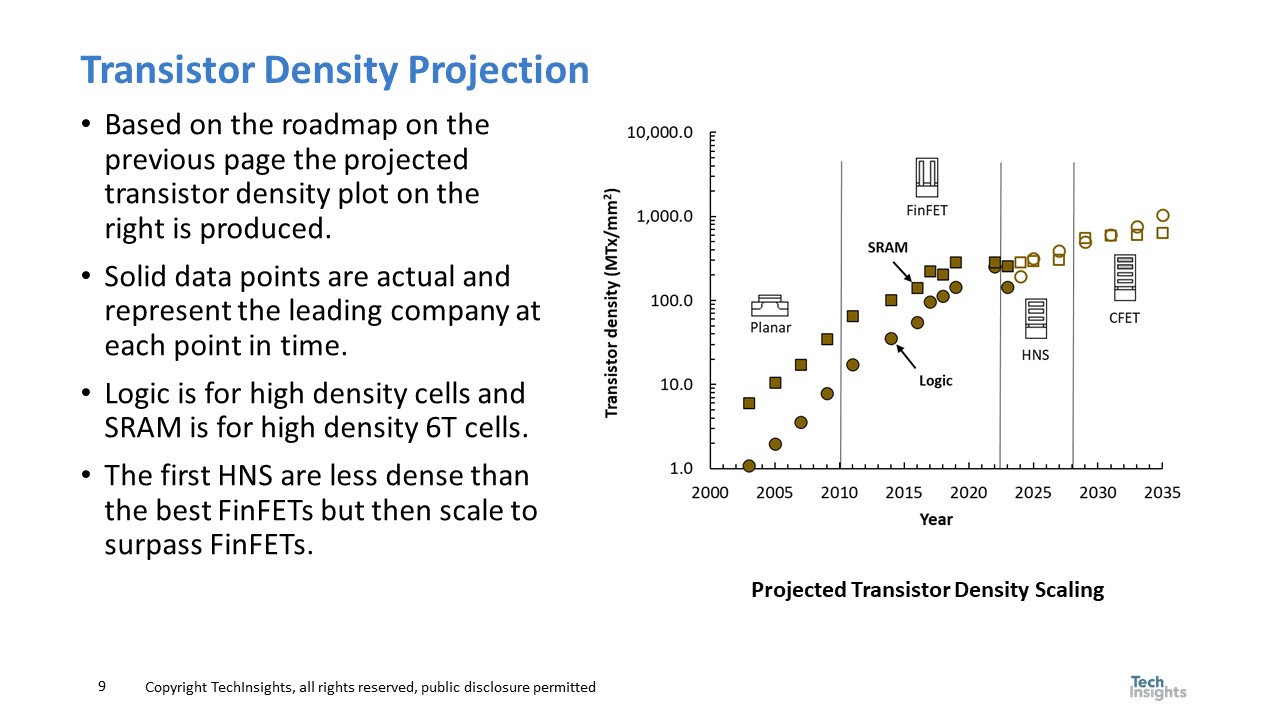

Sowohl die Dichteprognosen für Logiktransistoren als auch die Dichteprognosen für SRAM-Transistoren sind in Abbildung 6 dargestellt.

Sowohl die Skalierung der Logik- als auch der SRAM-Transistordichte verlangsamt sich, aber SRAM ist in größerem Maße aktiv, und die Logik hat jetzt eine ähnliche Transistordichte wie SRAM.

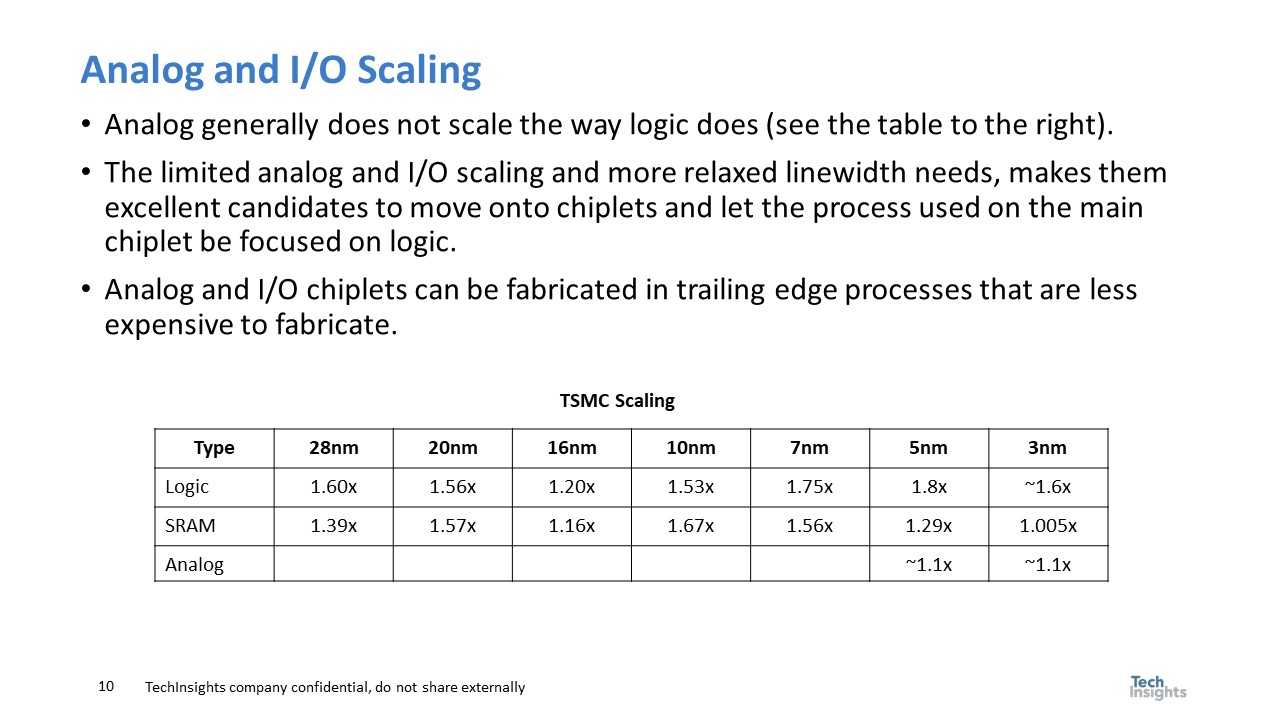

Folie 7 fasst TSMC-Daten zur analogen Skalierung im Vergleich zu Logik und SRAM zusammen. Auch die analoge und die E/A-Skalierung sind langsamer als die logische Skalierung.

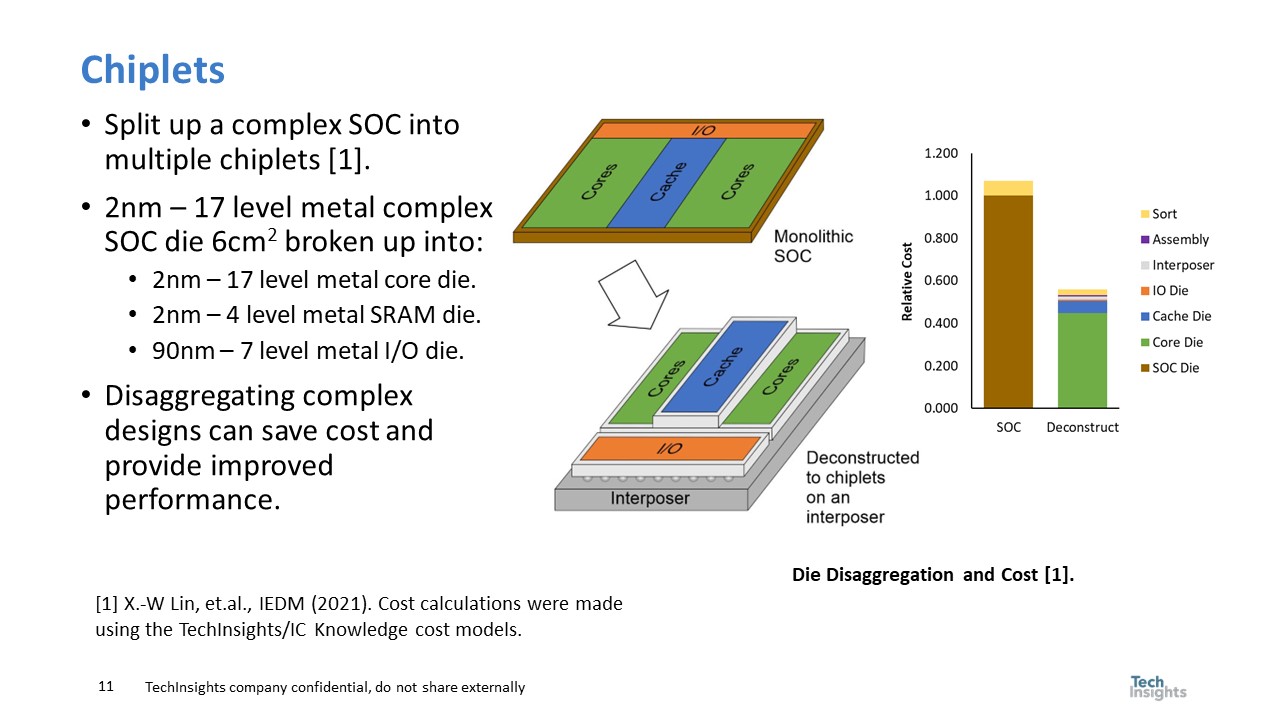

Eine mögliche Lösung für langsameres SRAM und analoge und I/O-Skalierung sind Chiplets. Chiplets können die Verwendung kostengünstigerer und optimierterer Prozesse zur Herstellung von SRAM und I/O ermöglichen.

Die Abbildung auf der rechten Seite von Abbildung 8 stammt aus einer Arbeit aus dem Jahr 2021, die ich gemeinsam mit Synopsys verfasst habe. Unsere Schlussfolgerung war, dass die Zerlegung eines großen SOC in Chiplets die Kosten sogar unter Berücksichtigung der erhöhten Verpackungs-/Montagekosten halbieren könnte.

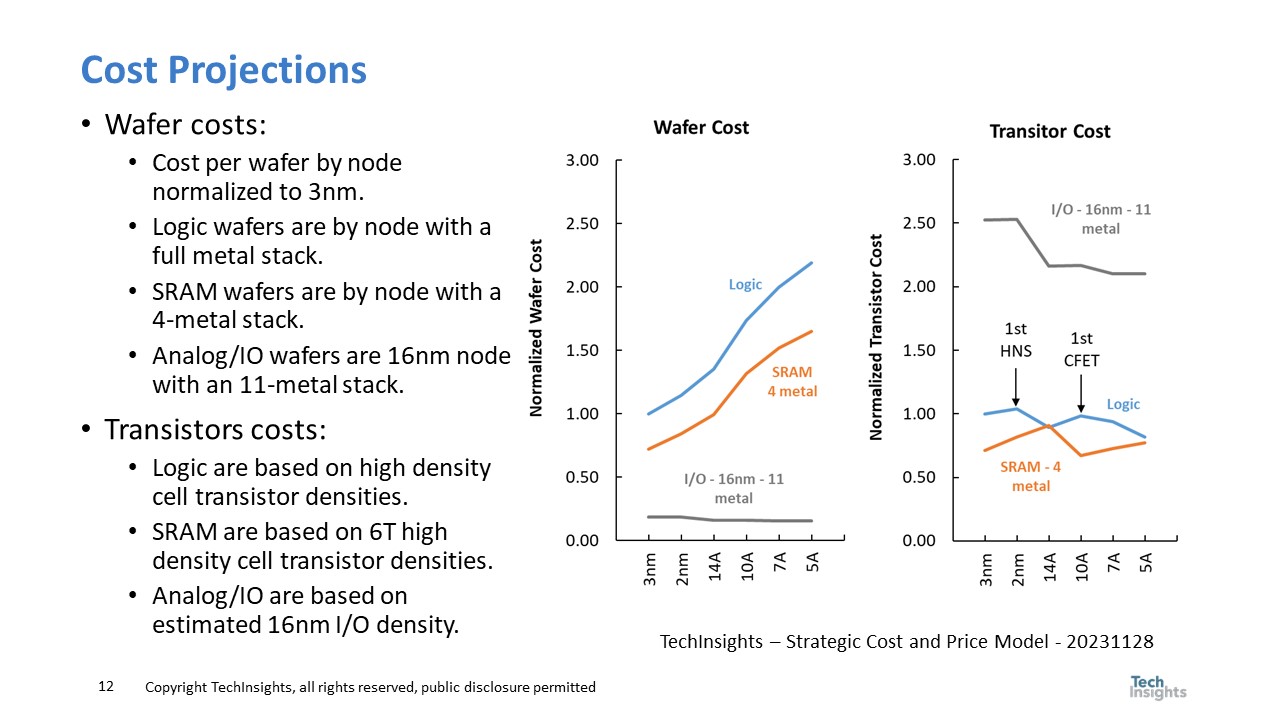

Abbildung 9 zeigt die normalisierten Wafer- und Transistorkosten für Logik, SRAM und I/O (bitte beachten Sie, dass die Abbildung gegenüber der ursprünglichen Darstellung aktualisiert wurde).

In der rechten Abbildung sind die normalisierten Waferkosten dargestellt. Die Kosten für den Logikwafer gelten für einen vollständigen Metallstapel, dessen Anzahl an Metallschichten zunimmt. Bei den SRAM-Wafern handelt es sich um die gleichen Knoten, jedoch sind sie aufgrund des regelmäßigeren Layouts von SRAM auf 4 Metallschichten beschränkt. Die I/O-Wafer-Kosten basieren auf einem 16-nm-11-Metall-Prozess. Ich habe mich für 16 nm entschieden, um einen FinFET-Knoten mit minimalen Kosten zu erhalten und eine angemessene I/O-Leistung sicherzustellen.

Die Abbildung rechts zeigt die in Transistorkosten umgerechneten Waferkosten. Interessanterweise sind die I/O-Transistoren so groß, dass sie selbst auf einem kostengünstigen 16-nm-Wafer die höchsten Kosten verursachen (die I/O-Transistorgröße basiert auf TechInsights-Messungen tatsächlicher I/O-Transistoren). Die Kosten für Logiktransistoren steigen bei 2 nm beim ersten TSMC-HNS-Blechknoten, wo die Schrumpfung gering ist. Wir gehen davon aus, dass die Schrumpfung bei 14 A bei einem HNS-Knoten der zweiten Generation größer sein wird (ähnlich wie TSMC es mit seinem ersten FinFET-Knoten gemacht hat). Auch hier erhöhen die Kosten des ersten CFET-Knotens auch die Transistorkosten für einen Knoten. Die Kosten für SRAM-Transistoren steigen aufgrund begrenzter Kostensenkungen, mit Ausnahme einer einmaligen Kostenreduzierung bei CFETs. Das Fazit dieser Analyse ist, dass die Kostenreduzierung bei Transistoren moderat ausfallen wird, obwohl Chiplets einen einmaligen Vorteil bieten können.

Was die Nachhaltigkeit angeht, erläutert Abbildung 10 die verschiedenen „Umfänge“, aus denen sich der COXNUMX-Fußabdruck zusammensetzt.

Scope 1 sind die direkten Standortemissionen aufgrund von Prozesschemikalien und Verbrennung (Strom kann auch Scope 1 sein, wenn er vor Ort erzeugt wird), Scope 2 ist auf den CO3-Fußabdruck des gekauften Stroms zurückzuführen. Scope XNUMX ist in dieser Analyse nicht enthalten, beruht aber auf dem COXNUMX-Fußabdruck der eingekauften Materialien, der Nutzung des hergestellten Produkts und beispielsweise Fahrzeugen, die von Mitarbeitern eines Unternehmens gefahren werden.

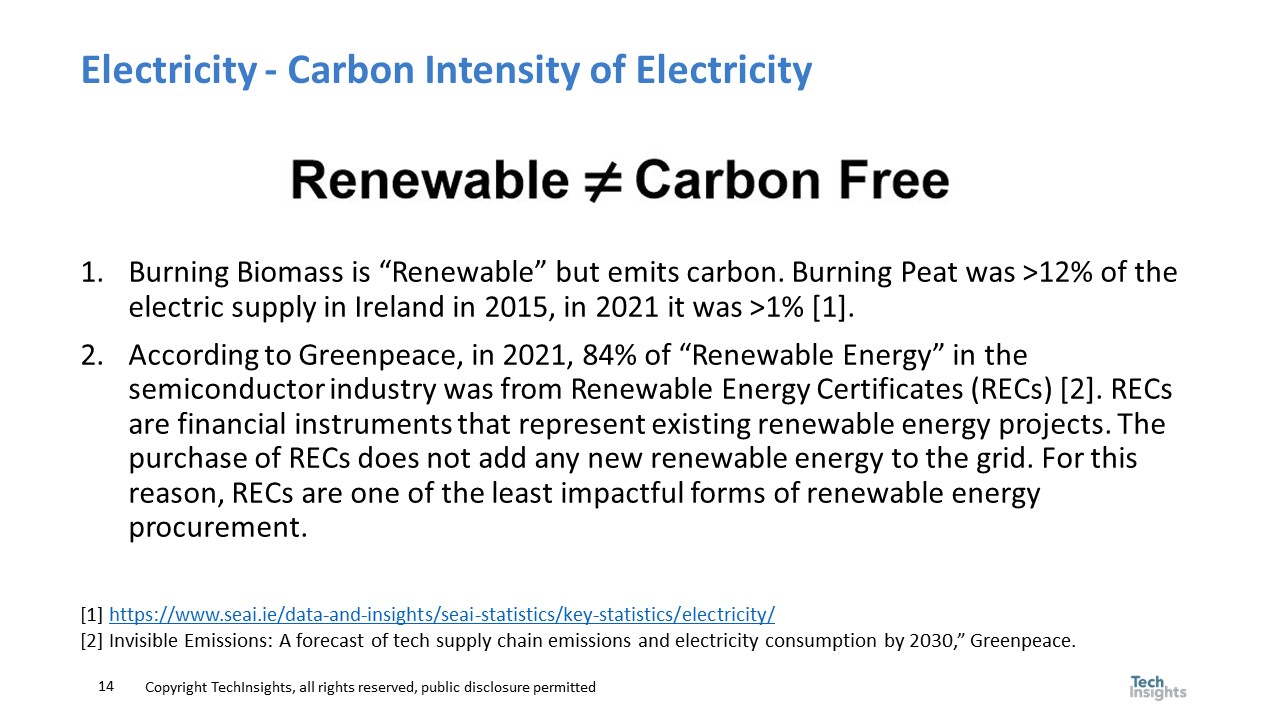

Viele Unternehmen in der Halbleiterindustrie behaupten, dass sie durch Strom keine CO11-Emissionen verursachen, da der Strom vollständig erneuerbar ist. Abbildung XNUMX vergleicht erneuerbare Energien mit kohlenstofffreien Energien.

Das Hauptproblem besteht darin, dass laut Greenpeace 84 % der erneuerbaren Energien in der Halbleiterindustrie im Jahr 2021 Zertifikate für erneuerbare Energien waren, bei denen ein Unternehmen die Rechte erwirbt, um Reduzierungen in Anspruch zu nehmen, die bereits jemand anderes vorgenommen hat. Dies ist nicht dasselbe wie die Installation von kohlenstoffarmen Stromquellen oder die Bezahlung anderer für die Bereitstellung von kohlenstoffarmem Strom und verringert tatsächlich nicht den globalen COXNUMX-Fußabdruck.

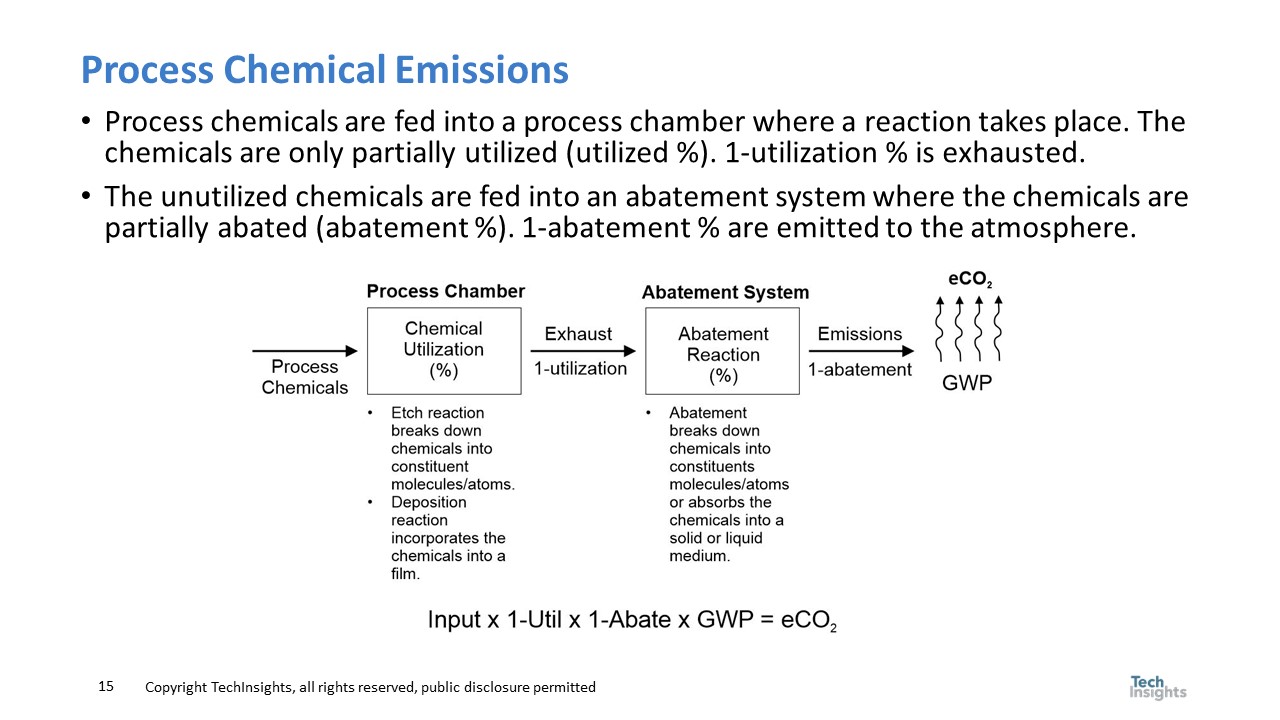

Abbildung 12 zeigt, wie Prozesschemikalienemissionen auftreten und charakterisiert werden.

Prozesschemikalien gelangen in eine Prozesskammer, wo ein Prozentsatz der Chemikalien in einer Ätz- oder Abscheidungsreaktion verwendet wird, die die Chemikalien zersetzt oder in einen abgeschiedenen Film einbaut. 1-Ausbeute ist die Menge an Chemikalien, die aus dem Auspuff des Werkzeugs austritt. Die Abgase des Werkzeugs können dann in eine Abgasreinigungskammer geleitet werden, in der ein Teil der Chemikalien weiter zersetzt wird und die Emissionen aus der Abgasreinigung in die Atmosphäre gleichbleibend sind. Abschließend wird ein Treibhauspotenzial (GWP) herangezogen, um die Kohlenstoffäquivalenz der Emission zu berechnen. Beim GWP wird berücksichtigt, wie lange die Chemikalie in der Atmosphäre verbleibt und wie viel Wärme die Chemikalie im Vergleich zu Kohlendioxid zurückreflektiert. Kohlendioxid hat ein GWP von 1, Halbleiterprozesschemikalien wie SF6 und NF3 haben GWP-Werte von 24,300 bzw. 17,400 (gemäß IPCC AR6).

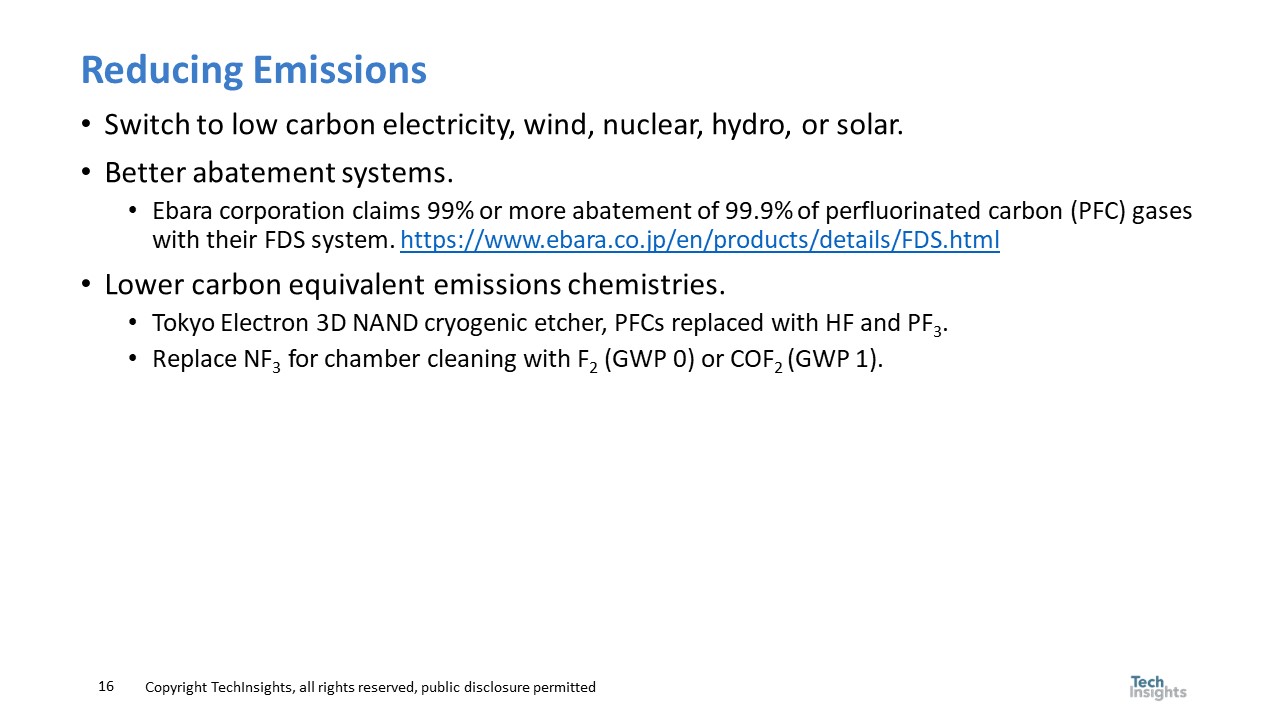

Abbildung 13 stellt einige Möglichkeiten zur Reduzierung der Emissionen vor.

Stromquellen wie Kohle produzieren 820 Gramm CO2 äquivalente Emissionen pro Kilowattstunde (gCO2e/KWh), während Solar-, Wasserkraft-, Wind- und Kernkraft jeweils 48, 24, 12 und 12 gCO2e/KWh erzeugen.

Effizientere Abgasreinigungssysteme können Prozessgase effektiver abbauen. Der Wirkungsgrad der Fab-Minderungssysteme reicht von 0 % für einige gemeldete US-Standorte (keine Minderung) bis zu ~90 %. Wir schätzen, dass der weltweite Durchschnitt von 300-mm-Fabriken etwa 70 % beträgt und dass die meisten Fabriken mit 200-mm-Wafern und kleinerer Wafergröße keine Reduzierung aufweisen. Es stehen Systeme mit einem Wirkungsgrad von bis zu 99 % zur Verfügung.

Es kann auch eine emissionsärmere Chemie verwendet werden. Tokyo Electron hat ein neues Ätzwerkzeug für 3D-NAND angekündigt, das Gase mit einem GWP von Null verwendet. Gase wie SF6 und NF3 werden hauptsächlich verwendet, um Fluor (F) zur Reinigung in Kammern zu transportieren und F zu ersetzen2 (GWP 0) oder COF2 (GWP 1) kann diese Emissionsquelle im Wesentlichen eliminieren.

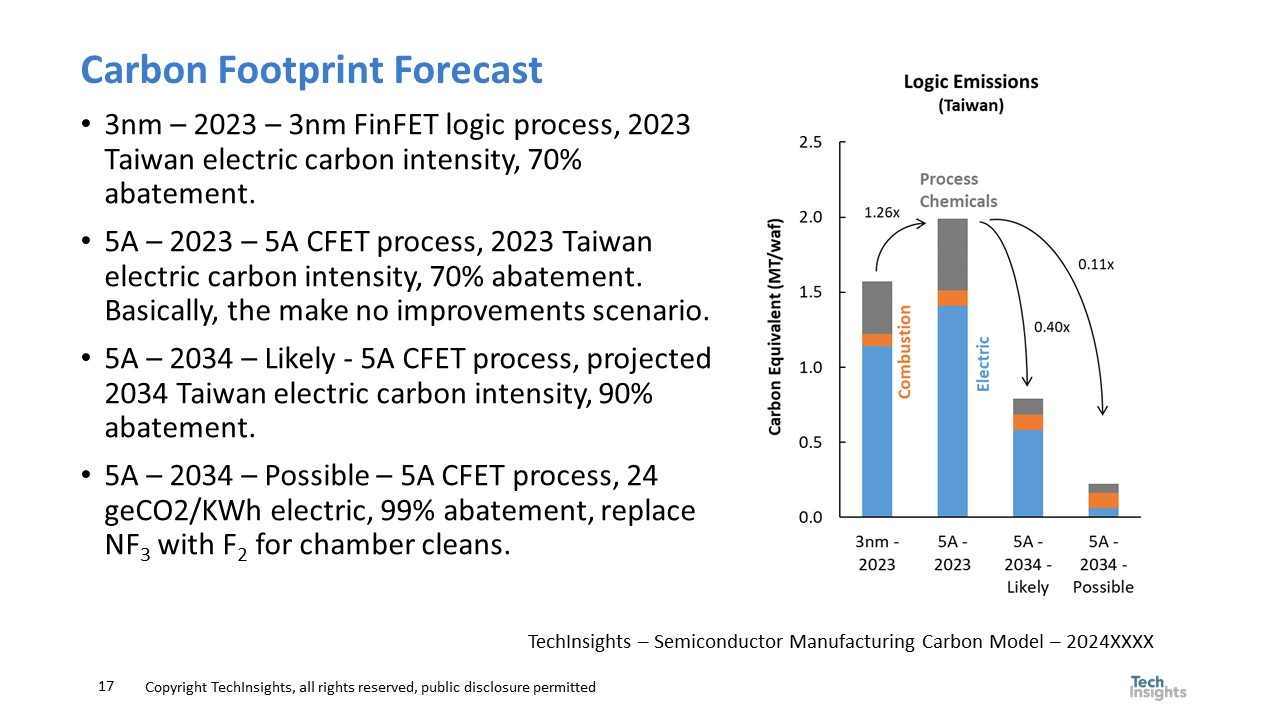

Abbildung 14 zeigt eine COXNUMX-Fußabdruck-Prognose für die Logik.

In der Abbildung ist der erste Balken links ein 3-nm-Prozess, der im Jahr 2023 in Taiwan durchgeführt wurde, unter der Annahme, dass Taiwans CO70-Fußabdruck im Stromsektor und eine Reduzierung um 5 % erreicht werden. Der zweite Balken ist ein 2023A-Prozess und die Emissionen, die sich ergeben würden, wenn die gleiche CO70-Intensität für taiwanesischen Strom im Jahr 1.26 und eine 2034-prozentige Reduzierung verwendet würden. Die Zunahme der Prozesskomplexität würde den Gesamt-Fußabdruck um das 90-fache erhöhen. Mit Blick auf das Jahr 5 wird Taiwans Strom voraussichtlich deutlich dekarbonisiert, außerdem dürfte eine Reduzierung um 2034 % üblich sein, und der dritte Balken zeigt, wie ein 99A-Prozess unter dieser Bedingung aussehen würde. Dies stellt zwar eine Reduzierung der Emissionen um mehr als die Hälfte dar, doch das Wachstum der Zahl der von der Industrie im Jahr XNUMX betriebenen Wafer würde diese Verbesserung wahrscheinlich übertreffen. Der letzte Balken auf der rechten Seite zeigt, was mit ausreichenden Investitionen möglich ist. Er basiert auf kohlenstoffarmem Strom, einer Reduzierung um XNUMX % und der Verwendung von F2 zur Kammerreinigung.

Abbildung 15 zeigt unsere Schlussfolgerungen:

Transistordichte- sowie Wafer- und Chip-Kostenschätzungen wurden mithilfe des TechInsights Strategic Cost and Price Model erstellt, einer Branchen-Roadmap, die Kosten- und Preisschätzungen sowie detaillierte Ausrüstungs- und Materialanforderungen erstellt. Die Schätzungen der Treibhausgasemissionen wurden mithilfe des TechInsights Semiconductor Manufacturing Carbon Model erstellt. Für weitere Informationen wenden Sie sich bitte an sales@techinsights.com

Ich möchte meinen Kollegen in der Reverse Engineering Business Unit bei TechInsights danken. Ihre digitalen Grundrisse und Prozessberichte waren bei der Erstellung dieser Präsentation sehr hilfreich. Außerdem Alexandra Noguera von TechInsights für die Extraktion von Daten zur I/O-Transistorgröße für diese Arbeit.

Lesen Sie auch:

IEDM 2023 – Modellierung der Kohlenstoffemissionen von 300-mm-Waferfabriken

SMIC N+2 im Huawei Mate Pro 60

Teile diesen Beitrag über:

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoData.Network Vertikale generative KI. Motiviere dich selbst. Hier zugreifen.

- PlatoAiStream. Web3-Intelligenz. Wissen verstärkt. Hier zugreifen.

- PlatoESG. Kohlenstoff, CleanTech, Energie, Umwelt, Solar, Abfallwirtschaft. Hier zugreifen.

- PlatoHealth. Informationen zu Biotechnologie und klinischen Studien. Hier zugreifen.

- Quelle: https://semiwiki.com/semiconductor-manufacturers/342094-iss-2024-logic-2034-technology-economics-and-sustainability/