Das Verständnis der elektromagnetischen (EM) Kopplung zwischen verschiedenen Elementen eines Hochfrequenz-Halbleiterbauelements ist für die Einhaltung von Designspezifikationen und die Gewährleistung eines zuverlässigen Betriebs im Feld von entscheidender Bedeutung. Diese EM-Wechselwirkungen umfassen nicht nur den Siliziumchip, sondern erstrecken sich auch auf das Gehäuse, das ihn umschließt. Allerdings kann es sein, dass der IC- oder Systemdesigner erst gegen Ende eines Projekts dazu kommt, EM-Modelle zu erstellen und zu simulieren, die sowohl die Metalle auf dem Chip als auch die Gehäuseschichten umfassen. Es ist nicht ungewöhnlich, dass die Einbeziehung der Gehäuseschichten in das On-Die-Metallmodell zu einer Verschlechterung der Leistung führt, die zu einer Verletzung von Spezifikationen führen kann. Um dies zu vermeiden, bietet Ansys eine Lösung, mit der dem Metallaufbau einer Siliziumtechnologie problemlos Gehäuseschichten hinzugefügt werden können, um frühzeitig im Designprozess vollständige Modelle mit On-Silicon- und Gehäuseschichten zu extrahieren.

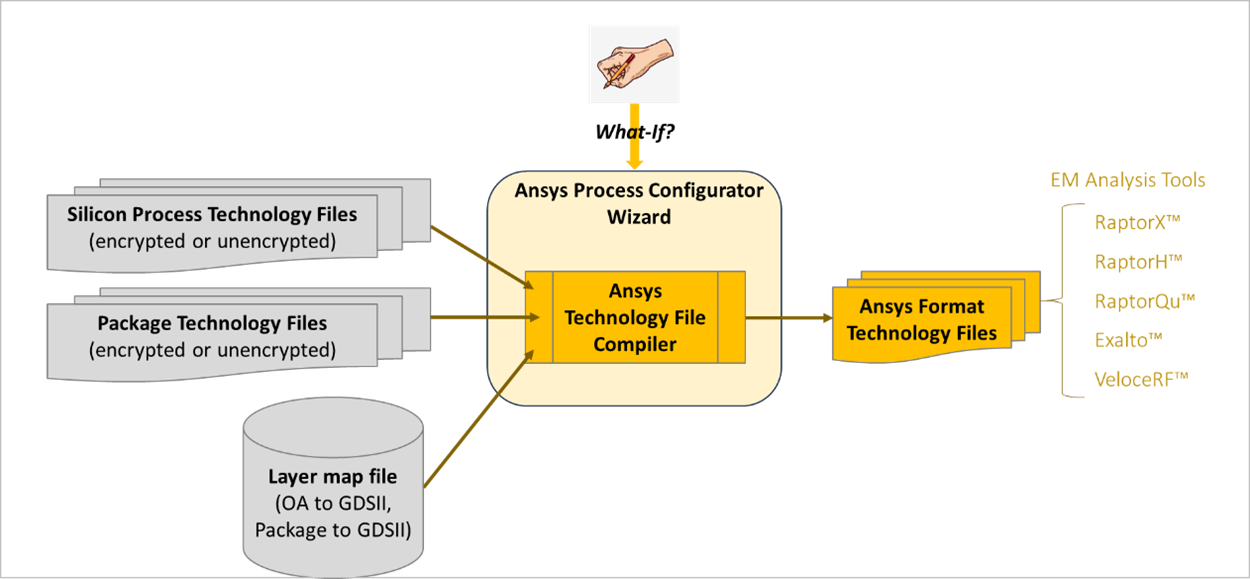

Die On-Chip-Tools zur elektromagnetischen Analyse von Ansys bearbeiten IC-Layouts in der Entwurfsphase vor LVS (Ansys RaptorX™) und die Post-LVS-Signoff-Phase (Ansys Exalto™). Die Chipanalyse kann Teile des Gehäuselayouts und/oder der Gehäuseschichten umfassen, um ein vollständiges EM-Modell zu extrahieren, das mit einem SPICE-Schaltkreissimulator simuliert werden kann. Die Ansys-Tools basieren auf präzisen Informationen über die Verbindungstechnologie, die bei der Herstellung jeder Schicht verwendet wird. Prozessinformationen werden von Siliziumgießereien in verschiedenen Formaten bereitgestellt, darunter Design Rule Manuals (DRMs) und Technologiedateien – wie iRCX-, ITF- und ICT-Dateien – die unverschlüsselt oder verschlüsselt sein können. Der Prozess zur Erfassung des Technologie-Stack-Ups stellt eine Sammlung von Technologiedateien im Ansys-Format zusammen, indem vom Hersteller bereitgestellte Prozesstechnologieinformationen auf physische Layoutinformationen im OpenAccess- oder GDSII-Stream-Format abgebildet werden (siehe Abbildung 1). Diese kompilierten Technologiedateien unterstützen auch andere On-Chip-EM-Tools von Ansys, einschließlich Ansys VeloceRF™ (Synthese des induktiven Gerätelayouts) und Ansys RaptorQu™ (für supraleitendes Quantendesign).

RaptorX ist ein siliziumoptimierter elektromagnetischer Solver und verfügt über einen sehr nützlichen Assistenten namens Process Configurator, der das Erstellen und Ändern von Ansys-Technologiedateien auch für komplexe Chip-Package-Konfigurationen einfach macht. Wie in Abbildung 1 dargestellt, erstellt Process Configurator Ansys-Technologiedateien, die nur den Gießereimetall-Stapel oder den Gießereimetall-Stapel sowie ausgewählte zusätzliche Paketschichten enthalten können. Die Eingabe für den Prozesskonfigurator-Assistenten für den Gießerei-Metallstapel sind die von der Gießerei bereitgestellten Prozessinformationen. Wenn Chip- und Gehäuseschichten gemeinsam extrahiert werden müssen, müssen auch die Paketschichtinformationen für die interessierenden Schichten enthalten sein.

Wenn die Foundry-Technologiedatei unverschlüsselt ist oder die Paketschichtinformationen unverschlüsselt sind, können Sie mit dem Process Configurator-Assistenten verschiedene prozessbezogene „Was-wäre-wenn“-Szenarien erkunden, indem Sie die Eigenschaften der Chip- und/oder Paketschichten bearbeiten und verschiedene Versionen kompilieren der Ansys-Technologiedateien. Mit dem Prozesskonfigurator können Designer Substrate, Rückwandplatinen, Leiter, Dielektrika und Durchkontaktierungen, einschließlich Through-Silicon Vias (TSV), hinzufügen oder entfernen. Die Technologieeigenschaften, die mit Process Configurator bearbeitet werden können, sind Metalldicke, Metallleitfähigkeit, dielektrische Dicke und Dielektrizitätskonstante. Um die Ansys-Technologiedateien zu vervollständigen, benötigt der Compiler auch die GDS-Stream-Layer-Map-Datei und die Layer-Mapping-Informationen.

Einige Beispiele für die Modifizierung einer unverschlüsselten Technologie für „Was-wäre-wenn“-Experimente sind:

- Modifizieren der Substratdicke und -eigenschaften, um die Auswirkungen der Kopplung durch das Substrat zu untersuchen

- Hinzufügen von TSVs in einem explorativen 3DIC-Stackup

- Erstellen einer Technologiedatei für die Wafer-on-Wafer (WoW)-Technologie

Fügen Sie Paketebenen hinzu, um deren Auswirkungen auf das EM-Gerät zu sehen – wie im folgenden Beispiel gezeigt wird

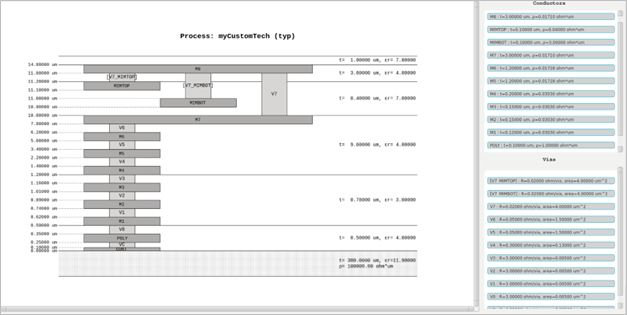

Die Eingabedateien und Informationen für Process Configurator können sowohl über eine Benutzeroberfläche als auch über ein Befehlsskript im Batch-Modus verarbeitet werden. Die Ausgaben von Process Configurator sind die kompilierten Ansys-Prozesstechnologiedateien, die von der Ansys EM-Tool-Suite verwendet werden. Der Prozesskonfigurator verfügt über die sehr nützliche Fähigkeit, einen Technologiequerschnitt zu visualisieren, wodurch die korrekte Reihenfolge und Konnektivität der Technologieebenen leicht überprüft werden kann. Auch unverschlüsselte Technologieschichteigenschaften wie Dicke, spezifischer Widerstand und Dielektrizitätskonstante werden im Querschnittsviewer angezeigt. Wenn die Technologie verschlüsselt ist, zeigt der Querschnittsbetrachter die Schichtfolge und Konnektivität an, aber die Schichtdicken sind nicht maßstabsgetreu und Materialeigenschaften werden nicht gemeldet.

Abbildung 2 unten zeigt einen Stapel einer fiktiven Beispiel-Technologiedatei. Das linke Feld zeigt die Substrateigenschaften auf der unteren Schicht, die kumulative Schichthöhe ausgehend vom Substrat, die Schicht- und Via-Namen auf der linken Seite sowie die dielektrische Dicke und Dielektrizitätskonstante (zr) auf der rechten Seite. Der Abschnitt „Leiter“ im rechten Bereich listet die Leiter mit ihrer Dicke und ihrem spezifischen Widerstand (r) auf, und der Abschnitt „Durchkontaktierungen“ zeigt den Widerstand und die Fläche der Durchkontaktierung an.

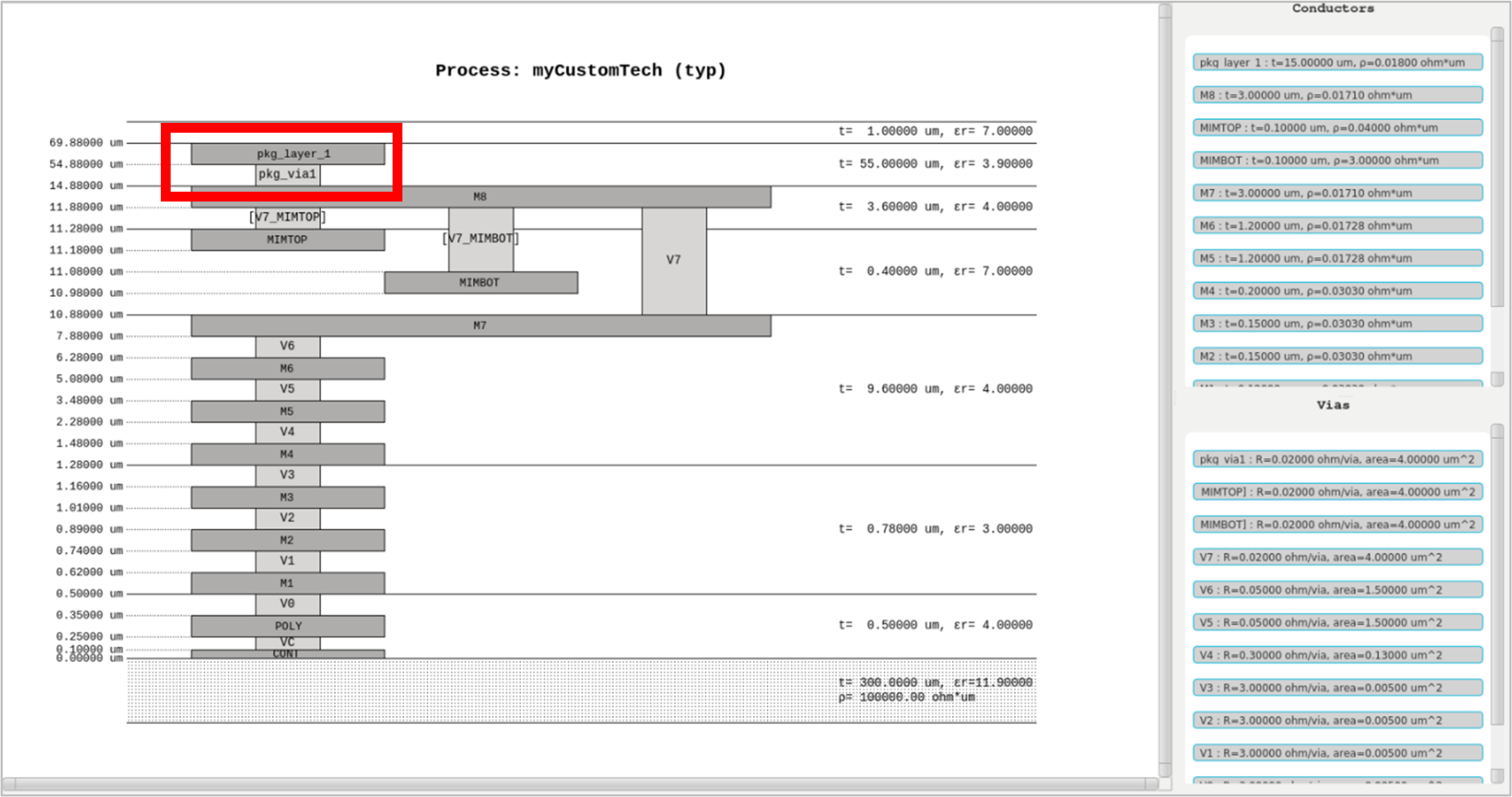

Das rote Kästchen in Abbildung 3 unten hebt eine Durchkontaktierung und eine Paketschicht hervor, die dem Stapel hinzugefügt wurden. Dieser Aufbau, einschließlich der Gehäuseschicht und der Durchkontaktierung, wurde für die in den folgenden Abschnitten beschriebenen Simulationsergebnisse verwendet, die zeigen, wie sich die Gehäuseschicht auf die Leistung eines EM-Geräts auswirken kann.

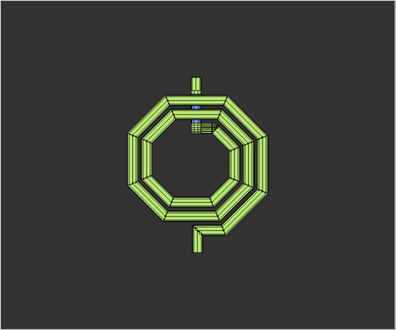

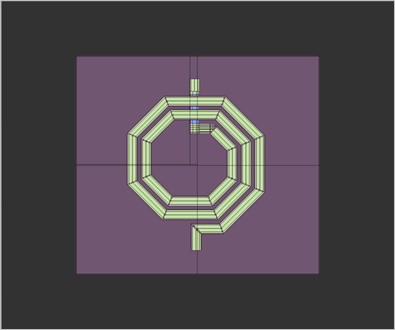

Um zu veranschaulichen, wie Process Configurator verwendet werden kann, um die Wirkung eines Gehäuses auf einem Chip zu untersuchen, haben wir ein einfaches Layoutbeispiel erstellt: Es besteht aus einem EM-Gerät – einem achteckigen Spiralinduktor mit einem Ende – der mit RaptorX extrahiert wurde. Das resultierende elektrische Modell wurde dann in einem Schaltungssimulator auf SPICE-Ebene simuliert, um die Leistung zunächst mit und dann erneut ohne darüber platzierte Gehäuseschicht zu analysieren. Abbildung 4 unten zeigt das physische Netz von RaptorX für den Induktor ohne die Paketschicht.

Als nächstes wurde derselbe Induktor verwendet, aber darüber wurde ein Rechteck der Paketschicht platziert. Abbildung 5 unten zeigt das RaptorX-Netz des Induktors einschließlich der Paketschicht.

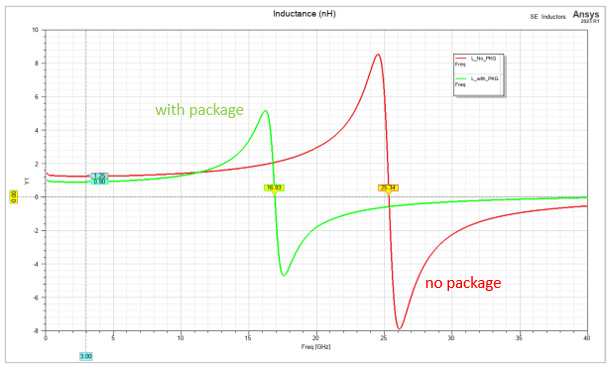

RaptorX generierte für jeden Induktor ein S-Parameter-Modell, das dann für Induktivität und Qualitätsfaktor über einen Frequenzbereich hinweg simuliert wurde. Abbildung 6 zeigt die Induktivität der beiden Induktoren im Diagramm über der Frequenz. Ein Vergleich des Diagramms der Induktivität bei 3 GHz für die enthaltene Gehäuseschicht (grün) zeigt eine Abnahme der Induktivität um 28 % und eine Verringerung der Resonanzfrequenz um 33 % im Vergleich zu den Simulationsergebnissen für das Modell ohne die Gehäuseschicht (rot).

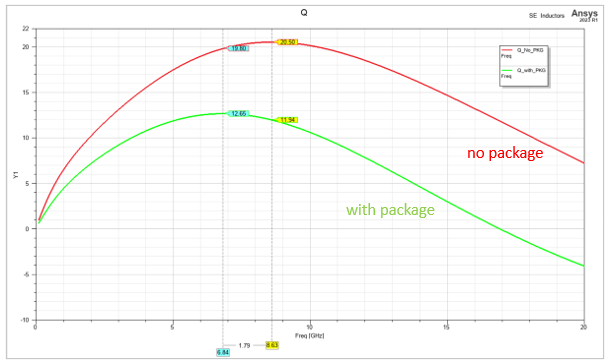

In Abbildung 7 unten ist der Qualitätsfaktor (Q) der beiden Induktoren über der Frequenz aufgetragen. Ein Vergleich des Simulationsdiagramms von Q für die enthaltene Paketschicht (grün) zeigt einen Rückgang des maximalen Q-Werts um 38 % und einen Rückgang der maximalen Q-Spitzenfrequenz um 21 % im Vergleich zu den Simulationsergebnissen für das Modell ohne die Paketschicht (rot).

Zusammenfassend veranschaulichen diese Simulationsergebnisse die starken Änderungen im Geräteverhalten, die auftreten, wenn Paketschichten in eine Simulation einbezogen werden. Die Modellierung von Gehäuseschichten zusammen mit On-Die-Metallen kann Leistungseinbußen aufdecken, die möglicherweise gegen eine Spezifikation verstoßen oder zum Ausfall des Geräts führen können. Ansys hat den Process Configurator entwickelt, um IC- und Systemdesignern die Erfassung selbst der komplexesten mehrschichtigen Verpackungskonfigurationen sehr einfach zu machen und schnelles Experimentieren zu ermöglichen. Es fördert einen Shift-Left-Ansatz mit frühzeitiger Was-wäre-wenn-Erkundung, um Designern dabei zu helfen, die bestmögliche Lösung für die Optimierung ihres Endprodukts zu finden und Überraschungen in der Spätphase zu vermeiden.

Lesen Sie auch:

Teile diesen Beitrag über:

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoData.Network Vertikale generative KI. Motiviere dich selbst. Hier zugreifen.

- PlatoAiStream. Web3-Intelligenz. Wissen verstärkt. Hier zugreifen.

- PlatoESG. Kohlenstoff, CleanTech, Energie, Umwelt, Solar, Abfallwirtschaft. Hier zugreifen.

- PlatoHealth. Informationen zu Biotechnologie und klinischen Studien. Hier zugreifen.

- Quelle: https://semiwiki.com/eda/340090-will-the-package-kill-my-high-frequency-chip-design/