Die nächste Designrevolution steht eindeutig vor der Tür. Das traditionelle Mooresche Gesetz verlangsamt sich, die exponentielle Nachfrage nach Innovation und Formfaktordichte jedoch nicht. Wenn Sie mit einem einzelnen monolithischen Chip nicht mehr zurechtkommen, ist die Umstellung auf einen Multi-Die-Ansatz die Lösung. Diese neue Designmethodik bringt viele Herausforderungen mit sich – lieferkettenorientiert, materialorientiert und standardorientiert, um nur einige zu nennen. Es gibt vielversprechende Innovationen von EDA, IP und Standardisierungsorganisationen. Über all dieser Arbeit zu sitzen, ist eine erhebliche Herausforderung. Welche Optionen sind bei so vielen Optionen zur Implementierung neuer Siliziumsysteme auf Systemebene die besten? 2.5D, 3D, Technologieauswahl, IP/Chiplet-Auswahl und so weiter. Dies ist ein ärgerliches Problem, da der Start mit den falschen Optionen zu enormen Kosten- und Termineinbußen führen kann. Das Problem wurde als bezeichnet Wegfindung, und das ist das Thema dieses Beitrags. Lesen Sie weiter, um zu erfahren, wie MZ Technologies Multi-Die-Design Wirklichkeit werden lässt.

Über MZ Technologies

Ich habe die Wegfindung erwähnt. In diesem Kontext bezieht sich der Begriff auf die Ermittlung der optimalen Technologieauswahl zur Implementierung eines 2.5D- oder 3D-Multi-Die-Designs. Das Problem besteht schon eine ganze Weile. Hier ist eine Diskussion darüber aus dem 2009 IEEE International Symposium on System-on-Chip. Ich habe auch einige Erfahrung mit diesen Problemen. Etwa zur gleichen Zeit, als ich bei Atrenta war, entwickelten wir ein frühes Tool, um das Pfadfindungsproblem anzugehen. Und später, als ich bei eSilicon war, konnte ich aus nächster Nähe sehen, wie anspruchsvoll 2.5D-Design sein kann.

MZ Technologies wurde 2014 von einem Team führender EDA-, IC- und Package-Co-Design-Experten gegründet. Ziel war es, von Grund auf eine neue Technologie zu entwickeln, um die I/O-Planungs- und Optimierungsphase der physischen Implementierung komplexer integrierter 2.5D- und 3D-Schaltkreise zu bewältigen. Das heißt, das Pfadfindungsproblem lösen. Ein wenig über den Namen des Unternehmens, der eine Abkürzung für Monozukuri ist. Im Japanischen ist „monozukuri“ ein zusammengesetztes Wort aus „mono“, was wörtlich „Dinge“ („Produkte“) bedeutet, und „zukuri“, was „Herstellungsprozess“ oder „Schöpfung“ bedeutet.

Das Unternehmen ist ein europäischer EDA-Anbieter und liefert GENIO™, ein einheitliches Cockpit für 2.5D- und 3D-Chiplet-basiertes Systemdesign. GENIO ist ein Tool, das die bahnbrechende Lücke für das Multi-Die-Design schließt. Es konkurriert nicht mit bestehenden Technologien, sondern verbindet sich mit ihnen, um eine breitere, ganzheitlichere Fähigkeit zu schaffen. Das Tool gab es bereits in mehreren Versionen und wurde in einer Vielzahl von Multi-Chip-Designs eingesetzt. Mehr dazu gleich.

Was MZ Technologies macht

GENIO befasst sich mit der Systemarchitektur und dem gemeinsamen Entwicklungsablauf von ICs und Paketen. Dies ist der Teil des Designprozesses, der normalerweise über vorhandenen Tools und geistigem Eigentum liegt. Es beantwortet kritische Fragen zum besten Implementierungsansatz aus Sicht des Formfaktors, der Energie, der Leistung und der Kosten. Wenn Sie diese Dinge schon früh im Prozess richtig machen, kann dies der entscheidende Faktor für den Erfolg eines komplexen Entwurfs sein. Wenn man mit einem suboptimalen Ansatz beginnt, führt dies zu Nacharbeit, Überschreitungen und einer guten Chance, dass das Projekt scheitert.

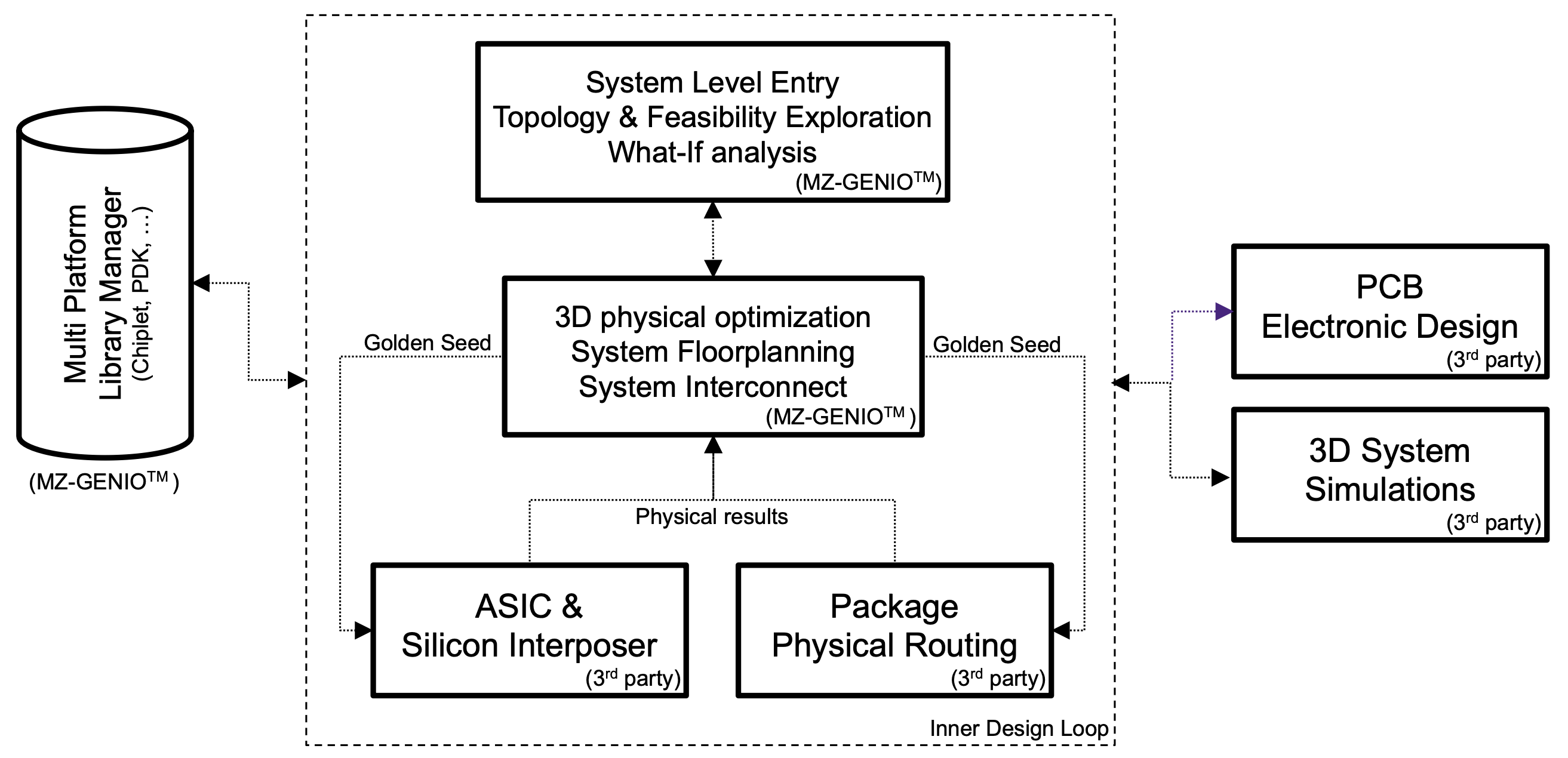

Die folgende Abbildung zeigt, wie GENIO mit vorhandenen Tools in den gesamten Designablauf passt.

Das Tool fügt sich in den Fluss vom Konzept bis zum Design ein, um eine zu liefern Beim ersten Mal richtig optimales Ergebnis. Ziel ist es, eine bessere Herstellbarkeit bei optimaler Ressourcennutzung und besserem Ertrag zu schaffen. GENIO arbeitet im gesamten Design-Ökosystem vom Silizium über das Gehäuse bis zur Leiterplatte mit integrierten Designabläufen.

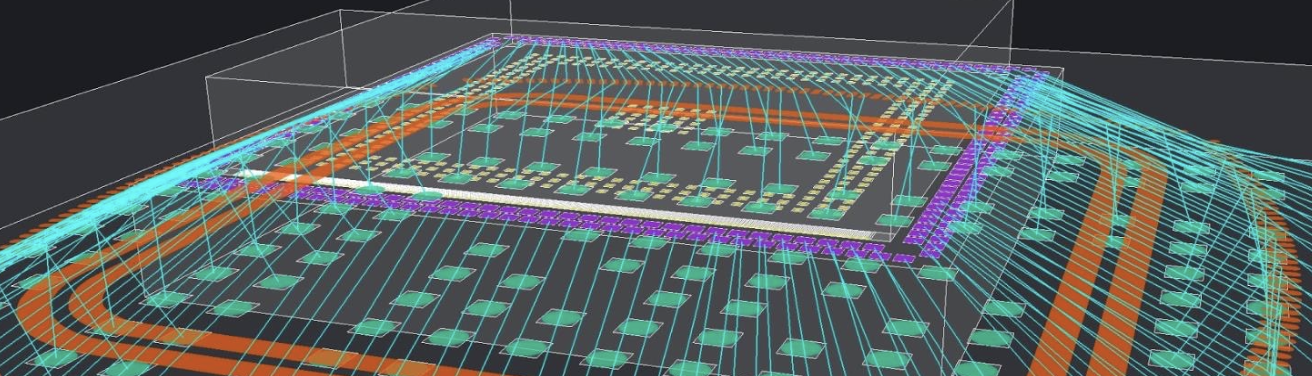

Wenn man etwas tiefer geht, wird die Erkundung der Systemarchitektur für die Planung, Implementierung und Analyse in verschiedenen technischen Bereichen unterstützt. Was-wäre-wenn-Analysen werden für 2D-, 2.5D- und 3D-Verbindungsmanagement, I/O-Planung und Optimierung bereitgestellt. Zum Beispiel planar vs. SI-basiert vs. 3D-Stapel. Die Optimierungsalgorithmen begrenzen die Rechenkomplexität des Multi-Die-Designs. Es werden auch frühe Schätzungen des elektrischen, mechanischen und thermischen Verhaltens bereitgestellt.

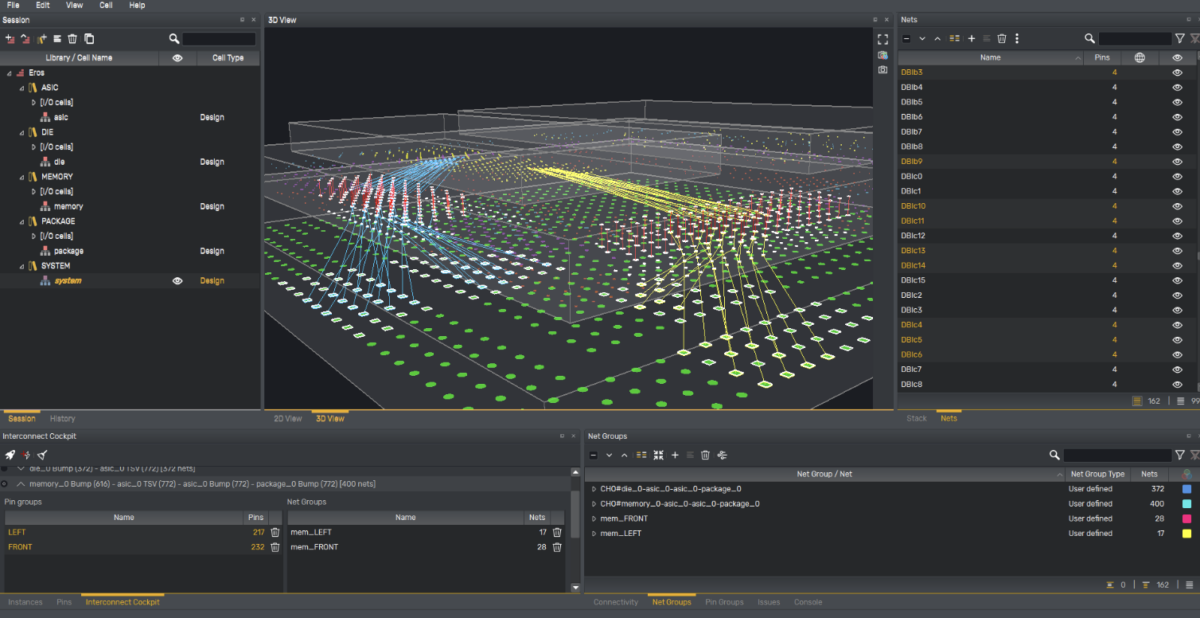

Mit GENIO ist es möglich, die gesamte Systemhierarchie von der obersten Ebene bis hin zu Subsystemen und Komponenten auf einmal zu optimieren. Eine ausgefeilte grafische Benutzeroberfläche ermöglicht unter anderem Cross-Highlight und Scripting sowie die Möglichkeit, in der Designgeschichte zurückzugehen, um die vielversprechendsten Konfigurationen zu kennzeichnen. Die folgende Abbildung zeigt ein Beispiel der GUI.

GENIO hat eine bemerkenswerte Leistung erbracht 60-fache Reduzierung der architektonischen Entwurfszeit. Die folgende Tabelle zeigt die Arten von Designs, auf die GENIO angewendet wurde.

Hier ist eine Zusammenfassung der aktuellen Version und der nächsten Generation des Tools:

GENIO V1.x (heute im Handel erhältlich mit Back-End-Ausrichtung)

- Die umfassende Systemansicht umfasst das gesamte Design-Ökosystem

- Cross-Fabric-Plattform, integriert mit herkömmlichen IC-, Gehäuse- und PCB-Designtools

- Erforschung der Architektur auf Systemebene

- Identifiziert die effizientere und kostengünstigere Option im 3D-Systemangebot

- Einzelner, konsistenter Interconnect Manager

- Darstellung und Pflege des 3D-Modells des gesamten Systems

- Hierarchieübergreifende 3D-bewusste Pfadfindung

- Einschränkungsgesteuerte, proprietäre Optimierungsalgorithmen

- 3D-Chiplet-basierter Designablauf mit mehreren IP-Bibliotheken

- Chip-Stacking und vertikale Silizium-zu-Silizium-Kommunikation – kombinierbare „LEGO-ähnliche“ Montage

GENIO EVO (Nächste Evolution-Version; führt eine simulationsbewusste Optimierung ein)

- Vollständige 3D-Systemansicht über die physische Implementierung und Analyse hinweg

- Superschnelle parasitäre Schätzung für eine frühzeitige Analyse

- Was-wäre-wenn-Analyse vor Beginn der physischen Implementierung

- Hochmoderne TSV-Modellierung

- Einschließlich elektrischer Leistung (R/C) und mechanischem/thermischem Verhalten

- Thermische Modellierung

- Basierend auf der Verlustleistungskarte und dem TSV-Beitrag

- Mechanische Beanspruchung

- Platzierung der Spannungs- und Temperaturüberwachung entsprechend identifizierter thermischer Hotspots

- Kritische Netzgruppenerkennung und Priorisierung

- 3DBlox-Sprachunterstützung

- 3D-System-Partitionierungsablauf

- Unterstützung der Systempartitionierung in den frühen Phasen von RTL und Synthese

- 3D-Stack-Grundrissplanung

- Beste Positionierung der Systemkomponenten/Chiplets über die Stapelebenen hinweg

Um mehr zu lernen

MZ Technologies lizenziert seine Software mit einem zeitbasierten Modell. Zusätzliche Dienste für kundenspezifische Integration, kundenspezifische Modulentwicklung und Kundenschulung sind ebenfalls verfügbar. Wenn Sie vorhaben, ein Multi-Die-Design in Angriff zu nehmen, sollten Sie Kontakt mit ihnen aufnehmen. Ich kann Ihnen aus eigener Erfahrung sagen, dass das Problem, das MZ löst, sehr real ist und zu einem fatalen Fehler werden kann, wenn es nicht frühzeitig angegangen wird. Sie erreichen uns unter info@monozukuri.eu. Und so verwirklicht MZ Technologies das Multi-Die-Design.

Lesen Sie auch:

Ausblick 2024 mit Anna Fontanelli, Gründerin und CEO von MZ Technologies

CEO-Interview: Anna Fontanelli von MZ Technologies

Teile diesen Beitrag über:

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoData.Network Vertikale generative KI. Motiviere dich selbst. Hier zugreifen.

- PlatoAiStream. Web3-Intelligenz. Wissen verstärkt. Hier zugreifen.

- PlatoESG. Kohlenstoff, CleanTech, Energie, Umwelt, Solar, Abfallwirtschaft. Hier zugreifen.

- PlatoHealth. Informationen zu Biotechnologie und klinischen Studien. Hier zugreifen.

- Quelle: https://semiwiki.com/eda/mz-technologies/342224-how-mz-technologies-is-making-multi-die-design-a-reality/