Bei der 3D-IC-Chipdesign-Methode (Three-dimensional Integrated Circuit) werden Chiplets oder Wafer vertikal übereinander gestapelt und mithilfe von Through Silicon Vias (TSVs) oder Hybrid-Bonding verbunden.

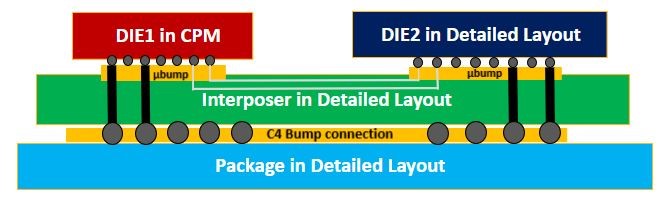

Bei der 2.5D-IC-Designmethode werden mehrere Chiplets nebeneinander auf einem Silizium-Interposer platziert. Mikrobumps und Verbindungsdrähte stellen Verbindungen zwischen Chips her, während TSVs verwendet werden, um Verbindungen mit dem Gehäusesubstrat herzustellen.

Warum brauchen wir 3D-ICs?

Neue Technologien wie künstliche Intelligenz, maschinelles Lernen und Hochgeschwindigkeitsrechnen erfordern hochfunktionale, schnelle und kompakte ICs. Die 3D-IC-Designtechnologie bietet ultrahohe Leistung und reduzierten Stromverbrauch und eignet sich daher für Multi-Core-CPUs, GPUs, Hochgeschwindigkeits-Router, Smartphones und KI/ML-Anwendungen. Mit der Weiterentwicklung der High-Tech-Industrie wächst der Bedarf an kleinerer Größe und mehr Funktionalität. Die heterogene Integrationsfähigkeit des 3D-IC-Designs sorgt für mehr Funktionsdichte auf kleinerer Fläche. Die vertikale Architektur von 3D-ICs reduziert außerdem die Verbindungslänge und ermöglicht so einen schnelleren Datenaustausch zwischen den Chips. Insgesamt ist diese fortschrittliche Verpackungstechnologie eine dringend benötigte IC-Designmethode, um der wachsenden Nachfrage nach Geschwindigkeit, mehr Funktionalität und weniger Stromverbrauch gerecht zu werden.

Vorteile von 3D-ICs

Ein wesentlicher Vorteil von 3D-ICs ist heterogene Integration. Es ermöglicht die Integration von Chiplets in verschiedene Technologieknoten auf demselben Raum. Digitale Logik, analoge Schaltkreise, Speicher und Sensoren können in einem einzigen Gehäuse untergebracht werden. Dies ermöglicht die Erstellung hochindividueller und effizienter Lösungen, die auf spezifische Anwendungsanforderungen zugeschnitten sind.

Höhere Integrationsdichte ist ein weiterer Vorteil des 3D-IC-Designs. Durch die vertikale Stapelung mehrerer Schichten miteinander verbundener Chiplets oder Wafer wird die verfügbare Chipfläche effizienter genutzt. Diese erhöhte Integrationsdichte ermöglicht die Integration von mehr Funktionalität auf kleinerem Raum, was besonders bei Anwendungen von Vorteil ist, bei denen Größen- und Gewichtsbeschränkungen von entscheidender Bedeutung sind, wie z. B. mobile Geräte und IoT-Geräte.

Auch 3D-ICs sind vertreten höhere elektrische Leistung. Die reduzierte Verbindungslänge in vertikal gestapelten Chips führt zu kürzeren Signalpfaden und geringerem Widerstand, was zu einer verbesserten Signalintegrität und einer geringeren Signalverzögerung führt. Dies führt zu höheren Datenübertragungsraten, einem geringeren Stromverbrauch und einer verbesserten Gesamtsystemleistung.

Mit den neuesten Konfigurationsmethoden wie CoWoS (Chip On Wafer on Substrate) und WoW (Wafer on Wafer) von TSMC, die Hybrid-Bonding-Techniken nutzen, wird die Verbindungslänge weiter minimiert, was zu geringeren Leistungsverlusten und einer verbesserten Leistung führt.

Die 3D-IC-Technologie bietet eine Reihe außergewöhnlicher Vorteile, darunter heterogene Integration, höhere Integrationsdichte, geringere Größe, höhere elektrische Leistung, geringere Kosten und schnellere Markteinführung. Diese Vorteile machen 3D-ICs zu einer überzeugenden Lösung für anspruchsvolle Chipdesigns in verschiedenen Branchen.

Herausforderungen des 3D-IC-Designs

Obwohl 2.5D/3D-IC-Designmethoden zahlreiche Vorteile bieten, haben diese neuen Methoden auch neue physikalische Herausforderungen mit sich gebracht. Die strukturelle, thermische, Leistungs- und Signalintegrität des gesamten 3D-IC-Systems ist komplizierter. 3DIC-Designer stehen am Anfang der Lernkurve, um die Integritätsherausforderungen während der physischen Implementierung des Systems zu meistern. Genaue Simulationsmethoden sind ein Muss für jeden Chipdesigner, insbesondere wenn es um 3D-IC geht. Jede Komponente im 3D-IC-System sollte mit hochpräzisen Simulationstools untersucht und validiert werden.

Erfahren Sie mehr über die neuesten Entwicklungen im 3D-IC-Design, Herausforderungen und Simulation sowie den Schlüssel zu einem erfolgreichen 3D-IC-Design, indem Sie sich für dieses Webinar anmelden. Design und Analyse von Multi-Die- und 3D-IC-Systemen von Ansys-Experten. Er wird auch die fortschrittlichen Simulationsmethoden zur Vorhersage möglicher struktureller, thermischer, Leistungs- und Signalintegritätsprobleme in 3D-IC diskutieren.

Lesen Sie auch:

Chiplet-Fragen und Antworten mit John Lee von Ansys

Multiphysik-Analyse vom Chip zum System

Checkliste, um sicherzustellen, dass Silizium-Interposer Ihr Design nicht zerstören

Teile diesen Beitrag über:

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- EVM-Finanzen. Einheitliche Schnittstelle für dezentrale Finanzen. Hier zugreifen.

- Quantum Media Group. IR/PR verstärkt. Hier zugreifen.

- PlatoAiStream. Web3-Datenintelligenz. Wissen verstärkt. Hier zugreifen.

- Quelle: https://semiwiki.com/eda/ansys-inc/330137-webinar-revolutionizing-chip-design-with-2-5d-3d-ic-design-technology/