Ich habe kürzlich mit Frank Schirrmeister (Solutions & Business Development, Arteris) über den Stand der Fortschritte auf dem Weg zum offenen Chiplet-Ideal gesprochen. Sie wissen schon – wo ein Multi-Die-System im Paket mit UCIe- (oder anderen) Verbindungen zusammengestellt werden kann, die den Datenfluss zwischen den Chips nahtlos verbinden. Wenn künstliche allgemeine Intelligenz und Quantencomputing im industriellen Maßstab unmittelbar vor der Tür stehen, sollten dann doch alle verbleibenden Probleme beim offenen Chiplet-Design im Handumdrehen gelöst werden? Laut Frank lautet die Antwort ja und nein. Für einige privilegierte Gruppen ist alles möglich und wird heute in die Tat umgesetzt. Für größere offene Märkte nicht so sehr, zumindest nicht auf kurze Sicht.

Mit freundlicher Genehmigung von Arterien

Multi-Die-Systeme und proprietäre Lösungen

Multi-Die-Systeme erfüllen die nie endende Nachfrage, größere und komplexere Systeme zu bauen (z. B. für die LLM-Verarbeitung), wenn sie durch eine Reihe von Halbleiterbeschränkungen eingeschränkt werden: Sie können nur eine bestimmte Menge Logik auf einem Die unterbringen; Einige Funktionen wie Analog und DRAM funktionieren am besten in Prozessen, die für die Logik nicht optimal sind. Und selbst wenn man irgendwie mehr auf einen einzelnen Chip unterbringen könnte, würde die Ausbeute sinken und die Kosten würden in die Höhe schnellen.

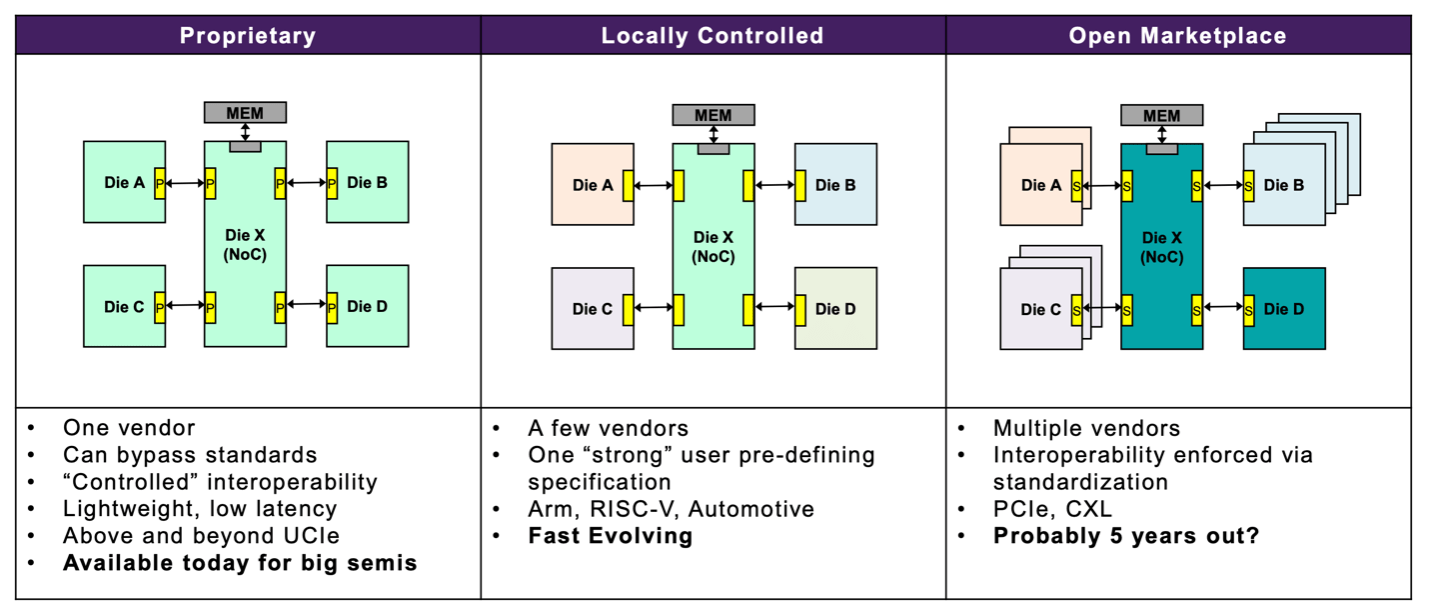

Im letzten Jahr oder so haben Intel, AMD und Nvidia alle Prozessorprodukte auf Basis von Chiplet-Architekturen herausgebracht. Das Besondere an diesen Produkten in diesem Zusammenhang ist, dass diese Unternehmen jeweils alle ihre Chiplets selbst gebaut haben, zusammen mit der Infrastruktur und Konnektivität, die sie zu einem vollständigen Multi-Die-System zusammenfügt. Sie sind nicht von externen Chiplet-Anbietern oder externen IP-Anbietern für die Chiplet-zu-Chiplet-Kommunikation abhängig. Indem sie alles intern kontrollieren und ihre Lieferanten entsprechend anleiten, können sie die Systeme, die sie intern entwickelt haben, anhand ihrer eigenen umfangreichen Testreihen abstimmen und validieren. Einige andere sehr große vertikal integrierte Unternehmen könnten ebenfalls in diese Klasse fallen. Mir wurde gesagt, dass Meta nun einer davon sein könnte, und ich wäre überrascht, wenn Apple nicht auch das gesamte Multi-Die-Design selbst übernehmen würde.

Für alle anderen, die ein Multi-Die-System aufbauen möchten, ist das alles interessant, stellt aber dennoch einen Machbarkeitsnachweis dar. Funktioniert sehr gut für Intel, AMD und Nvidia, aber für Systementwickler, die nicht über dieses Maß an Kontrolle verfügen, ist mehr erforderlich. Während sich UCIe (neben anderen Optionen) grundsätzlich um die Kommunikation von Sterben zu Sterben kümmern sollte, deutet die Realität darauf hin, dass die Herausforderung noch nicht gemeistert ist.

Übrigens gibt es auch einen parallelen Trend; Leiterplatten (PCBs) werden immer kleiner. Hier hat die Branche viele verschiedene Arten von Verpackungsansätzen gesehen, und Benutzer sind es gewohnt, mehrere Chips auf Substraten für Designs zu integrieren, die die oben erwähnte Retikelgrenze nicht in Frage stellen. Beide Trends laufen bei Chiplets zusammen, wenn auch mit unterschiedlichen Designmethodik-Ansätzen – miniaturisierte PCBs vs. gemeinsam entworfene oder interoperable nackte Siliziumstücke.

Offene Chiplets und interoperable Kommunikationsschnittstellen

Theoretisch sollte die Verwendung von Standards wie UCIe für die Kommunikation zwischen Chips Kommunikationsprobleme zwischen Chips lösen, was für die Ermöglichung eines echten offenen Chiplet-Ökosystems unerlässlich ist. Wenn dies wie angekündigt funktioniert, sollten Chiplets auch dann kommunizieren können, wenn sie von verschiedenen Chiplet-Anbietern stammen, in verschiedenen Gießereien hergestellt werden usw. Leider erweist sich die Einhaltung des Standards als notwendige, aber unzureichende Bedingung, um die Interoperabilität zwischen zwei Seiten sicherzustellen (sagen wir) ein UCIe-Link. Während die PHYs über Augendiagramme überprüft werden können, gibt es immer noch Unterschiede in der Art und Weise, wie Daten von Protokollen wie AXI und CHI zu Streaming-Schnittstellen wie CXS und von dort zu FDI, der Streaming-Schnittstelle von UCIe, gepackt werden.

Das ist keine Offenbarung. In der PC-Welt, der kabelgebundenen und kabellosen Kommunikation und anderen Bereichen ist die Einhaltung von Standards der erste Schritt. Plugfests zum Nachweis der Interoperabilität zwischen Anbietern in der Praxis sind ein nächster Schritt. Für die Mobilfunkkommunikation benötigen Netzbetreiber detaillierte Interoperabilitätstests anhand ihrer Anforderungen. Es scheint, dass eine ähnliche Infrastruktur für die Chiplet-Kommunikation erforderlich ist, obwohl dies möglicherweise etwas schwieriger ist, da man keinen Stecker in ein Chiplet stecken kann. Frank erzählt mir, dass er gehört hat, dass Pläne in Arbeit sind, aber voraussichtlich nicht so schnell zum Mainstream werden (PCIe hat auch eine Weile gedauert). Die Branche hat erste Fälle von reiner UCIe-Interoperabilität angekündigt, beispielsweise zwischen Intel und Synopsys.

Eine Klasse von Systementwicklern hat eine einfache Antwort auf dieses Problem. Sie sind leistungsstark genug, um ihre Lieferanten zu einer konvergierenden Einhaltung ihrer Designs zu zwingen. Wenn in ihren Anwendungsfällen etwas nicht funktioniert, greifen die potenziell schuldigen Parteien zu und müssen eine Lösung finden. Einige große Automobilhersteller gehören zu dieser Klasse, auch einige große HPC-Unternehmen. Die hier gefundenen Probleme dürften kleine Unterschiede in den Erwartungen an Margen, Pufferung und andere Parameter sein, die im Standard nicht vollständig festgelegt sind. Oder einfach nur Fehler, die in den Anwendungsfalltests von Chiplet-/IP-Anbietern nicht behandelt werden. Was auch immer das Problem ist, die Lieferanten müssen es lösen. Es ist gut, König zu sein, wenn man ein Chiplet-basiertes Design entwickeln möchte.

Für alle anderen

Das heutige Erreichen der Interoperabilität hängt davon ab, wo jede Ihrer Inter-Chip-Verbindungen in der großen und sich ständig weiterentwickelnden Matrix bewährter/abgedeckter Kommunikationspaare unter Berücksichtigung von IP/PHY-Quellen, Spezifikationsunterschieden und Anwendungsfallunterschieden (kohärente versus nicht kohärente Links) angesiedelt ist. . Symmetrische Paare (auf beiden Seiten alles gleich) sollten (?) in Ordnung sein, aber asymmetrische Paare sind ein Glücksspiel, sofern sie nicht in der Produktion nachgewiesen werden. Laut Frank ist diese Herausforderung besonders in der NoC-Welt sichtbar. Er sagt, Kunden fragen, ob das Arteris Nr. C Funktioniert mit einer bestimmten UCIe-Controller-IP. Vernünftige Frage, würde man meinen.

Aber der NoC kommuniziert mit einem Protokoll-zu-Stream-Konverter, der dann mit einem PHY kommuniziert. Die Kommunikation erfolgt über eine Verbindung zu einem PHY auf dem zweiten Chiplet, dann zu einem Stream-zu-Protokoll-Konverter und dann zum NoC auf diesem Chiplet. Alle halten sich voll und ganz an den Standard, aber die Verbindung funktioniert trotzdem nicht – es sei denn, sie funktioniert nachweislich in der Produktion. Viel strengere Interoperabilitätstests werden dieses Problem letztendlich lösen, aber bis dahin kann es noch fünf Jahre dauern. In der Zwischenzeit, Arterien und Kunden füllen Zellen in der Interoperabilitätsmatrix einzeln (oder vielleicht auch mehrere) aus.

Unterm Strich sind Chiplets real, für den vertikal integrierten Systembauer völlig unter Kontrolle, entwickeln sich unter autokratischen Kunden schnell weiter und schreiten für alle anderen langsam voran. Sie können mehr lesen KLICKEN SIE HIER.

Teile diesen Beitrag über:

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoData.Network Vertikale generative KI. Motiviere dich selbst. Hier zugreifen.

- PlatoAiStream. Web3-Intelligenz. Wissen verstärkt. Hier zugreifen.

- PlatoESG. Kohlenstoff, CleanTech, Energie, Umwelt, Solar, Abfallwirtschaft. Hier zugreifen.

- PlatoHealth. Informationen zu Biotechnologie und klinischen Studien. Hier zugreifen.

- Quelle: https://semiwiki.com/chiplet/341582-moderating-our-open-chiplet-enthusiasm-a-noc-perspective/