Die Nachfrage nach Netzwerklösungen mit hoher Bandbreite und geringer Latenz war noch nie so groß. Da die Arbeitsbelastung durch künstliche Intelligenz (KI) weiterhin exponentiell wächst und Hyperscale-Rechenzentren zum Rückgrat unserer digitalen Infrastruktur werden, wird der Bedarf an schnelleren und effizienteren Kommunikationstechnologien immer wichtiger. 1.6T-Ethernet wird 400G- und 800G-Ethernet als Rückgrat von Hyperscale-Rechenzentren schnell ersetzen.

Hyperscale-Rechenzentren, die alles von Cloud Computing und Big-Data-Analysen bis hin zu KI und maschinellem Lernen unterstützen, benötigen Chips und Schnittstellen mit hoher Bandbreite und geringer Latenz, um Petabytes an Daten schnell und effizient zu verarbeiten. Da der Bedarf an Rechenleistung weiter steigt, steigt auch der Energieverbrauch von Rechenzentren. Ein hoher Stromverbrauch durch Verbindungen führt zu einer erhöhten Wärmeerzeugung, was wiederum robustere Kühlsysteme erfordert, um optimale Betriebstemperaturen aufrechtzuerhalten. Durch die Reduzierung des Stromverbrauchs der Verbindungsleitungen wird weniger Wärme erzeugt, die Gesamtenergieeffizienz kann verbessert werden, was zu Kosteneinsparungen und einer geringeren Umweltbelastung führt. Wenn es um KI und Rechenzentrumsinfrastruktur geht, sind neben der Geschwindigkeit vor allem die drei Faktoren Latenz, Leistung und Größe von entscheidender Bedeutung.

Synopsys hat kürzlich die branchenweit erste vollständige 1.6T-Ethernet-IP-Lösung vorgestellt das alle oben genannten Anforderungen erfüllt. Die Gesamtlösung von Synopsys ermöglicht eine Reduzierung der Latenz um bis zu 40 %, eine Reduzierung der Verbindungsleistung um 50 % und eine Flächenreduzierung um 50 % im Vergleich zu bestehenden Lösungen. Sie umfasst ein vorab verifiziertes Subsystem und verschafft Chip-Designern einen Vorsprung.

Komplette Lösung

Die komplette 1.6T-Ethernet-IP-Lösung von Synopsys umfasst eine Reihe innovativer Technologien, die darauf ausgelegt sind, die Leistung zu optimieren, den Stromverbrauch zu senken und die Markteinführungszeit für KI- und HPC-Netzwerkchips zu beschleunigen.

Nachfolgend finden Sie ein kontextbezogenes Zitat von Mick Posner, VP of Product Management, High Performance Computing IP Solutions bei Synopsys.

„Die Siliziumanbieter hinter den Rechenzentrumseinheiten benötigen die Einführung der neuesten Generation von Verbindungsprotokollen, damit sie ihr Silizium für die Skalierung mit neuen Arbeitslasten optimieren können. Und genau hier kommt 1.6 Ethernet ins Spiel.“

Das Anbieten einer vollständigen Ethernet-IP-Lösung für Kunden vereinfacht die Integration, reduziert die Komplexität, optimiert die Leistung, vereinfacht die Bereitstellung, bietet konsistenten Support, ermöglicht Skalierbarkeit und hilft, Risiken zu mindern. Diese Vorteile führen letztendlich zu größerer Kundenzufriedenheit und Erfolg bei der Bereitstellung und Wartung von Ethernet-IP-Netzwerken.

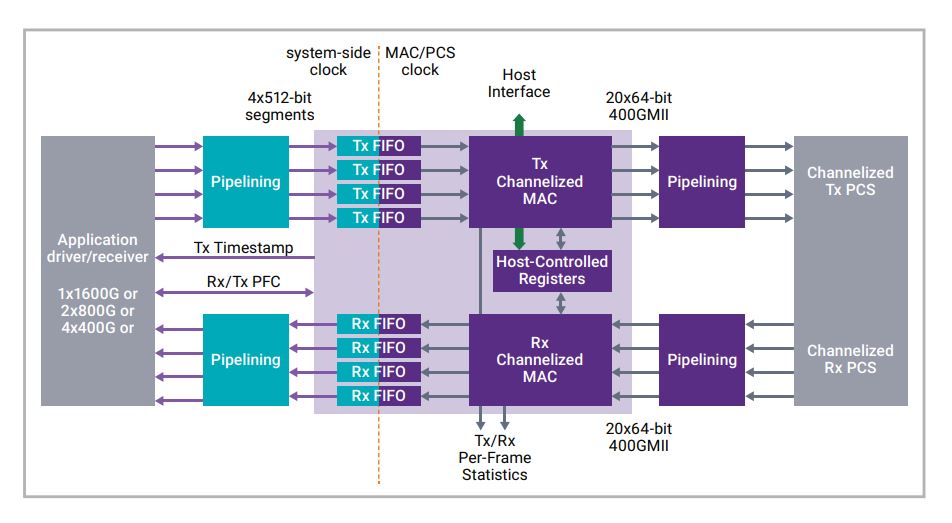

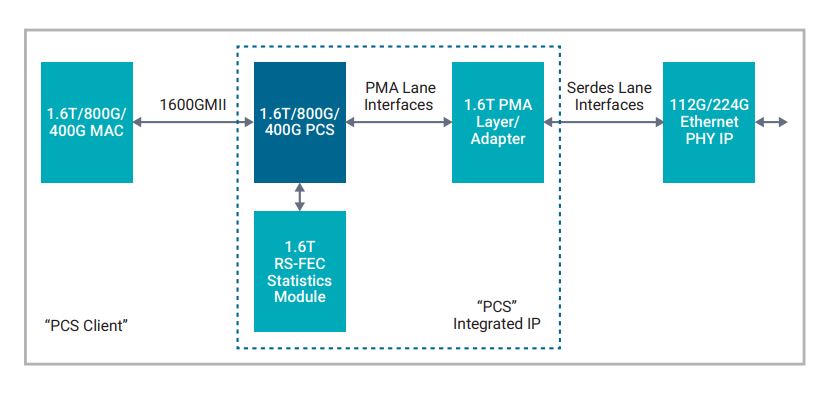

Die Synopsys 1.6T Ethernet IP-Lösung verfügt über neue, optimierte MAC- und PCS-IP

1.6T MAC- und PCS-Ethernet-Controller

Forward Error Correction (FEC)-Mechanismen spielen eine entscheidende Rolle bei der Verbesserung der Zuverlässigkeit der Datenübertragung über Hochgeschwindigkeitsverbindungen, insbesondere im Zusammenhang mit 1.6 Tbit/s-Verkehr. Während FEC dabei hilft, Fehler zu bekämpfen und die Datenintegrität sicherzustellen, führt seine Implementierung zu zusätzlichen Überlegungen wie Fläche, Stromverbrauch und Latenz. Beim Entwurf effizienter Kommunikationssysteme für die 1.6T-Ära ist es unerlässlich, das richtige Gleichgewicht zwischen Bitfehlerrate (BER), Energieeffizienz und Latenz zu finden. Durch die Implementierung einer patentierten Reed-Solomon-FEC-Architektur ist Synopsys in der Lage, die Fläche um 50 % zu verkleinern und die Latenz um 40 % auf dem 1.6-T-Ethernet-MAC und den Mehrkanal-Mehrraten-PCS-Controllern zu reduzieren, ohne die Zuverlässigkeit über Ethernet-Raten von 10 G bis hin zu beeinträchtigen 1.6T.

224G Ethernet PHY IP

Das siliziumerprobte Ethernet-PHY-IP von Synopsys bietet eine robuste Verbindungsleistung mit außergewöhnlicher Signalintegrität und unterstützt Chip-zu-Chip-, Chip-zu-Modul- und Kupferkabelverbindungen. Die anpassbare PHY-IP optimiert Leistungs- und Leistungskompromisse und sorgt für nahtlose Ökosystem-Interoperabilität für mehrere Kanallängen.

Verifizierungs-IP

Die Verifizierungs-IP von Synopsys für Ethernet-Geschwindigkeiten von bis zu 1.6 T verkürzt die Markteinführungszeit, indem sie den Verifizierungsprozess beschleunigt. Die Verifizierungs-IP ist in nativem SystemVerilog und der Universal Verification Methodology (UVM) implementiert und bietet einen umfassenden Satz an Protokollen, Methoden und Produktivitätsfunktionen, die ein zuverlässiges und effizientes Testen von Ethernet-Designs gewährleisten. Als branchenweit erste Ethernet-Verifizierungs-IP für bis zu 1.6T trägt es dazu bei, die Zeit bis zum ersten Test zu verkürzen.

Rückwärtskompatibilität

Die 1.6T IP-Lösung von Synopsys ist abwärtskompatibel mit 400G- und 800G-Ethernet-Lösungen, sodass Benutzer ihre Systeme in ihrem eigenen Tempo aktualisieren oder erweitern können, ohne mit kostspieligen, störenden Änderungen konfrontiert zu werden. Abwärtskompatibilität ist von entscheidender Bedeutung, um Investitionen zu erhalten, reibungslose Übergänge zu gewährleisten und die Interoperabilität von Software, Hardware und Protokollen zu fördern. Indem Benutzern die nahtlose Integration neuer Technologien in bestehende Systeme ermöglicht wird, minimiert die Abwärtskompatibilität der Synopsys-Lösung Unterbrechungen und verkürzt die Lernkurve.

Silizium-zu-Systemdesign-Lösungen

Die Komplettlösung von Synopsys umfasst vorab verifizierte Subsysteme, die es Kunden ermöglichen, ihren Entwicklungsprozess zu rationalisieren und Markteinführungszeiten sowie Entwicklungsrisiken zu reduzieren. Diese von Lieferanten streng getesteten und validierten Subsysteme gewährleisten eine hohe Zuverlässigkeit und die Einhaltung von Industriestandards. Damit können sich Kunden auf ihre Kernkompetenzen konzentrieren und gleichzeitig Skalierbarkeit und Flexibilität genießen. Die beschleunigte Markteinführung steigert die Gesamtrendite der Investition und macht vorverifizierte Subsysteme zu einem wertvollen Aktivposten für die effiziente Produktentwicklung für große, mittlere und kleine Kunden.

Das Synopsys 1.6T Ethernet IP-Lösungssubsystem integriert vorverifizierte MAC, PCS und PHY

Zusammenfassung

Die vollständige 1.6T-Ethernet-IP-Lösung von Synopsys stellt einen bedeutenden Meilenstein in der Entwicklung von Netzwerktechnologien für KI und Hyperscale-Rechenzentren dar. Durch das Angebot innovativer Lösungen, die die Leistung optimieren, die Latenz verringern, den Stromverbrauch reduzieren und die Markteinführung beschleunigen, trägt Synopsys dazu bei, die Zukunft von KI und Hochleistungsrechnen voranzutreiben und es Kunden zu ermöglichen, aktuelle und zukünftige Anforderungen an die meisten Daten zu erfüllen -intensive Arbeitsbelastung.

Für weitere Einzelheiten Besuchen Sie Synopsys Complete 1.6T Ethernet IP Solution.

Du kannst dich Hier finden Sie die Pressemitteilung von Synopsys zu ihrer kompletten 1.6T-Ethernet-IP-Lösung.

Lesen Sie auch:

Zusammenfassung der Signal & Power Integrity SIG-Veranstaltung 2024

Navigieren durch die 1.6-Tbit/s-Ära: Elektrooptische Verbindungen und 224G-Verbindungen

Warum hat Synopsys Ansys wirklich übernommen?

Teile diesen Beitrag über:

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoData.Network Vertikale generative KI. Motiviere dich selbst. Hier zugreifen.

- PlatoAiStream. Web3-Intelligenz. Wissen verstärkt. Hier zugreifen.

- PlatoESG. Kohlenstoff, CleanTech, Energie, Umwelt, Solar, Abfallwirtschaft. Hier zugreifen.

- PlatoHealth. Informationen zu Biotechnologie und klinischen Studien. Hier zugreifen.

- Quelle: https://semiwiki.com/ip/342740-complete-1-6t-ethernet-ip-solution-to-drive-ai-and-hyperscale-data-center-chips/