Seit Jahrzehnten beobachte ich das unglaubliche Wachstum von SoCs in Bezug auf Chipgröße, Transistoranzahl, Frequenz und Komplexität. Anstatt die gesamte Systemkomplexität in einem einzigen, monolithischen Chip unterzubringen, gibt es jetzt zwingende Gründe für die Verwendung eines Multi-Chip-Ansatzes, etwa wenn die maximale Chipgröße erreicht ist oder es kostengünstiger ist, zwei oder mehr kleinere Chiplets zu verwenden Entworfen in einer Vielzahl von Technologieknoten. Der Weg des Multi-Die-Systems bringt neue Herausforderungen bei der Chiplet-Verbindung mit sich:

- Zuverlässige Konnektivität

- Grosse Bandbreite

- Low-Power

- Geringe Latenz

- Unterstützung von Standards

Zum Glück für die Branche gab es eine gemeinsame Anstrengung, Standards zu entwickeln Universeller Chiplet Interconnect Express™ (UCIe™) hat an Bedeutung gewonnen, indem es die Integration auf Paketebene über eine Die-to-Die-Verbindung zusammen mit einem Konnektivitätsprotokoll ermöglicht, sodass mehrere Anbieter durch Interoperabilität ein Ökosystem aufbauen können. UCIe deckt drei Stapelschichten ab und die PHY-Schicht definiert die elektrische Schnittstelle.

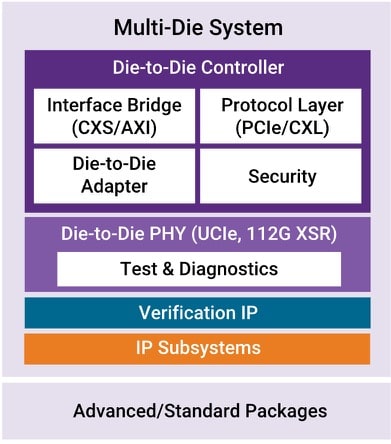

Synopsys war Bereitstellung von IP seit vielen Jahren in vielen Bereichen, wie zum Beispiel: Schnittstelle, Grundlage, Prozessor, Sicherheit, Analog, Subsysteme. Sie sind außerdem dem UCIe-Konsortium beigetreten und haben zur Spezifikation des Standards beigetragen. Da ist ein UCIe PHY IP von Synopsys, zusammen mit a UCIe-Controller-IP und Verifizierungs-IP.

Im März 2023 gab Synopsys bekannt, dass ihre UCIe PHY IP einen Tape-Out aufwies TSMC N3E Prozessknoten.

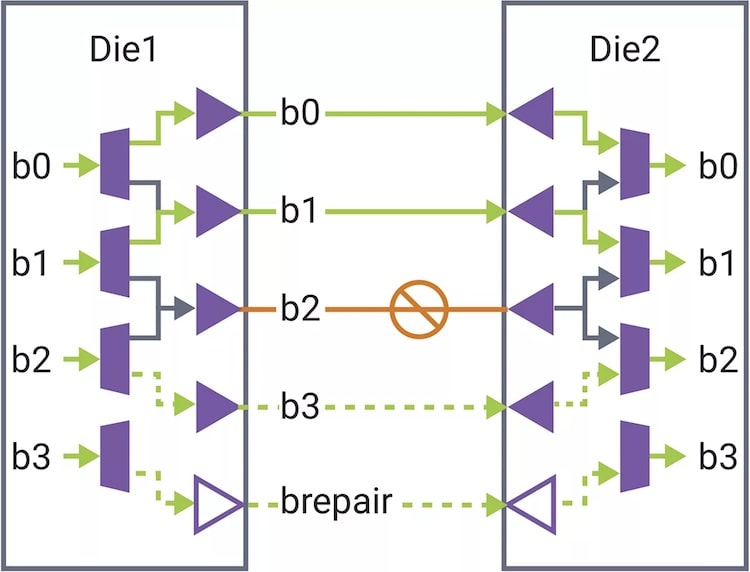

Für eine zuverlässige Konnektivität verfügt der UCIe-Standard über bis zu 8 Ersatzpins pro Richtung, was eine Reparatur der Funktionsverbindungen ermöglicht.

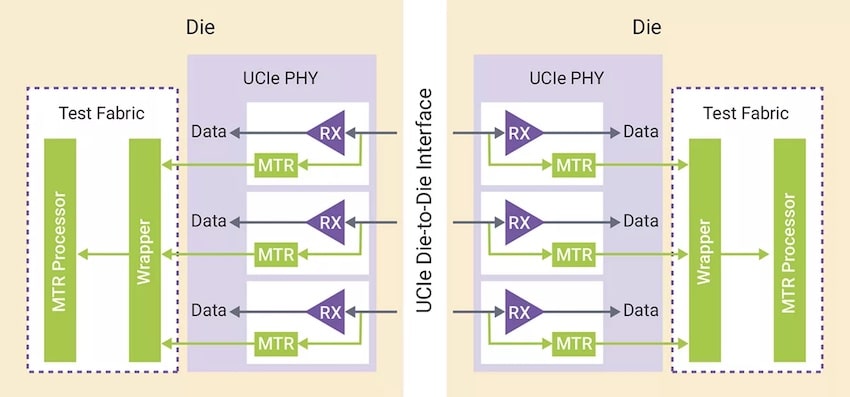

Variationen in den Die-zu-Die-Schnittstellensignalen werden von Signal Integrity Monitors (SIM) überwacht. Anschließend kann der Überwachungs-, Test- und Reparaturcontroller den Zustand des Multi-Die-Systems für die vorausschauende Wartung der Verbindungen ermitteln. Synopsys hat das Silizium-Lebenszyklusmanagement Tools zur Überwachung der UCIe-Schnittstelle während des Betriebs und zur Erkennung von Soft- oder Hard-Fehlern.

Die Bandbreite für UCIe unter Verwendung der Synopsys PHY IP beträgt bis zu 5 Tbit/s/mm. Die Controller-IP unterstützt Streaming-Protokolle sowie PCI Express- und CXL-Protokolle und liefert sichere Daten mit geringer Latenz.

Sich an die UCIe-Spezifikation zu gewöhnen, kostet wertvolle Entwicklungszeit. Durch die Wiederverwendung der Protokollverifizierungs-IP wird Ihr Team also wertvolle Zeit bis zur Markteinführung sparen. Die Ausführung einer IP-Verifizierung auf einem Software-Simulator bietet einen guten Anfang, gefolgt von der Hinzufügung einer Hardware-Emulation Inhaltsangabe ZeBu und Prototyping mit Synopsys HAPS Die Plattform bietet mehr Zeitersparnis beim Debuggen der gesamten Systemlaufsoftware.

Die Weiterleitung der UCIe-Signale zwischen den Chips wird durch automatisiert Synopsys 3DIC-Compiler Tool, und es funktioniert für 2.5D-Chiplets.

Zusammenfassung

Systemingenieure müssen sich heute noch zwischen zwei Implementierungsansätzen entscheiden: dem traditionellen Single-Chip-SoC oder dem Multi-Die-System. EDA-Anbieter wie Synopsys automatisieren seit langem die EDA-Aufgaben für einen Single-Chip-SoC und haben ihre Automatisierung auch auf den Bereich von 2.5D ausgeweitet, indem sie neue EDA-Tools, Verifizierung und IP für Multi-Chip-Systeme entwickelt haben.

Die Verbindungsherausforderungen von Multi-Die-Systemen wurden durch Standardisierungsbemühungen wie UCIe angegangen, was die Risiken für neue Projekte, die Chiplet-basierte Systeme in Betracht ziehen, verringert. Synopsys ist einer der wenigen EDA- und IP-Anbieter mit solch umfassender Unterstützung von Multi-Die-Systemen.

Verwandte Blogs

Teile diesen Beitrag über:

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoAiStream. Web3-Datenintelligenz. Wissen verstärkt. Hier zugreifen.

- Die Zukunft prägen mit Adryenn Ashley. Hier zugreifen.

- Kaufen und verkaufen Sie Anteile an PRE-IPO-Unternehmen mit PREIPO®. Hier zugreifen.

- Quelle: https://semiwiki.com/eda/synopsys/329299-chiplet-interconnect-challenges-standards/