Wenn Sie, wie ich, historisch weniger glamourösen Bereichen des Chipdesigns wie der Verpackung zu wenig Aufmerksamkeit geschenkt haben, werden Sie eines Tages aufwachen und feststellen, wie sehr sich die Dinge geändert und weiter entwickelt haben und wie interessant es geworden ist.

Einer der Hauptgründe dafür ist der zunehmende Einsatz von Chiplets, um den sinkenden – ja verschwindenden – Kostengewinnen durch die jüngsten Prozessschrumpfungen entgegenzuwirken, indem eine feinkörnigere Abbildung großer Subsystemblöcke auf ihre optimale Prozesstechnologie ermöglicht und die Wiederverwendung von Blöcken und Designressourcen optimiert werden .

Dies ist die Art von Paketszenario, mit dem wir es zu tun haben (nennen wir es eine Versammlung of Komponenten).

Die expandierende Welt des 2.5D- und 3D-Packaging liegt zwischen monolithischem Chip- und PCB-Design, sodass sowohl EDA- als auch System-Level-Tools zusammengebracht werden müssen, um den Prozess zu automatisieren. Aufgaben wie die ordnungsgemäße Automatisierung der Konnektivität innerhalb von Paketen, die Überprüfung vertikaler Ebenenverbindungen und eine präzisere thermische Modellierung.

Wie bei fast allem anderen in EDA heutzutage bedeutet dies eine immer engere Zusammenarbeit zwischen EDA-Tool-Anbietern, Fertigung und Designern.

Die Arbeit von Siemens und TSMC an 3DIC zur gemeinsamen Entwicklung des einheitlichen Design-Ökosystems TSMC 3Dblox auf Basis von Calibre 3DSTACK und c-Tools von Siemens ist ein gutes Beispiel. Die Präsentation von John Ferguson beim TSMC OIP im vergangenen Oktober befasste sich mit den Fortschritten hier sowohl bei der logischen als auch bei der physikalischen Verifizierung und thermischen Analyse. Lass uns genauer hinschauen.

Schließen der Lücken in der physischen 3D-Verifikation

Hier gibt es einige offensichtliche Herausforderungen bei 3DIC-Strukturen.

- Prozesse können Schichtnamen teilen, obwohl sie unterschiedliche Eigenschaften haben

- Pin- und Pad-Namen auf Komponenten können äquivalent sein, verwenden aber unterschiedliche Namen

- Tools müssen ein kombiniertes PV-Deck, eine Netzliste und eine physische Datenbank erstellen, um die gesamte Baugruppe zu überprüfen und dennoch die korrekten Regeln für einzelne Komponenten beizubehalten

- Möglicherweise unterschiedliche Eingabedateiformate für die Komponenten.

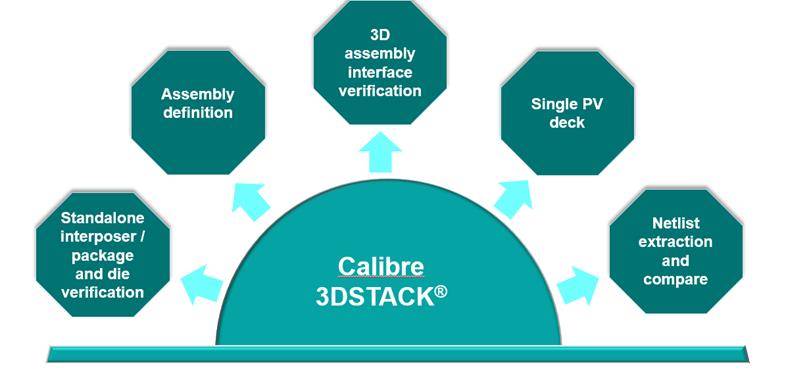

Verpackung mit heterogener Prozess sterben schafft neue Herausforderungen für die physische Verifizierung (PV), hauptsächlich bei der Erstellung einer vollständigen und genauen DB. Calibre 3DSTACK (siehe Diagramm unten) hat bereits einen Großteil dieser PV-Vorbereitung übernommen – Aufgaben wie das Kompilieren der physikalischen DB der Baugruppe mit einem einzelnen PV-Deck und das Berechnen der korrekten Kopplung zwischen gestapelten Chips.

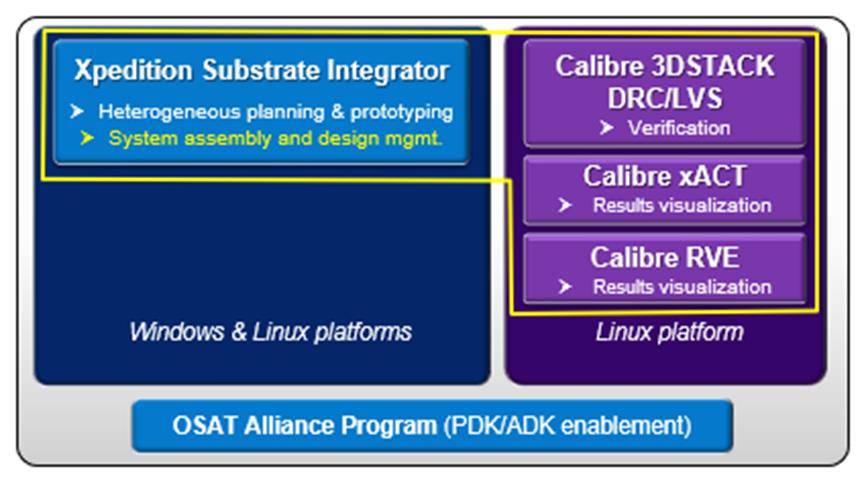

Das Hinzufügen des Planungstools Xpedition Substrate Integrator (XSI) von Siemens schließt die verbleibenden Lücken bei der Beschreibung der erforderlichen Komponenten und Konnektivität (analog zu einer Spezifikation oder einem benutzerdefinierten Schema), der Erstellung einer zusammengeführten Netzliste und der Verwaltung der Design-DB; sogar die Calibre 3DSTACK-Verifizierung wird automatisiert.

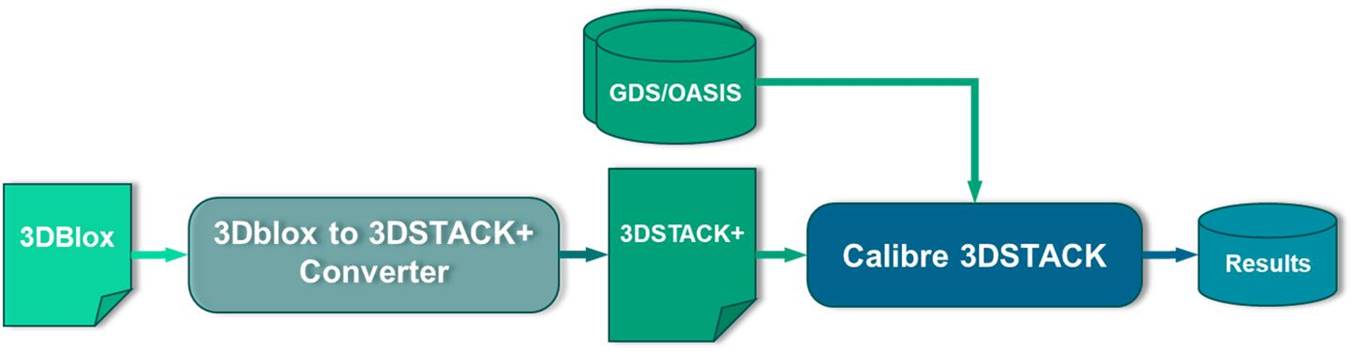

Eines bleibt – einen Weg zu finden, adäquate „Bibliotheksmodelle“ und „Designregeln“ für die Komponenten zu erstellen. Der neue 3DBlox-Ansatz von TSMC tut dies mit Assembly Design Kits (APDK), um die Konnektivitäts-, Prozess- und Montageeigenschaften und Designregeln für jede Komponente zu beschreiben.

Wenn wir dies alles zusammenfassen, erhalten wir einen Fluss, in dem wir das vollständige Assembly-PV vorbereiten, ausführen und debuggen können.

Thermische Analyse

3D-Verpackungen stellen auch größere thermische Herausforderungen dar, darunter:

- größere Interaktion zwischen sterben

- härtere Herausforderung bei der Wärmeableitung – höhere Leistungsdichte durch 3D-Stapelung

- die Modellierung vertikaler thermischer Gradienten wird notwendig

- Modellierung der Kühlkörperinteraktion für 3D-Die

Die Transistorleistung hängt stark von der Temperatur ab, daher können solche thermischen Effekte nicht ignoriert werden. Und dies sind nicht nur Signoff-Checks – wir brauchen eine gute Wärme- und Leistungsmodellierung sehr früh im Design und integriert in den ASIC-Design-Flow, da späte Änderungen hier zu erheblichen Nacharbeiten führen.

Bei der physischen Verifizierung bestand die Herausforderung eher darin, die Schnittstellen der obersten Ebene und der Komponenten zu verifizieren. Hier geht es eher darum, die Auswirkungen des Gesamtsystems auf die Komponenten zu verstehen – und wie sich das dann in das übergeordnete System zurückspielt.

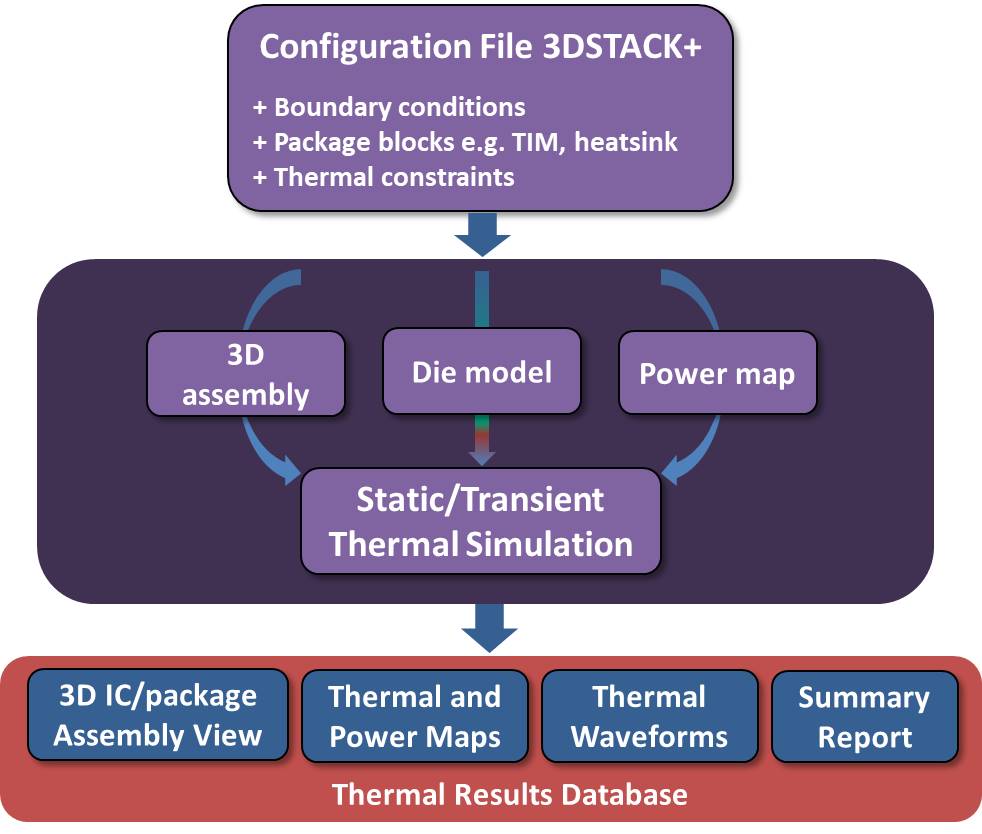

Eine weitere Zusammenarbeit mit TSMC erweiterte einen Flow, der um die bestehenden Tools Siemens Calibre 3DSTACK und SimCenter Flotherm herum aufgebaut war, wobei ein Großteil der Infrastruktur aus dem PV-Flow wiederverwendet wurde.

Analysen, einschließlich statischer und dynamischer Heatmaps, können auf Baugruppen-, Chip- oder IP-Ebene durchgeführt und Leistungsanalysen mit mPower ausgeführt werden. Für eine genauere Signal- und Zeitanalyse können Gerätetemperaturkoeffizienten extrahiert werden.

Zusammenfassung

Siemens und TSMC haben eine Entwurfsmethodik und einen Ablauf zusammengestellt, um aktuelle und zukünftige 3DICs auf der Grundlage bewährter Tools (Calibre 3DSTACK und SimCenter Flotherm) und mit besonderem Augenmerk auf die Vereinfachung der Konfiguration und Modellierung (3DBlox) und die frühe Verwendung des Entwurfs zu unterstützen. Dies sollte auch weiterhin so sein skalieren, da immer ausgefeiltere 3D-Verpackungstechnologien auf den Markt kommen.

Bemerkenswert ist auch, dass Siemens für diese Arbeit die Auszeichnung TSMC OIP Partner of the Year gewonnen hat.

Weitere Informationen

Die TSMC OIP-Präsentation („TSMC 3Dblox™ vereinfacht die Kaliberüberprüfung und -analyse“) ist bis Mai für Leser mit dem von TSMC bereitgestellten Original-Eventregistrierungslink und -code verfügbar.

Erfahren Sie hier mehr über die physische Verifizierung von Calibre und 3DSTACK:

https://eda.sw.siemens.com/en-US/ic/calibre-design/physical-verification/

https://eda.sw.siemens.com/en-US/ic/calibre-design/physical-verification/3DSTACK/

Ein Whitepaper „Die physische Verifizierung von 2.5D/3DIC auf die nächste Stufe bringen“ ist ebenfalls verfügbar.

Informationen zur thermischen Analyse von Siemens Flotherm finden Sie hier:

https://www.plm.automation.siemens.com/global/en/products/simcenter/flotherm.html

Lesen Sie auch:

Erreichen eines schnelleren Abschlusses der Designverifizierung

Siemens strebt KI im PCB-Design an

Teile diesen Beitrag über:

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- Platoblockkette. Web3-Metaverse-Intelligenz. Wissen verstärkt. Hier zugreifen.

- Quelle: https://semiwiki.com/eda/siemens-eda/324284-advances-in-physical-verification-and-thermal-modeling-of-3dics/