Heutzutage wird viel über die Beseitigung von Innovationshindernissen diskutiert. Halbleitersysteme sind das Herzstück der Erschließung vieler Formen technischer Innovation, wenn wir nur Probleme wie die Verlangsamung des Mooreschen Gesetzes, die Reduzierung des Stromverbrauchs, die Verbesserung von Sicherheit und Zuverlässigkeit usw. angehen könnten. Aber es gibt noch ein weiteres ziemlich erhebliches Hindernis, das Gegenstand dieses Beitrags ist. Es ist der dramatische Unterschied zwischen Prozessor- und Speicherleistung. Während CPU- und GPU-Systeme unglaubliche Leistungsniveaus liefern, hinken die Speicher, die kritische Daten für diese Systeme verwalten, erheblich hinterher. Das ist das Problem der Erinnerungswände, und ich möchte untersuchen, wie Arteris Innovationen freisetzt, indem es diese aufbricht Speicherwand.

Was ist die Memory Wall?

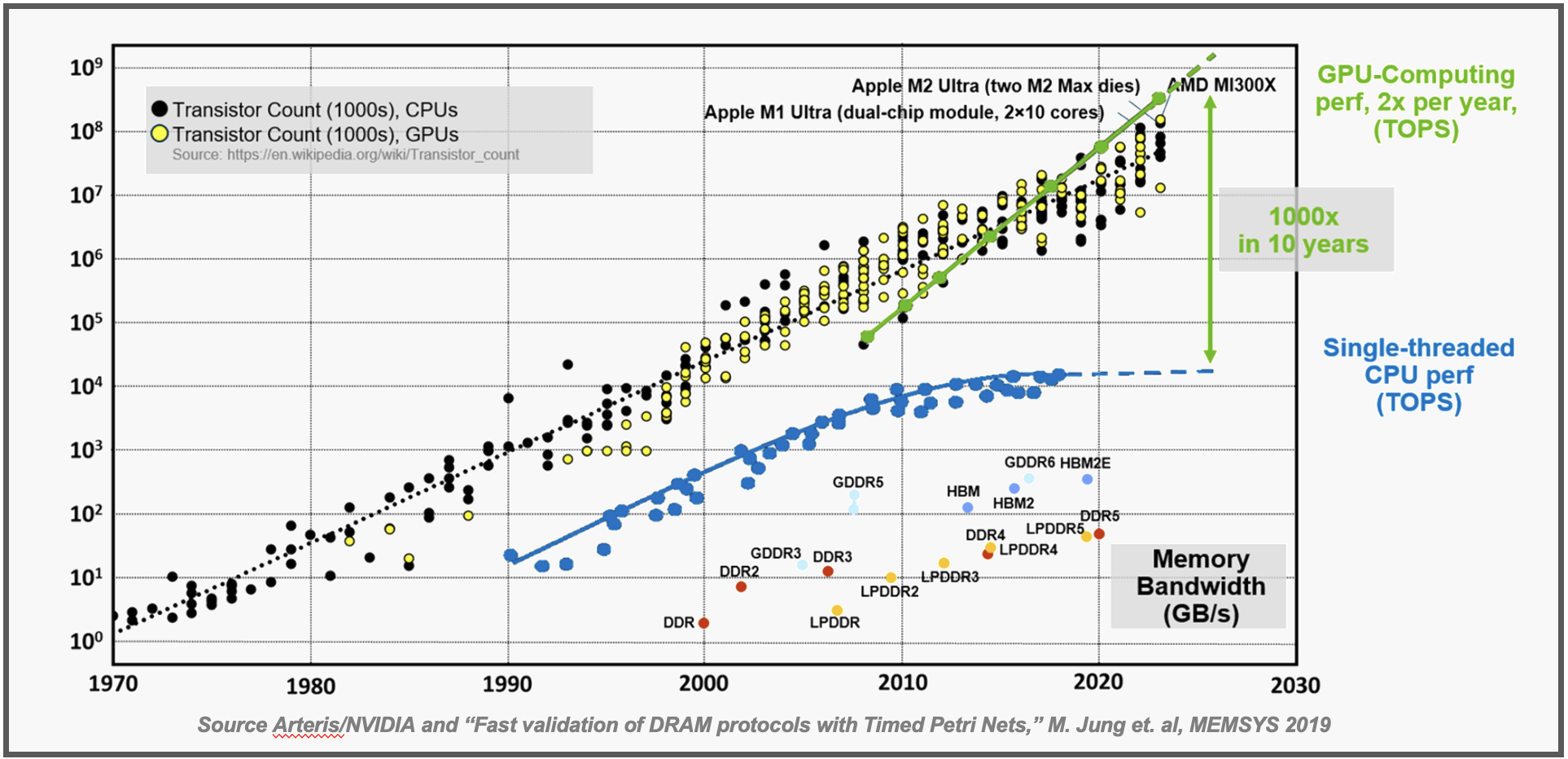

Die Grafik oben in diesem Beitrag veranschaulicht das Memory-Wall-Problem. Die stetige Leistungssteigerung von Single-Threaded-CPUs erkennen Sie an der blauen Linie. Die grüne Linie zeigt die exponentielle Leistungssteigerung durch GPU-Cluster. Die Leistungssteigerung von GPUs im Vergleich zu CPUs wird in 100 Jahren auf das Hundertfache geschätzt – eine umwerfende Statistik. Als Randbemerkung können Sie sehen, dass sich die Transistorzahlen sowohl für CPUs als auch für GPUs um eine ähnliche gerade Linie gruppieren. Die GPU-Leistung wird dadurch erreicht, dass weniger Aufgaben viel schneller erledigt werden, anstatt mehr Transistoren für das Problem einzusetzen.

Viele Systeme sind heutzutage eine Kombination aus einer Reihe von CPUs, die umfassende Verwaltungsaufgaben übernehmen, und einer großen Anzahl von GPUs, die spezifische Aufgaben übernehmen, die oft mit KI zusammenhängen. Die Kombination liefert den erstaunlichen Durchsatz, den wir bei vielen Produkten sehen. Diese harmonische Architektur hat eine dunkle Seite, die unten in der Grafik dargestellt ist. Hier sehen wir die Leistungsdaten der verschiedenen Speichertechnologien, die alle Informationen liefern, die diese Systeme verarbeiten können. Wie Sie sehen, ist die gelieferte Leistung wesentlich geringer als bei den CPUs und GPUs, die auf diesen Speichersystemen basieren.

Das ist das Memory-Wall-Problem. Lassen Sie uns die einzigartige Art und Weise erkunden, wie Arteris dieses Problem löst.

Der Arteris-Ansatz – ein hochkonfigurierbarer Cache-kohärenter NoC

Ein allgemein akzeptierter Ansatz zum Umgang mit langsameren Speicherzugriffsgeschwindigkeiten besteht darin, die erforderlichen Daten vorab abzurufen und in einem lokalen Cache zu speichern. Der Zugriff auf Daten ist auf diese Weise viel schneller – ein paar CPU-Zyklen gegenüber über 100 CPU-Zyklen. Es ist ein toller Ansatz, aber es kann entmutigend sein, die gesamte erforderliche Software und Hardware zu implementieren, um aus dem Cache auf den Speicher zuzugreifen und sicherzustellen, dass die richtigen Daten zur richtigen Zeit am richtigen Ort und über alle Caches hinweg konsistent sind. Systeme, die diese Lösung effektiv liefern, werden genannt Cache kohärent, und dieses Ziel zu erreichen ist nicht einfach. Eine reine Software-Kohärenzimplementierung kann beispielsweise bis zu etwa 25 % aller CPU-Zyklen im System verbrauchen und ist sehr schwer zu debuggen. SoC-Designer entscheiden sich stattdessen oft für Cache-kohärente NoC-Hardwarelösungen, die für die auf dem System laufende Software transparent sind.

Kürzlich hatte ich die Gelegenheit, mit Andy Nightingale, Vice President Product Management & Marketing bei, zu sprechen Arterien. Andy hat großartige Arbeit geleistet und die Herausforderungen bei der Implementierung von Cache-kohärenten Systemen und die einzigartige Lösung erklärt, die Arteris zur Bewältigung dieser Herausforderungen entwickelt hat.

Es stellt sich heraus, dass die Entwicklung einer zuverlässigen und energieeffizienten Cache-kohärenten Architektur viele Hardware- und Softwareaspekte des Systemdesigns berührt. Es kann ziemlich schwierig sein, alles zuverlässig und effizient zum Laufen zu bringen und die erforderlichen PPA-Ziele zu erreichen. Andy schätzte, dass all diese Arbeiten pro Projekt 50 Ingenieurjahre erfordern könnten. Das ist viel Zeit und Kosten.

Die gute Nachricht ist, dass Arteris über umfangreiche Kompetenzen in diesem Bereich verfügt und das Unternehmen eine vollständige Cache-kohärente Architektur in eines seiner Network-on-Chip (NoC)-Produkte integriert hat. Andy beschrieb Ncore, ein vollständig Cache-kohärentes NoC, das von Arteris angeboten wird. Die Verwaltung des Speicherzugriffs passt gut in die gesamte Network-on-Chip-Architektur, für die Arteris bekannt ist. Ncore verwaltet den Cache-kohärenten Teil des SoC transparent für die Software – so kann sich der Systementwickler auf die übergeordneten Herausforderungen konzentrieren, die damit verbunden sind, die CPU und all diese GPUs dazu zu bringen, die jeweilige Aufgabe auszuführen.

Andy hat eine umfangreiche Liste der Ncore-Funktionen zusammengestellt:

- Produktiv: Verbinden Sie mehrere Verarbeitungselemente, einschließlich Arm und RISC-V, für maximale Engineering-Produktivität und schnellere Markteinführung, wodurch mehr als 50 Personenjahre pro Projekt eingespart werden.

- Konfigurierbar: Skalierbar von heterogenen bis hin zu Mesh-Topologien, unterstützt kohärente CHI-E-, CHI-B- und ACE- sowie kohärente ACE-Lite IO-Schnittstellen. Ncore ermöglicht es auch nicht-kohärenten AXI-Agenten, als IO-kohärente Agenten zu fungieren.

- Ökosystemintegration: Vorab validiert mit den neuesten Arm v9-Automobilkernen und im Rahmen einer bereits angekündigten Partnerschaft mit Arm.

- Sicher: Unterstützt die Anforderungen von ASIL B bis ASIL D für Sicherheitsanwendungen im Automobilbereich und ist ISO26262-zertifiziert.

- Effizient: Kleinere Chipfläche, geringerer Stromverbrauch und höhere Leistung im Vergleich zu anderen kommerziellen Alternativen.

- Märkte: Geeignet für Automotive-, Industrie-, Enterprise-Computing-, Consumer- und IoT-SoC-Lösungen.

Andy beschrieb einige der Vorteile, die mit einem SoC-Design für Verbraucher erzielt wurden. Dazu gehörte eine optimierte Chip-Grundrissplanung dank der stark verteilten Architektur, die eine effiziente Ressourcennutzung fördert. Die Arteris-Hochleistungsverbindung mit einer Fabric mit hoher Bandbreite und geringer Latenz sorgte für eine nahtlose Datenübertragung und steigerte die Gesamtsystemleistung.

Wenn wir etwas tiefer gehen, bietet Ncore außerdem Echtzeit-Einblick in die Verbindungsstruktur mit Nachverfolgung auf Transaktionsebene, Leistungsüberwachung sowie Fehlererkennung und -korrektur. Alle diese Funktionen ermöglichen ein einfaches Debuggen und eine hervorragende Produktqualität. Die umfassende Ökosystemunterstützung und Kompatibilität mit branchenüblichen Schnittstellen wie AMBA erleichtern auch die einfachere Integration mit Komponenten und EDA-Tools von Drittanbietern.

Das war eine sehr nützliche Diskussion. Es scheint, dass Arteris den Overhead für die Implementierung von Cache-kohärenten Architekturen drastisch reduziert hat.

Um mehr zu lernen

Ich habe einige Einzelheiten zur Arbeit von Arteris mit Arm erwähnt. Denken Sie nicht, dass dies der einzige Partner ist, mit dem das Unternehmen zusammenarbeitet. Arteris wird als die Schweiz des IP-Systems bezeichnet. Das Unternehmen arbeitet auch maßgeblich mit der RISC-V-Community zusammen ausführlich im SemiWiki-Beitrag hier.

Arteris hat kürzlich die Erweiterung seines Ncore-Produkts angekündigt. Sie können lesen, wie Arteris erweitert Ncore Cache Coherent Interconnect IP, um hier führende Elektronikdesigns zu beschleunigen. In der Pressemitteilung erklärt Leonid Smolyansky, Ph.D. SVP SoC Architecture, Security & Safety bei Mobileye äußerte sich wie folgt:

„Wir arbeiten seit 2010 mit der Network-on-Chip-Technologie von Arteris und nutzen sie in unseren fortschrittlichen autonomen Fahr- und Fahrerassistenztechnologien. Wir freuen uns, dass Arteris seine bedeutenden technischen Fähigkeiten eingebracht hat, um zur Lösung der Probleme der Fehlertoleranz und des zuverlässigen SoC-Designs beizutragen.“

Es gibt auch eine kurze (etwas mehr als eine Minute) Video, das die Herausforderungen erklärt, denen Ncore begegnet. Ich fand das Video recht informativ.

Wenn Sie für Ihr nächstes Design eine verbesserte Leistung benötigen, sollten Sie sich unbedingt die Cache-kohärenten Lösungen von Arteris genauer ansehen. Du kannst Erfahren Sie hier mehr über Ncore. Und so ist es Arterien setzt Innovationen frei, indem es die Erinnerungsmauer niederreißt.

Teile diesen Beitrag über:

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoData.Network Vertikale generative KI. Motiviere dich selbst. Hier zugreifen.

- PlatoAiStream. Web3-Intelligenz. Wissen verstärkt. Hier zugreifen.

- PlatoESG. Kohlenstoff, CleanTech, Energie, Umwelt, Solar, Abfallwirtschaft. Hier zugreifen.

- PlatoHealth. Informationen zu Biotechnologie und klinischen Studien. Hier zugreifen.

- Quelle: https://semiwiki.com/ip/arteris/342991-arteris-is-unleashing-innovation-by-breaking-down-the-memory-wall/