Am 13. September 2021 hat die Andes Technology Corporation ihr öffentliches GDR-Angebot (Global Depositary Receipt) erfolgreich an der Luxemburger Börse durchgeführt. Zu dieser Zeit war Andes der einzige internationale öffentliche CPU-IP-Anbieter für RISC-V-Befehlssatzarchitektur (ISA). Dies ermöglichte es Investoren auf der ganzen Welt, an dem Wachstum zu partizipieren, das Andes für RISC-V vorsah. Diese Kapitalspritze würde den Ehrgeiz von Andes befeuern, ein führendes Unternehmen auf dem sich schnell entwickelnden, wachstumsstarken RISC-V-Markt mit offenem Standard zu werden. Im Jahr 2015 erkannte Andes das enorme Potenzial der RISC-V ISA und wurde Gründungs- und Premier-Mitglied von RISC-V International.

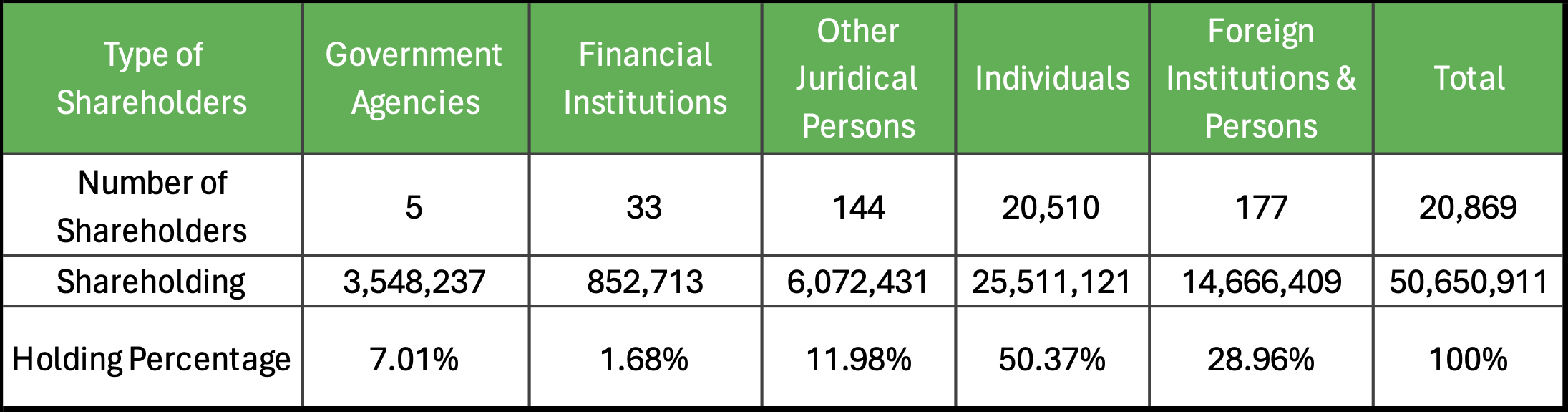

Stand: 2. April 2023; Einheit: Anteile, %

Die Investition hat sich besonders gelohnt, da sie mit der Ratifizierung der RISC-V-Vektorerweiterung im November 2021 zusammenfiel. Dieses Ereignis markierte einen Wendepunkt in der Entwicklung der RISC-V-Befehlssatzarchitektur. Die RISC-V-Vektorerweiterung kam zu einer Zeit, als sich die Datenverarbeitung im Rechenzentrum von der Allzweckverarbeitung zur KI-Verarbeitung wandelte, die extrem große Datensätze verarbeitet. Die Vektorverarbeitung zeichnet sich durch die effiziente Verarbeitung großer Arrays oder strukturierter Daten aus. Die Vektorverarbeitung hat das Potenzial, RISC-V zum nächsten großen weltweiten ISA zu machen.

Die hochparallele Architektur eines Vektorprozessors reduziert Latenz und Overhead. Es erreicht eine bessere Energieeffizienz durch Maximierung der CPU-Ressourcenauslastung und Minimierung von Leerlaufzyklen, wodurch eine höhere Leistung pro Watt erzielt wird. Darüber hinaus ist die Hardware zur Implementierung von RISC-V-Vektorverarbeitungseinheiten (VPUs) und Vektorregistern einfacher als bei hochparallelen Architekturen, die für die Grafikverarbeitung verwendet werden. Und VPUs bieten ein weitaus weniger komplexes Programmiermodell.

Die Forschungs- und Entwicklungsteams von Andes sowohl im nordamerikanischen Betrieb als auch in der erweiterten Belegschaft in Taiwan haben sich auf die Entwicklung modernster Architekturen für High-End-RISC-V-Prozessoren konzentriert. Insbesondere erreichten die beiden einen bedeutenden Meilenstein mit der Entwicklung der ersten RISC-V-Vektor-Engine (RVV), der AndesCore™ NX27V, basierend auf der RISC-V International RVV-Spezifikation. Der Entwurf wurde innerhalb eines Jahres fertiggestellt und basierte auf Version V0.8 der RISC-V-Vektorerweiterungsspezifikation und wurde später bei der Ratifizierung von RVV auf Version V1.0 geändert, was die Agilität und Innovationskraft des Andes-Ingenieurteams unter Beweis stellte. Dieser Erfolg führte zu einigen großen OEM-Designgewinnen.

Letztes Jahr präsentierte META auf der Konferenz International Symposium on Computer Architecture (ISCA) 2023 in Orlando, Florida, sein Papier „MTIA: First Generation Silicon Targeting Meta's Recommendation Systems“, das Rechenzentrums- und KI-Serverprojekt des Unternehmens. Es gibt 64 Verarbeitungselemente (PE) im Serverdesign, die den maßgeschneiderten proprietären Beschleuniger von MRETA unterstützen. Jedes PE enthält zwei Prozessoren: einen Skalar und einen Vektor. Bei beiden handelt es sich um IP von Andes, die von META-Ingenieuren mithilfe von Andes Custom Extensions (ACE) stark angepasst wurden, um eine völlig einzigartige Lösung zu erstellen, die auf die spezifischen KI-Computing-Anforderungen von META zugeschnitten ist.

Das Design bestätigte die Wirksamkeit von RISC-V mit Vector Extensions als leistungsstarke Lösung für KI-Rechenzentrums-Computing-Anforderungen in einer Zeit, in der die Nachfrage nach Rechenzentrums-Verarbeitungshardware explodiert. Entsprechend Markteinblicke der ZukunftBericht „Marktausblick für Rechenzentrums-CPUs (2023 bis 2033)“. Der Markt für Rechenzentrums-CPUs wird in den nächsten Jahren voraussichtlich erheblich wachsen, angetrieben durch die steigende Nachfrage nach Cloud Computing, Big-Data-Analysen und künstlicher Intelligenz (KI). . Zu den Haupttreibern dieses Wachstums zählen der Bedarf an schnellerer Datenverarbeitung, höherer Effizienz und geringeren Kosten.

Im Jahr 2021 ratifizierte RISC-V International zusätzlich zu den Vektorerweiterungen 11 weitere Erweiterungen. Abbildung 1 zeigt die Produkt-Roadmap von Andes zur Unterstützung dieser Erweiterungen. Bis Ende 2022 wurden N25F-SE, 27 Series und 45 Series ausgeliefert, im Jahr 2023 lieferte Andes sechs neue RISC-V-Kerne auf den Markt, darunter D25F-SE, D23, N225, NX45V und AX45MPV sowie AX65. Die Roadmap reicht vom stromsparenden und hochsicheren RISC-V-Einstiegsprozessor AndesCore™ D23 bis zum AX65, dem ersten der 60er-Serie, der im vierten Quartal 2023 auf den Markt kam und jetzt für Kundendesigns ausgeliefert wird.

Der AX65 ist ein 13-stufiger, 4-Wege-64-Bit-Out-of-Order-Prozessor mit RVA 22-Profil (RVA22U64-Profil spezifiziert die ISA-Funktionen, die für Benutzermodus-Ausführungsumgebungen in 64-Bit-Anwendungsprozessoren verfügbar sind). Ausgestattet mit einer 13-Stufen-Pipeline, 4-facher Dekodierung und 8-facher Out-of-Order-Ausführung zielt die Serie auf die Linux-Anwendungsprozessorsockel von Computern, Netzwerken und High-End-Controllern ab.

Der AX65 ermöglicht Multicore-Cluster von einem über vier bis acht Kerne. Die Leistung ist Weltklasse und arbeitet mit einer Taktfrequenz von 2.4 Gigahertz im Sieben-Nanometer-TSMC-Verfahren. Die Spec-Integer-Leistung (Specint 2006) beträgt 8.25 pro Gigahertz und ein SpecFp2006 beträgt 10.2 pro Gigahertz, was der bekanntesten SPEC CPU® 2006-Leistung mit zweistufigem Cache-Design entspricht. Danach werden AX66, AX63 und AX67 ausgeliefert.

Ein weiterer Bereich, in den Andes erheblich investiert hat, ist leistungsstarkes RISC-V-CPU-IP für die Automobilindustrie. Laut der SHD Group wird die Durchdringung von RISC-V-SoCs in Automobildesigns bis 21.4 voraussichtlich 2030 % erreichen „RISC-V-Marktbericht: Anwendungsprognosen in einer heterogenen Welt.“ Andes hat Produkte entwickelt, die der funktionalen Sicherheit entsprechen, darunter das N25F-SE, das weltweit erste vollständig ISO 26262-konforme RISC-V-CPU-IP; D25F-SE, das DSP-Erweiterungsanweisungen unterstützt; und die Prozessoren der 45-SE-Serie, die die höchste ASIL-Stufe ASIL D erfüllen. Die ACE-Funktion wird erweitert, um Unterstützung für Prozessoren der 45-Serie hinzuzufügen.

Aufgrund der starken Nachfrage nach RISC-V-Produkten von Andes bleibt das Unternehmen weiterhin profitabel und verzeichnet weiterhin ein schnelles Wachstum. Von 2021 bis 2023 verzeichnete Andes ein Umsatzwachstum von fast 30 %. Dies wurde durch über 300 kommerzielle Lizenznehmer und über 600 unterzeichnete Lizenzverträge mit geografisch verteilten Kunden in Taiwan, China, Korea, Japan, Europa und den USA vorangetrieben. Die weltweite Mitarbeiterzahl des Unternehmens wuchs im gleichen Zeitraum um fast 70 %.

Zusammenfassung

In einer Zeit, die von rasanter technologischer Entwicklung geprägt ist, steht Andes Technology Corp. an der Spitze der Innovation auf dem RISC-V-CPU-IP-Markt. Von der bahnbrechenden Ausgabe von Overseas Depositary Receipts (GDR) bis zu seinen bahnbrechenden Fortschritten in der RISC-V-Architektur definiert Andes Technology weiterhin Industriestandards neu und gestaltet die Zukunft der Datenverarbeitung. Da die Nachfrage nach effizienten Hochleistungs-Computing-Lösungen weiter steigt, ist Andes Technology weiterhin bestrebt, beispiellose RISC-V-Lösungen bereitzustellen, um den transformativen Wandel in der globalen Technologielandschaft voranzutreiben.

Lesen Sie auch:

LIVE-WEBINAR: RISC-V-Befehlssatzarchitektur: Verbesserung der Rechenleistung

WEBINAR: Nutzen Sie zertifiziertes RISC-V-IP, um ASIL ISO 26262-Automobilchips herzustellen

Teile diesen Beitrag über:

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoData.Network Vertikale generative KI. Motiviere dich selbst. Hier zugreifen.

- PlatoAiStream. Web3-Intelligenz. Wissen verstärkt. Hier zugreifen.

- PlatoESG. Kohlenstoff, CleanTech, Energie, Umwelt, Solar, Abfallwirtschaft. Hier zugreifen.

- PlatoHealth. Informationen zu Biotechnologie und klinischen Studien. Hier zugreifen.

- Quelle: https://semiwiki.com/ip/343097-andes-technology-pioneering-the-future-of-risc-v-cpu-ip/