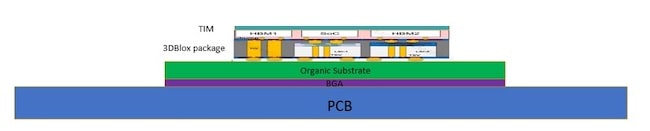

Bei SemiWiki haben wir jetzt vier Mal darüber geschrieben, wie TSMC mit ihrem Ansatz namens 3Dblox, also habe ich mir eine Präsentation von John Ferguson von Siemens EDA angesehen, um zu sehen, wie ihr Toolflow dies mit den Calibre-Tools unterstützt. Mit einem Chiplet-basierten Verpackungsfluss gibt es neue Herausforderungen bei der physischen Verifizierung, daher war die Antwort bei Siemens EDA zu entwickeln Kaliber 3DSTACK, das 3DIC unterstützt und thermische Analysen ermöglicht.

Physische Prüfungen für DRC stellen sicher, dass die Substratschnittstellen korrekt sind mit: Ausrichtung, Überlappungen, Skalierung und Chip-zu-Chip-Abständen. Die LVS-Prüfung bestimmt, ob die Konnektivität über den Interposer oder das Paket RDL im Vergleich zur goldenen Netzliste korrekt ist. Sogar die durch die Gehäuseverbindung gebildeten Parasiten müssen extrahiert und analysiert werden, da sie die Signalintegrität und die Zeitspielräume beeinflussen.

Ein früher Ansatz bei 3DIC für die LVS-Verifizierung bestand darin, sie für jede Die-to-Die-Schnittstelle separat auszuführen, aber das ist unpraktisch, stattdessen besteht der mit Calibre 3DSTACK verwendete Ansatz darin, die gesamte Baugruppe, sowohl DRC als auch LVS, mit einem Deck zu überprüfen laufen.

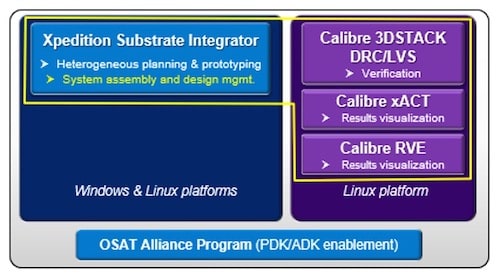

Um Ihre 3DIC-Gehäusemontage tatsächlich zu entwerfen und zu planen, gibt es ein weiteres Siemens EDA-Tool namens Xpedition Substratintegrator (XSI), und das ermöglicht Ihnen, die heterogene Regeldatei zu erstellen und die Quellnetzliste zu generieren. 3DIC-Paketdesign- und Verifizierungstools sind unten dargestellt:

TSMC stellt die Assembly Design Kits (ADK) bereit, um ihren 3Dblox-Tool-Flow zu unterstützen, wo es wie ein LEF/DEF-Flow ist, aber jetzt in 3 Dimensionen.

Die physische Verifizierungsprüfung im 3Dblox-Format wird in diesem Tool-Flow mit Calibre 3DSTACK automatisiert und ist unabhängig davon, welches Tool die 3Dblox-Daten erstellt.

Zusätzlich zur physikalischen 3DIC-Verifizierung gibt es neue Zuverlässigkeitsprobleme wie Wärme, da die Chiplets näher beieinander platziert werden. Temperaturerhöhungen verlangsamen die Schaltzeiten von Silizium und verkürzen die Lebensdauer von Halbleitern, was zu einem Timing- oder Zuverlässigkeitsfehler führen kann. Um herauszufinden, wie sich die Gehäusemontage auf jedes Chiplet auswirkt, gibt es ein weiteres EDA-Tool von Siemens, Simcenter Flotherm, um die Entwicklung eines thermischen digitalen Zwillings zu unterstützen. Damit erhalten Sie bereits in den frühen Planungsschritten eine schnelle Analyse. Analyseergebnisse als statische oder dynamische Heatmaps werden auf Baugruppen-, Die- oder IP-Ebene angezeigt. Sie können sogar eine Post-Layout-Netzliste mit den Temperaturkoeffizienten jedes Geräts erhalten, die für die Signalintegritäts- und Timing-Analyse verwendet wird.

Ausgehend von einer 3Dblox-Datei verwendet dieser thermische Fluss eine 3DSTACK-Syntax und erstellt individuelle Chipleistungskarten über die gesamte Baugruppe. Ingenieure sehen Wellenformen oder animierte Heatmaps der Temperaturen, oder die Leistung kann auf Chip- oder Baugruppenebene angezeigt werden. Einschränkungen können angegeben werden, und dann werden während der thermischen Simulation alle Warnungen oder Fehler notiert.

Das Hinzufügen thermischer Fähigkeiten zur Unterstützung von 3DIC-Packaging bei Siemens EDA erforderte eine enge Zusammenarbeit mit TSMC.

Zusammenfassung

Die Marktbegeisterung des 3DIC-Designs bringt auch neue technologische Herausforderungen mit sich, z. B. wie die physische Verifizierung mit DRC und LVS auf die effizienteste Weise durchgeführt werden kann. TSMC hat in einem Format standardisiert, das physische Stacking und die logischen Konnektivitätsinformationen, und nennt es 3Dblox. Siemens EDA mit Calibre 3DSTACK unterstützt das 3Dblox-Format in seinen DRC- und LVS-Flows vollständig. Das Entwerfen und Planen von 3D-Gehäusebaugruppen erfolgt mit XSI, und die neue thermische Analyse verwendet auch das 3Dblox-Format. Eine thermische Analyse für 3DIC-Verpackungen ist ebenfalls möglich, sodass Produkte so konstruiert werden können, dass sie Zuverlässigkeitsziele erfüllen.

Die EDA-, Foundry- und IP-Communities haben zusammengearbeitet, um sich den neuen 3DIC-Design- und Verifizierungsherausforderungen zu stellen, sodass unsere Wirtschaft einen stetigen Strom neuer Produkte genießen kann, die jetzt 100 Milliarden Transistoren erreichen. Die Zukunft von 3DIC ist in der Tat rosig.

Verwandte Blogs

Teile diesen Beitrag über:

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- Platoblockkette. Web3-Metaverse-Intelligenz. Wissen verstärkt. Hier zugreifen.

- Quelle: https://semiwiki.com/eda/siemens-eda/324006-3dic-physical-verification-siemens-eda-and-tsmc/