أصبحت المعالجات القابلة للتكوين ساخنة الآن ، ويرجع الفضل في ذلك إلى حد كبير إلى RISC-V. وهو ISA وليس معالجًا ، لكن دعونا لا نراوغ. يتبع Arm إمكانية التكوين في Cortex-X. كلاهما سبقه إلى حد كبير (عقدين) من وحدات المعالجة المركزية Synopsys ARC® RISC و CEVA DSP. أكد كل منها على قابلية التهيئة كمميز عن المعالجات المضمنة الأخرى وتمتع بنجاح مستمر في القيادة بهذه الإمكانية. قبل بضعة أشهر ، استضافت Synopsys خلفية مفيدة حول لماذا وكيفية التهيئة ، والتي تركزت بشكل طبيعي حول معالجات ARC.

لماذا التكوين؟

هناك العديد من السائقين. سماعات الأذن وبشكل عام ، يجب أن تكون الأجهزة القابلة للارتداء ذات طاقة منخفضة للغاية مع تحسين المعالجة إلى أقصى حد وصولاً إلى مستوى التعليمات أو أقل منه. في السحابة والبنية التحتية للشبكة ، أصبحت الحوسبة مجزأة لتقليل الكمون والطاقة. تطالب أيضًا بالتحسين لتحقيق تلك الأهداف. في مراكز البيانات ، تقوم الخوادم الآن بإلغاء تحميل عمليات البحث الأولية في قاعدة البيانات إلى محركات أقراص الحالة الصلبة الذكية ، من أجل التنبؤ بالبحث والتآكل. توزع شبكات RAN المفتوحة المعلومات والتخزين عبر الشبكة لتكون سريعة وسريعة الاستجابة ومع ذلك يجب أن تكون فعالة للغاية من حيث التكلفة.

يعد دعم الاتصال من السيارة إلى البنية التحتية (V2X) مثالًا رائعًا يستحق أكثر من ذلك بقليل الخلفية الدرامية. يعد نظام إدارة بيانات الاعتماد الآمن في الولايات المتحدة (SCMS) مرشحًا رائدًا للحصول على شهادة V2X ويبني على تقنية مفتاح عام / خاص تسمى مفاتيح الفراشة الموحدة. يسمح هذا لطرف ثانٍ بتوليد سلسلة من المفاتيح العامة التي يعرفها المنشئ فقط المفاتيح الخاصة. مما لا يثير الدهشة ، أن هذا النظام يشدد بشدة على الأداء. هناك عمليات حلقة في العملية تمنع تحقيق تلك الأهداف باستخدام خوارزميات البرامج التقليدية التي تعمل على المعالج. يجب تسريع هذه الأقسام ذات الأداء الحرج بطريقة ما.

تمديد المعالج ISA

جزء من سبب بطء هذه الحلقات هو الحمل الزائد في خط أنابيب وحدة المعالجة المركزية لكل تعليمة. الجلب ، فك التشفير ، الإرسال ، المضاربة ، التنفيذ ، إعادة الكتابة. إذا كان تسلسل التعليمات قابلاً للضغط في واحد أو بضعة تعليمات ، فيمكن أن يوفر ذلك وقتًا كبيرًا عن طريق تقليل هذا الحمل. يمكن أن يكون هناك أيضًا مزايا أخرى مثل المعالجة الخاصة لحساب الكلمات الطويلة جدًا.

تتيح تقنية Synopsys ARC APEX إضافة تعليمات مخصصة لتلبية هذه الحاجة. يقوم مطور ببناء (من خلال APEX) Verilog لتلك التعليمات. يمكن أن يتصل هذا بموارد المعالج القياسية مثل رموز الحالة والسجلات والإشارات. سيقوم APEX بإدخال Verilog في قلب ARC ، بالتوازي بشكل أساسي مع ALU. عندما تقوم إحدى التعليمات بترميز هذه العملية الخاصة ، فسيتم توجيهها إلى المنطق المخصص بدلاً من ALU. خلاف ذلك ، تعمل بقية وحدة المعالجة المركزية وتدفقات المترجم بنفس الطريقة. طريقة سهلة لطي التعليمات المخصصة في الأساس.

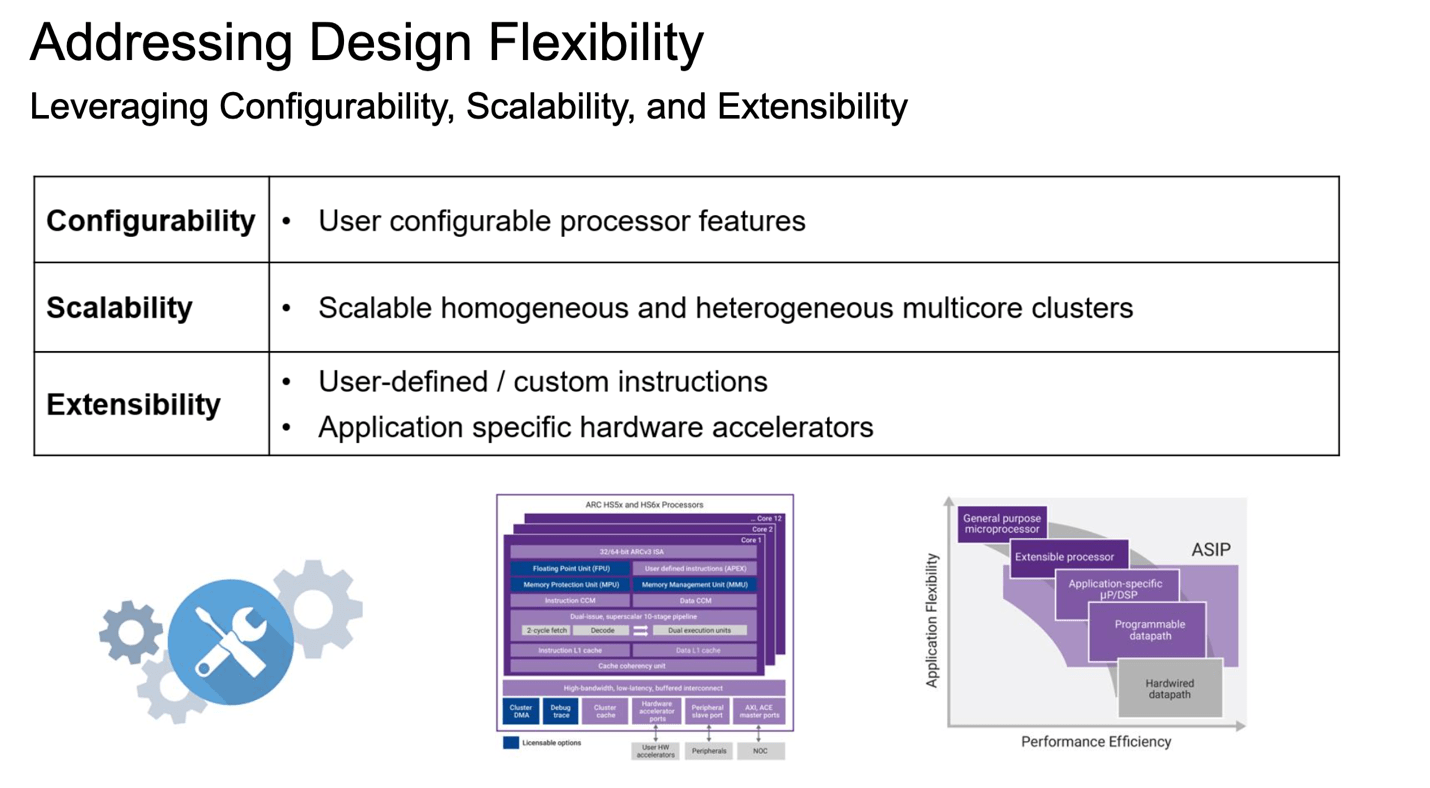

يجب أن أضيف أن Synopsys يوفر خيارات أخرى للتحسين: قابلية التكوين في المعالج الأساسي والتوازي من خلال تطبيقات متعددة النواة. دعم أيضًا مسرعات العملاء المقترنة بشكل وثيق والتي يمكنها الاتصال مباشرة بذاكرة التخزين المؤقت المشتركة ومشاركة الذاكرة.

هل يستحق كل هذا الجهد؟

أبرز ريتش كولينز (مدير تسويق المنتجات) أحد الأمثلة في الحديث: تحسين خوارزمية الشجرة باللونين الأحمر والأسود (موازنة الأشجار) لتطبيق التخزين. هنا ، كان المصممون قادرين على تقليل وقت التنفيذ (وبالتالي الطاقة) بنسبة 50٪ مع القليل من المساحة المضافة. ليس لدي أرقام لتصميم SCMS (المشار إليها سابقًا في هذه المقالة)؛ من الصعب جدًا فصل هذه التحسينات عن الخوارزميات. من الواضح أنهم اعتمدوا بشدة على ARC و APEX لجعل تصميمهم ممكنًا.

الاشياء. يمكنك مشاهدة الندوة عبر الإنترنت هنا.

شارك هذا المنشور عبر:

- كوينسمارت. أفضل بورصة للبيتكوين والعملات المشفرة في أوروبا.انقر هنا لمعرفة ذلك

- بلاتوبلوكشين. Web3 Metaverse Intelligence. تضخيم المعرفة. الوصول هنا.

- المصدر https://semiwiki.com/automotive/320767-configurable-processors-the-why-and-how/