منذ عدة سنوات، كنت أقابل أميك إيدا المؤسس المشارك كريستيان أميترواي كل بضعة أشهر لمناقشة حالة الصناعة، والاتجاهات الرئيسية في التصميم والتحقق، والطرق التي تساعد في تسهيل وتسريع تطوير الرقائق. لقد لاحظت ميزة جديدة مثيرة للاهتمام مذكورة في أحدثها خبر صحفىلذلك طلبت من كريستيان المزيد من المعلومات. وأدى ذلك إلى مناقشة حية ومثيرة للاهتمام.

يقوم معظم المصممين ومهندسي التحقق بكتابة التعليمات البرمجية الخاصة بهم في SystemVerilog هذه الأيام، ولكن هناك استثناءات. يستفيد البعض من أدوات التوليف عالية المستوى (HLS) للتصميم في SystemC أو لغات أخرى أكثر تجريدًا قليلاً من SystemVerilog. يكتب آخرون بلغاتهم الخاصة ويستخدمون أدوات مخصصة لإنشاء ملفات SystemVerilog المستخدمة للمحاكاة والتحقق الرسمي والتوليف وخطوات أخرى في عملية التطوير.

قال كريستيان إنهم يرون في بعض الأحيان حلاً وسطًا يكتب فيه المهندسون تعليمات برمجية تكون في المقام الأول SystemVerilog ولكنها تحتوي أيضًا على عبارات "معالج مسبق" في اللغات القائمة مثل مكتبة Perl وPython's Jinja2، أو في اللغات الخاصة. يستخدمون البرامج النصية لمعالجة هذه الملفات وإنشاء ملفات SystemVerilog النقية لبقية التدفق. سألت كريستيان كيف يغير استخدام المعالجات الأولية الطريقة التي يستخدم بها المهندسون بيئة التطوير المتكاملة (IDE).

علمت أن مستخدمي أدوات التصميم والتحقق من AMIQ EDA (DVT) تريد عائلة IDE الوصول إلى جميع ميزاتها المفضلة حتى عند تحرير الملفات باستخدام كود المعالج المسبق. قام فريق AMIQ EDA بتطوير أساليب استدلالية ذكية لتمكين إمكانات IDE الكاملة عند تحرير مثل هذه الملفات، تمامًا كما يفعلون مع SystemVerilog الخالص. تتضمن هذه الميزات الارتباطات التشعبية الملاحية، والإكمال التلقائي، واكتشاف الأخطاء أثناء التنقل، والإصلاحات السريعة، وإعادة البناء، وجميع الوظائف المتقدمة التي يدمن عليها مستخدمو DVT IDE.

كان هذا مثيرا للاهتمام بالنسبة لي. نحن نتحدث عن "فهم" الملفات متعددة اللغات، وهو أمر لا يمكن لأي مترجم استيعابه بسهولة. للتأكد من أنني فهمت الأمر بشكل صحيح وأن هذا حقيقي، دعا كريستيان Zeljko Zurzic، قائد الفريق الذي نسق تطوير هذه القدرة، لشرح كيفية عملها. وقال إن كل ما يحتاجه المستخدمون هو إبلاغ DVT IDE بالتعيين بين الملفات التي تحتوي على عبارات المعالج المسبق ("ملف p") والملفات التي تم إنشاؤها ("ملف g").

ويتم ذلك باستخدام توجيهات المترجم المخصصة التي تدعم حالات الاستخدام المختلفة. على سبيل المثال، هناك طريقة لإخبار مترجم DVT IDE "اذهب واكتشف ملف p المقابل من تعليق رأس الملف g." بمجرد الانتهاء من ذلك، يقوم المستخدمون فقط بتحرير ملفات p الخاصة بهم كما لو أنه لا يوجد شيء خاص بها. سيشير التجميع التزايدي الفوري إلى أي أخطاء في SystemVerilog أثناء كتابتها، وتأخذها الارتباطات التشعبية حول الكود، ويعمل الإكمال التلقائي وإعادة البناء بشكل جيد، ويمكنهم طلب مخططات مختلفة، وما إلى ذلك.

يتم وضع علامة مميزة على الأقسام التي تحتوي على كود المعالج المسبق حتى يعرف المستخدمون أنه سيتم تحويلها إلى كود SystemVerilog. في DVT الكسوف IDE يمكنهم رؤية كيفية إنشاء التعليمات البرمجية باستخدام طريقة العرض Inspect؛ في DVT IDE لرمز VS يمكنهم "إلقاء نظرة خاطفة" على التحولات. يمكن تكوين DVT IDE لتشغيل البرنامج النصي للمعالجة المسبقة تلقائيًا عند تغيير رمز المعالج المسبق. يمكن للمستخدمين بسهولة مقارنة ملف ap مع ملف g المقابل إذا رغبوا في ذلك.

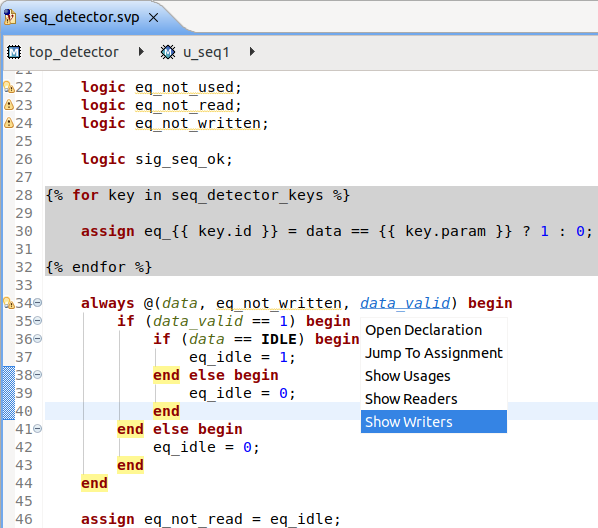

قدم Zeljko ثلاث لقطات شاشة توضح هذه الإمكانية الجديدة أثناء العمل. يعرض الأول أدناه ملفًا في DVT Eclipse IDE يتضمن بيان المعالج المسبق Jinja2. على الرغم من وجود هذا الكود غير التابع لـ SystemVerilog، يستطيع المستخدم الاستفادة من ميزة "إظهار الكتاب" القوية لفهم كيفية تشغيل المتغير بسرعة. تتم الإشارة إلى أخطاء التجميع والتحذيرات في العمود الموجود في أقصى يسار الشاشة.

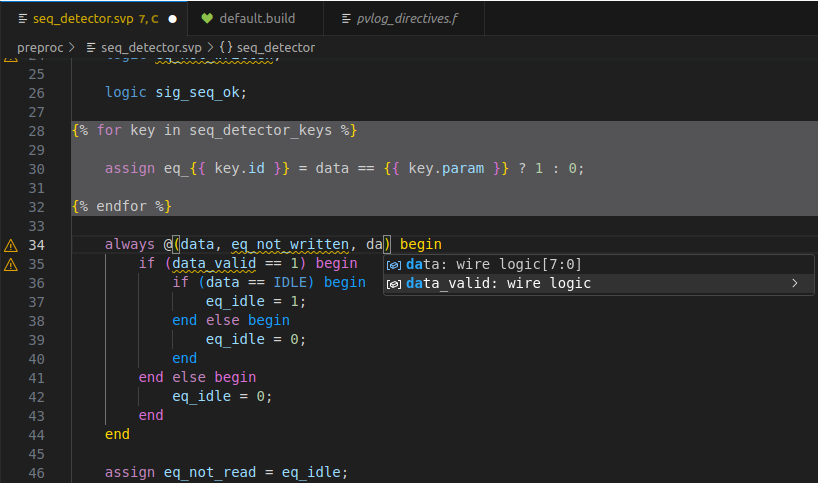

تعرض لقطة الشاشة أدناه نفس الملف في DVT IDE لـ VS Code، مع عرض مشكلات المترجم في العمود الأيسر وتمكين استخدام الإكمال التلقائي. يوضح هذا كيف تتوفر حتى وظائف DVT الأكثر تقدمًا في التعليمات البرمجية مع بيانات المعالج المسبق.

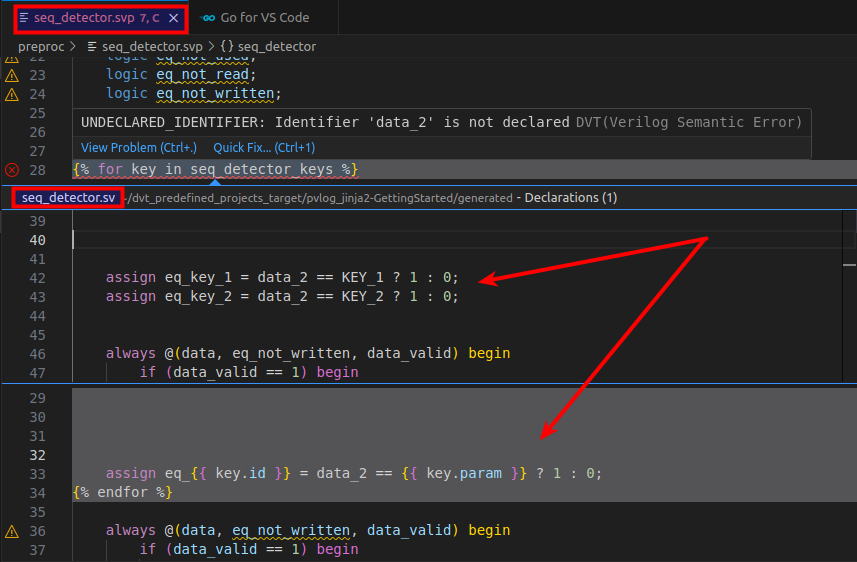

وشدد Zeljko على أن IDE يتحقق من كود SystemVerilog الذي تم إنشاؤه، وهو أمر مهم لأنه قد يكون هناك خطأ في بيان المعالج المسبق أو خطأ في البرنامج النصي للمعالجة المسبقة. تظهر لقطة الشاشة أدناه مثل هذا المثال. يحتوي رمز SystemVerilog الذي تم إنشاؤه على متغير لم يتم تعريفه في الملف المصدر. يعرض DVT IDE خطأ الترجمة والملف p والكود الذي تم إنشاؤه في الملف g.

يمكن أن يكون عرض ملفات g مفيدًا في تصحيح الأخطاء، ولكن خلاصة القول هي أن المستخدمين يعملون مباشرة مع ملفات p، ويقومون بتحليلها وتحريرها باستخدام بيئة تطوير متكاملة (IDE) قوية. يتم وضع علامة على ملفات g على أنها "للقراءة فقط" وسيتم تحذير المستخدمين إذا تم تعديلها. كنت سعيدا لسماع هذا. نعلم جميعًا أنها فكرة سيئة حقًا إجراء تغييرات يدوية على أي ملف سيتم استبداله بواسطة عملية إنشاء التعليمات البرمجية.

أخيرًا، شدد كريستيان على أن الهدف الأساسي من هذه الميزة الجديدة هو أنه يمكن للمستخدمين تحرير التعليمات البرمجية باستخدام بيانات المعالج المسبق تمامًا كما لو كانت SystemVerilog خالصة. إن تحقيق ذلك كان بمثابة جهد كبير مدفوع من قبل عدد قليل من العملاء الرئيسيين الذين يعتمدون على التدفقات القائمة على المعالجات المسبقة. شكرت زيليكو وكريستيان على توضيحاتهما ووقتهما.

إذا كنت ترغب في معرفة المزيد حول استخدام ملفات المعالجة المسبقة أو أي جانب من جوانب حلول AMIQ EDA، فيمكنك زيارتها في الجناح 107 في مؤتمر ومعرض التصميم والتحقق (DVCon) الولايات المتحدة في سان خوسيه، كاليفورنيا يومي 5 و6 مارس.

اقرأ أيضا:

توقعات 2024 مع كريستيان أميترواي، المؤسس والرئيس التنفيذي لشركة AMIQ EDA

استخدام Linting لكتابة كود اختبار خالي من الأخطاء

AMIQ: الاحتفال بمرور 20 عامًا في مجال الاستشارات وEDA

شارك هذا المنشور عبر:

- محتوى مدعوم من تحسين محركات البحث وتوزيع العلاقات العامة. تضخيم اليوم.

- PlatoData.Network Vertical Generative Ai. تمكين نفسك. الوصول هنا.

- أفلاطونايستريم. ذكاء Web3. تضخيم المعرفة. الوصول هنا.

- أفلاطون كربون، كلينتك ، الطاقة، بيئة، شمسي، إدارة المخلفات. الوصول هنا.

- أفلاطون هيلث. التكنولوجيا الحيوية وذكاء التجارب السريرية. الوصول هنا.

- المصدر https://semiwiki.com/eda/amiq-eda/342053-handling-preprocessed-files-in-a-hardware-ide/