Khi bạn nghĩ “FPGA”, bạn nghĩ đến điều gì? Các bộ phận lớn, đắt tiền có khả năng chứa nhiều logic nhưng cũng tiêu tốn nhiều năng lượng. Các nền tảng có thể cấu hình lại có thể sử dụng RTL cho một thiết kế SoC trong quá trình thử nghiệm trước silicon. Những thương vụ mua lại công ty lớn, nơi các nhà đầu tư kiếm được hàng tấn tiền. Bao bì 3D kỳ lạ và kết nối tiên tiến. Nhưng có lẽ không phải là rẻ tiền, gói nhỏ, số lượng pin ít, bộ phận nguồn dự phòng thấp, phải không? eFPGA của Flex Logix quay trở lại những điều cơ bản cho logic có thể lập trình công suất thấp có thể đảm nhận chi phí thấp hơn, âm lượng cao hơn và các thiết bị bị giới hạn về kích thước.

Hai con đường lập trình trình bày một sự lựa chọn

Có nguy cơ tự hẹn hò với chính mình, lần đầu tiên tôi tiếp xúc với cái được gọi là công nghệ FPGA đã trở lại khi Altera đưa ra dòng sản phẩm EP1200 dựa trên EPROM của họ trong gói DIP 40 chân với xung nhịp 16 MHz, công suất hoạt động 400 mW và chế độ chờ 15 mW. quyền lực. Nó đi kèm với một trình chỉnh sửa sơ đồ và một thư viện macro cổng. Các nhà thiết kế sẽ rút ra logic của họ, “đốt cháy” bộ phận của họ, kiểm tra nó, ném nó dưới đèn UV và xóa nó nếu nó không hoạt động, rồi thử lại.

Ngay sau đó, một bảng mạch xuất hiện trong một phòng thí nghiệm khác của chúng tôi với một số FPGA Xilinx đầu tiên. Chúng dựa trên RAM thay vì dựa trên EPROM – lớn hơn, nhanh hơn và lập trình lại mà không cần đợi đèn UV hoặc tháo bộ phận khỏi bo mạch. Logic bên trong cũng phức tạp hơn, với sự ra đời của hệ số nhân nhanh. Những bộ phận này không chỉ quét logic mà còn có thể được sử dụng để khám phá khả năng xử lý tín hiệu kỹ thuật số tùy chỉnh với chu kỳ thiết kế lại nhanh chóng.

Điều đó đã khơi mào cho cuộc chạy đua vũ khí silicon có thể lập trình và sự phân chia được phát triển giữa PLD – thiết bị logic lập trình được – và FPGA. Các nhà sản xuất đã đưa ra các lựa chọn, với Altera và Xilinx đi theo con đường cao về khả năng mở rộng của FPGA và Actel, Lattice, và những người khác đi theo con đường thấp hơn về tính linh hoạt của PLD cho “logic keo” để giảm chi phí hóa đơn vật liệu.

eFPGA thay đổi phương trình logic lập trình năng lượng thấp

Tất cả những điều đó nghe có vẻ giống như một thị trường trưởng thành, với một bên là rào cản gia nhập cao và bên kia là dịch vụ hàng hóa hơn. Nhưng điều gì sẽ xảy ra nếu logic khả trình là một khối IP có thể được thiết kế thành bất kỳ con chip nào trong thời đại không có huyền thoại này – kể cả một FPGA nhỏ, công suất thấp? Điều đó sẽ phá vỡ rào cản (ít nhất là trong các dịch vụ tầm trung và thấp) và hàng hóa hóa.

Flex Logix đã thực hiện thử thách đó với Ngói eFPGA EFLX 1K. Mỗi ô logic có 560 bảng tra cứu sáu đầu vào (LUT) với RAM, xung nhịp và kết nối. Việc sắp xếp các ô EFLX mang lại khả năng xử lý các vai trò logic và DSP khác nhau. Nhưng các tính năng nổi bật nhất của nó có thể là kích thước và khả năng quản lý năng lượng.

Được kết hợp trong TSMC 40ULP, ô xếp EFLX 1K vừa vặn với đường kính 1.5mm2 và cung cấp khả năng kiểm soát năng lượng cho các chế độ ngủ sâu với khả năng duy trì trạng thái – tích cực hơn nhiều so với PLD truyền thống. EFLX 1K cũng có các tính năng sẵn sàng sản xuất mượn từ FPGA. Nó trình bày các giao diện AXI hoặc JTAG cho cấu hình dòng bit, mạch đọc lại cho phép kiểm tra lỗi mềm và chế độ kiểm tra với các vectơ được sắp xếp hợp lý giúp cải thiện vùng phủ sóng và giảm thời gian kiểm tra.

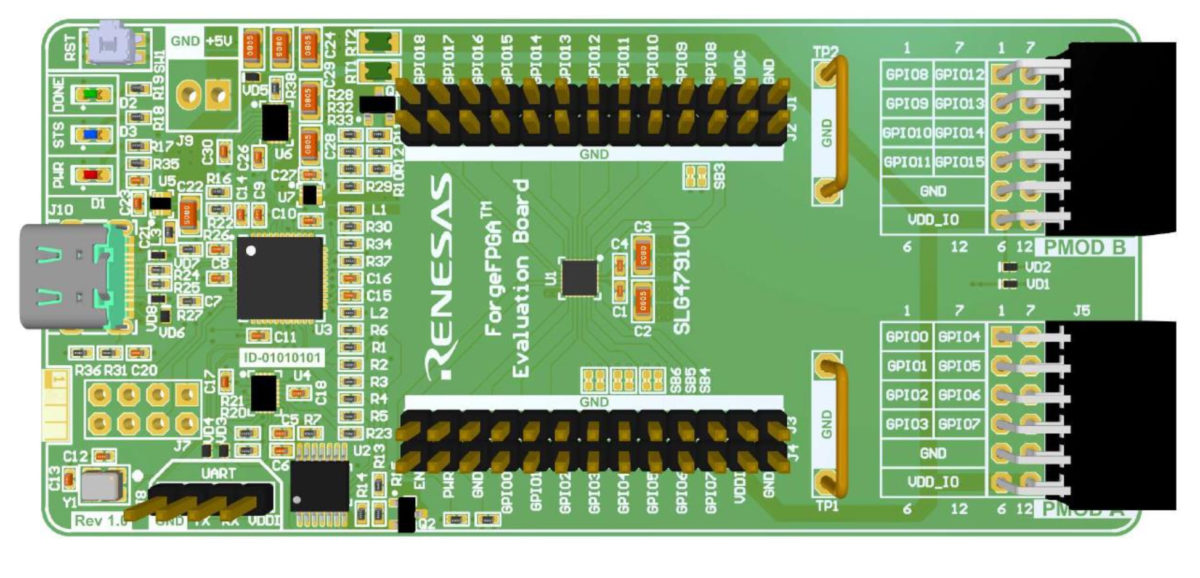

Xem con chip ở trung tâm của hình ảnh tiếp theo này? Đó là một ForgeFPGA từ Renesas trong gói QFN-24, dựa trên EFLX 1K IP, mà Renesas cung cấp với mức giá dưới 1 đô la về số lượng. Kiểm tra hiện tại mục tiêu dự phòng của nó ở mức dưới 20uA. Kích thước nhỏ hơn, chi phí thấp hơn và ít năng lượng hơn mở ra các cánh cửa trước đây đã đóng đối với FPGA. Dòng ForgeFPGA bắt nguồn từ Silego Technology, sau đó là Dialog Semiconductor, được Renesas mua lại vào năm 2021.

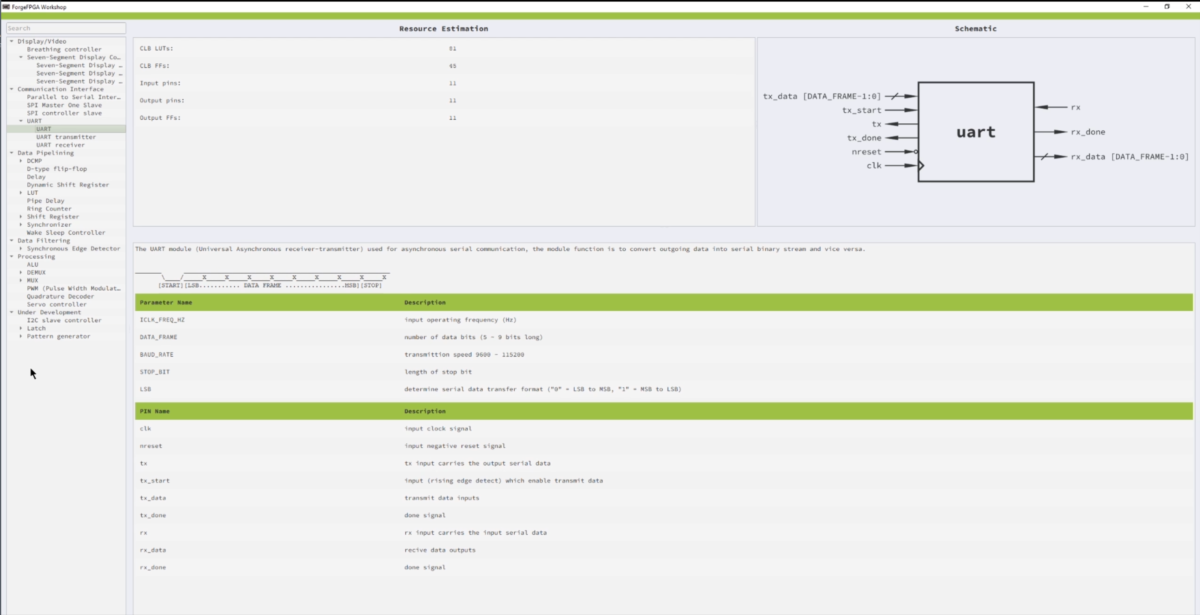

Renesas mang đến môi trường Go Configure IDE, đặt giao diện người dùng đồ họa lên trên trình biên dịch Flex Logix EFLX. Nó hỗ trợ ánh xạ các chân ForgeFPGA, biên dịch Verilog, tạo dòng bit và có bộ phân tích logic nhẹ.

Các khối ứng dụng dựng sẵn cho ForgeFPGA có một khối thú vị mà Geoff Tate của Flex Logix đã chỉ ra: một UART. Tạo một UART theo logic không quá khó, nhưng hóa ra mọi người đã hiểu về nó theo cách khác nhau và nó chỉ đủ logic để có nhiều hơn một vài con chip rời rạc. ForgeFPGA là một đoạn logic có thể cấu hình lại có thể giải quyết vấn đề đó, cho phép triển khai một phần cứng thích ứng nhanh chóng với nhiều cấu hình khác nhau.

ForgeFPGA chỉ là một ví dụ về những gì có thể được thực hiện với Ngói eFPGA Flex Logix EFLX 1K. Flex Logix có thể điều chỉnh IP cho các nút quy trình khác nhau và khả năng sắp xếp kết hợp và kết hợp mang lại khả năng mở rộng. Nó đạt được mức thấp mới cho logic có thể lập trình công suất thấp và cho phép các nhà sản xuất chip phân biệt các giải pháp theo những cách đáng chú ý. Để biết thêm thông tin, vui lòng truy cập:

Cũng đọc:

eFPGA xử lý tính linh hoạt của tiền điện tử cho SoC với PQC

Flex Logix: Hệ thống dựa trên Mini-ITX tích hợp AI đầu tiên của ngành

Đối tác Flex Logix với ID nội tại để bảo mật nền tảng eFPGA

Chia sẻ bài đăng này qua:

- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- Platoblockchain. Web3 Metaverse Intelligence. Khuếch đại kiến thức. Truy cập Tại đây.

- nguồn: https://semiwiki.com/efpga/flex-logix/325926-efpga-goes-back-to-basics-for-low-power-programmable-logic/