Düşük güçlü SoC'lere yönelik aralıksız talep birçok pazarda açıkça görülüyor. Örnekler arasında son teknoloji mobil, IoT ve giyilebilir cihazların yanı sıra yapay zeka ve 5G/6G iletişimlerine yönelik yüksek bilgi işlem talepleri yer alıyor. Düşük gücün etkenleri arasında pil ömrü, termal yönetim ve yüksek bilgi işlem uygulamaları için genel işletim maliyeti yer alır. Düşük güç elde etmek için çeşitli yaklaşımlar mevcuttur. Birçoğunun ortak noktası, optimum Temel IP'ye, yani gömülü belleklere ve mantık kitaplıklarına duyulan ihtiyaçtır. Bu, Synopsys için önemli bir yatırım ve pazar liderliği alanıdır. Mevcut seçenekleri ve faydaları anlamanıza yardımcı olacak iki bilgilendirici yayın artık mevcuttur. Synopsys Foundation IP bellek derleyicileri ve mantık kitaplıklarıyla son derece düşük güce ulaşmanın ulaşılabilir olduğu ortaya çıktı.

Mevcut bilgilere bakalım.

Teknik bülten

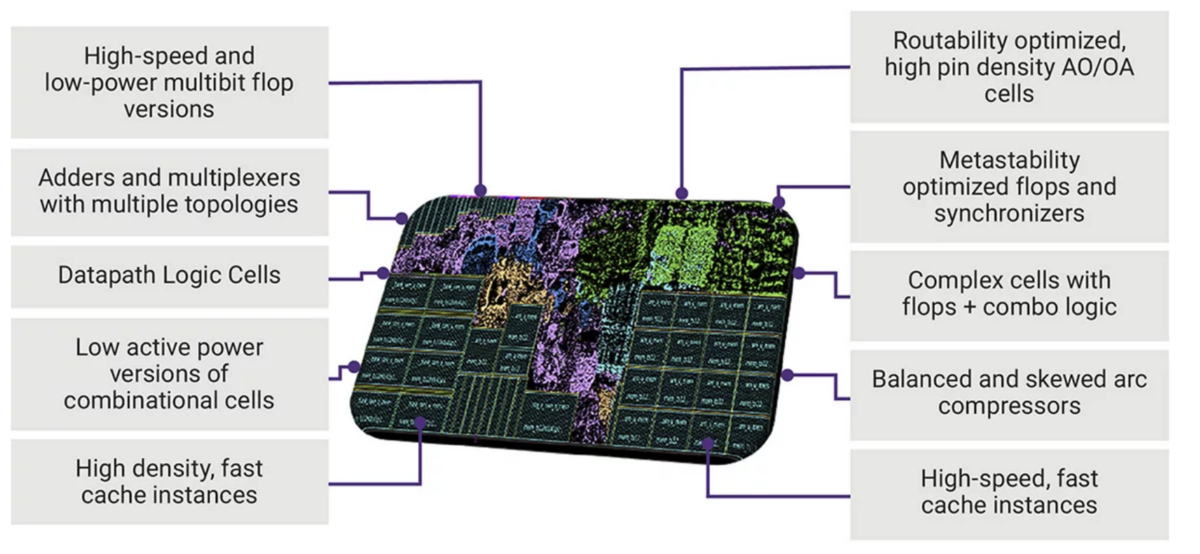

İle başlayacağım Synopsys Foundation IP ile HPC ve Yapay Zeka Uygulamaları için PPA'yı Optimize Etme, mantık kitaplıklarına odaklanan teknik bir bülten. Bu yazıda Synopsys'in araç uyumlu Foundation IP çözümüne ilişkin ayrıntılar verilmektedir. Optimize edilmiş devre sistemi, geniş çalışma voltajı aralığı desteği ve müşteriye özel optimizasyon ekleme esnekliği gibi konular tartışılmaktadır. Makale aynı zamanda mümkün olan maksimum performansın veya en iyi güç-performans dengesinin elde edilmesine yönelik bir bakış açısı da sunmaktadır. Aşağıdaki şekil HPC Tasarım Kitinde bulunan mantık kitaplığı devrelerini özetlemektedir.

Pek çok uygulama ve tasarım stratejisinde güç iyileştirmelerinin nasıl elde edildiğine ilişkin ayrıntılar sağlanmaktadır. İşlenen konular arasında geniş bir çalışma voltajı aralığında dinamik voltaj ölçeklendirme, yapay zeka ve uygulamaya özel hızlandırıcı blok PPA'nın optimize edilmesi, çip üzerinde ağ çözümleri ve verimli SoC Uygulaması için Synopsys HPC Tasarım Kitinin Synopsys EDA ile nasıl birlikte optimize edildiği yer alıyor.

Bu teknik bülten zengin bir dizi bilgi ve örnek sunmaktadır. Yapabilirsiniz bu bilgiye buradan erişin.

Beyaz Kağıt

Ayrıca şu başlıklı kapsamlı bir teknik inceleme de mevcuttur: Ne Kadar Düşebilirsin? Transistörlerin Sınırlarını Zorlamak. Bu parça hem gömülü hafızalara hem de mantık kütüphanelerine giriyor. Aşırı düşük güce ulaşmanın ardındaki ayrıntıları inceliyor. Mobil, Bluetooth ve Nesnelerin İnterneti, yüksek performanslı bilgi işlem, otomotiv ve kripto dahil olmak üzere çeşitli uygulama alanları tartışılıyor.

Gömülü bellekler için, destek teknikleri ve besleme gerilimlerinin bölünmesi dahil olmak üzere çeşitli yaklaşımlar tartışılmaktadır. Düşük voltajlarda yoğun, düşük güçlü bellek operasyonu sağlamak için teknoloji ile bellek yardımcı devrelerinin tasarımı arasında dikkatli bir ortak optimizasyonun gerekli olduğu belirtilmektedir. Çeşitli gelişmiş destek teknikleri gözden geçirilmiştir. Güç aralığında %10 ila %37 arasında iyileştirmeler.

Anıların güvenilirliği de tartışılmaktadır. Parça, voltaj düştükçe SRAM hücresinin bozulma göstermeye başladığını açıklıyor. Bu bozulma birden fazla soruna neden olabilir: okumalar bozulur, bit hücresi değişmez, SER telaffuz edilir, algılama başarısız olur, kontrol sinyalleri sapar ve BL sinyali zayıflar. Bu nedenle, son teknoloji düşük güç uygulamalarının gerektirdiği daha düşük aşırı düşük voltajları desteklemek için yardımcı tekniklere ihtiyaç vardır.

Synopsys'in burada benimsediği yaklaşımlar önemli bir fark yaratıyor. Güvenilirliği artırma stratejileri ve yaşlanmayı simüle etme yöntemleri tartışılmaktadır. Ayrıntıları kendiniz okumalısınız; bir bağlantı geliyor. Veriler, beş ila on yıllık ömrün de eklenmesiyle etkileyici sonuçlar gösteriyor.

Mantık kitaplıkları da 0.4v ve altında derin alçak gerilim çalışmasını mümkün kılacak stratejilerle birlikte tartışılmaktadır. Mimari optimizasyon da gözden geçirilir. Hem dinamik hem de kaçak gücü azaltmak için standart hücre mimarisi teknikleri kullanılabilir. Örneğin Synopsys, derin alçak gerilim işlemi için en uygun topolojiyi sağlamak üzere yığın tabanlı ve aşama tabanlı mimari teknikleri kullanır. Bu yaklaşımın arkasındaki strateji sunulmaktadır.

Karakterizasyon optimizasyonu da kapsanmaktadır. Karakterizasyonun önemli bir parçası, çip üzerinde varyasyon (OCV) olarak adlandırılan, bir SoC genelinde süreç varyasyonunun modellenmesidir. Burada doğruluğu artırmak ve performansı ve gücü optimize etmek için makine öğrenimi de dahil olmak üzere çeşitli gelişmiş teknikler kullanılıyor.

Teknik inceleme, derin alçak gerilim çalışmasını sağlamak için her şeyin SoC seviyesinde nasıl bir araya getirileceğine dair bir genel bakışla sona eriyor. Dinamik voltaj ve frekans ölçeklendirme (DVFS) teknikleri ve hafif uyku, derin uyku, tam kapatma ve POFF (Çevre KAPALI) modları gibi çeşitli kapatma stratejileriyle birlikte voltaj azaltımı tartışılmaktadır.

Bu teknik incelemede çok sayıda güç optimizasyonu konusu mükemmel ayrıntılarla ele alınmaktadır. Şiddetle tavsiye ederim. Yapabilirsiniz kopyanızı buradan alın. Synopsys Foundation IP bellek derleyicileri ve mantık kitaplıkları ile son derece düşük güce ulaşmak işte bu şekilde mümkün oluyor.

Bu gönderiyi şu yolla paylaş:

- SEO Destekli İçerik ve Halkla İlişkiler Dağıtımı. Bugün Gücünüzü Artırın.

- PlatoData.Network Dikey Üretken Yapay Zeka. Kendine güç ver. Buradan Erişin.

- PlatoAiStream. Web3 Zekası. Bilgi Genişletildi. Buradan Erişin.

- PlatoESG. karbon, temiz teknoloji, Enerji, Çevre, Güneş, Atık Yönetimi. Buradan Erişin.

- PlatoSağlık. Biyoteknoloji ve Klinik Araştırmalar Zekası. Buradan Erişin.

- Kaynak: https://semiwiki.com/ip/341966-achieving-extreme-low-power-with-synopsys-foundation-ip-memory-compilers-and-logic-libraries/