RISC-V hareketi, tasarımcılara sunduğu geniş seçenek yelpazesi nedeniyle çok hızlı bir şekilde yükselişe geçti. Ancak muazzam esneklik kendi zorluklarını da yaratır. Bunlardan biri, spesifikasyon sınırları dahilinde izin verilen potansiyel mikro mimari değişiklikleriyle kanıtlanmamış bir RISC-V çekirdek tasarımının nasıl analiz edileceği, optimize edileceği ve doğrulanacağıdır. En iyi FPGA tabanlı prototip oluşturma teknolojisiyle tanınan S2C, #60DAC'de ortaya çıkan sistematik RISC-V mimarisi analizi ve optimizasyon stratejisine modelleme ve emülasyon yeteneği ekleyen bir güncelleme verdi.

RISC-V mimari analizinin üç aşaması

RISC-V, yürütme birimi ve boru hattı yapılandırmalarından özelleştirilmiş talimatların eklenmesine kadar özelleştirmenin ne kadar mümkün olduğu açısından diğer işlemci mimarilerinden farklıdır. Geliştiriciler, bazı tanımların hala belirsiz olduğu birçok uygulamada çeşitli RISC-V yapılandırmalarının en iyi uyumunu araştırıyor. EDA desteği henüz yetişemedi; temel araçlar mevcuttur, ancak birkaç gelişmiş modelleme platformu mevcuttur.

Bu koşullar ekipleri bir sorunla karşı karşıya bırakıyor: Eğer uygulamaları için RISC-V talimat setini genişletirlerse, performansı değerlendirmeden önce, simüle edilmiş veya taklit edilmiş olarak bu talimatlar için döngü açısından doğru yeni modeller oluşturmaları gerekir. S2C, bu boşluğu sistematik RISC-V mimarisi analizi ve optimizasyonu için tanıdık bir teknolojinin iki yanında yer aldığı eksiksiz bir zincirle doldurmaya çalışıyor.

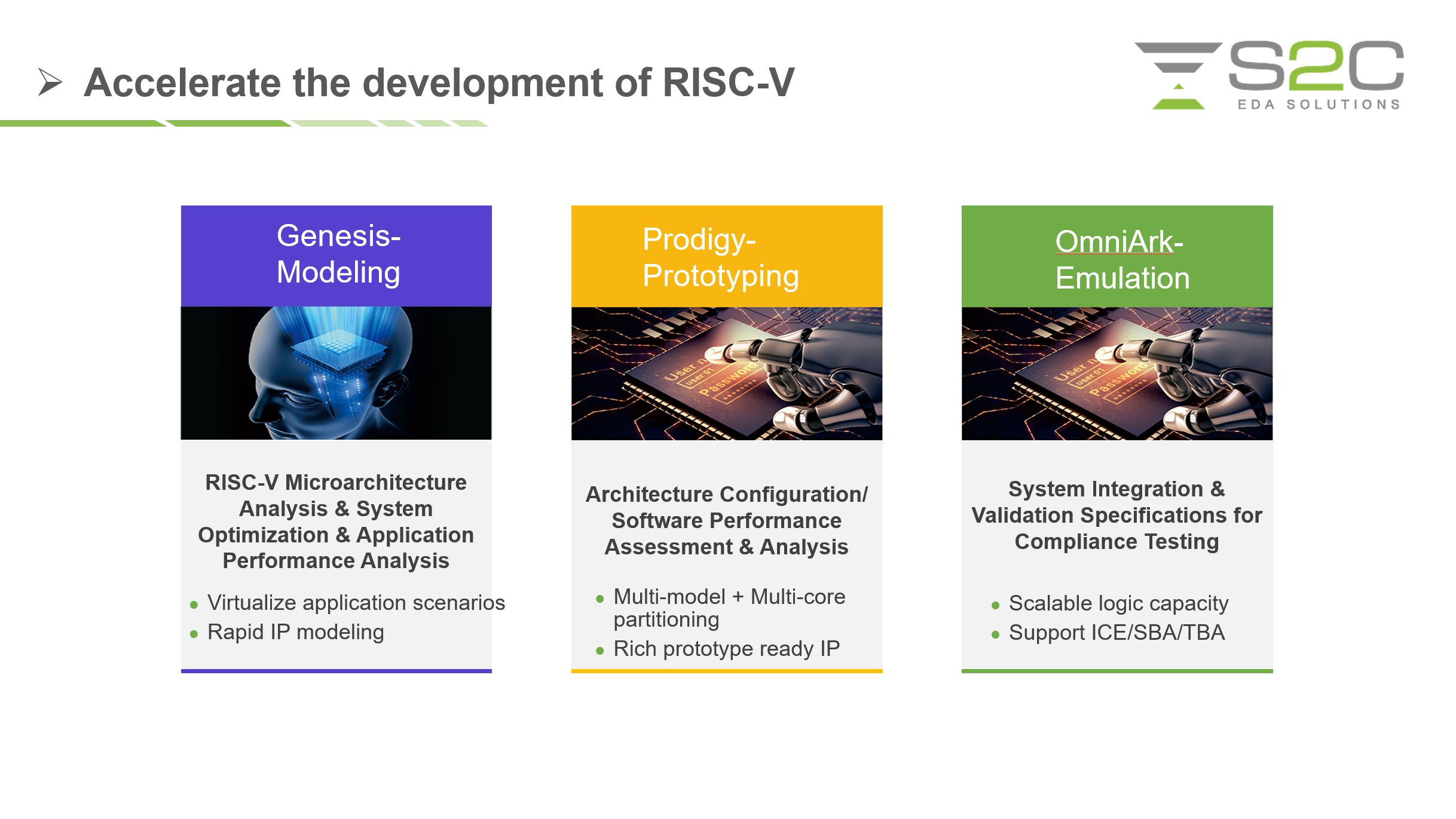

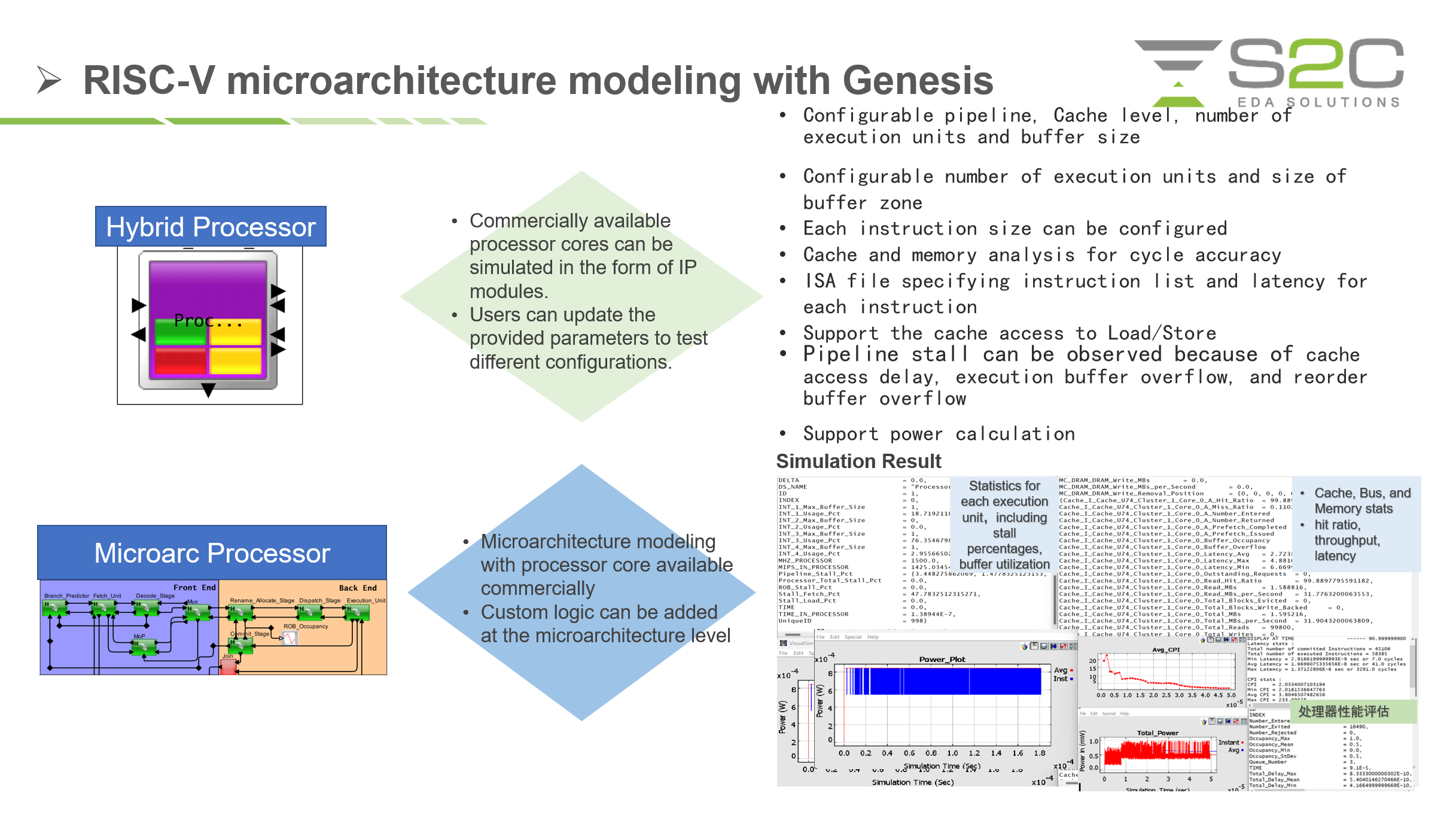

Zincirde ilk olarak S2C'nin yeni RISC-V "çekirdek ana" model soyutlama platformu Genesis yer alıyor. Modeller aslına uygunluk ekledikçe artan doğruluk düzeyleriyle stokastik modelleme, sistem mimarisi modelleme ve döngü açısından hassas modelleme sağlar. Genesis, ticari olarak temin edilebilen RISC-V çekirdeklerinin IP modülleri olarak simülasyonuna, ardından parametrelerin güncellenmesine veya mikro mimariye özel mantık eklenmesine olanak tanır. Bu simülasyonlar çekirdeklerin daha erken optimizasyonuna olanak sağlar.

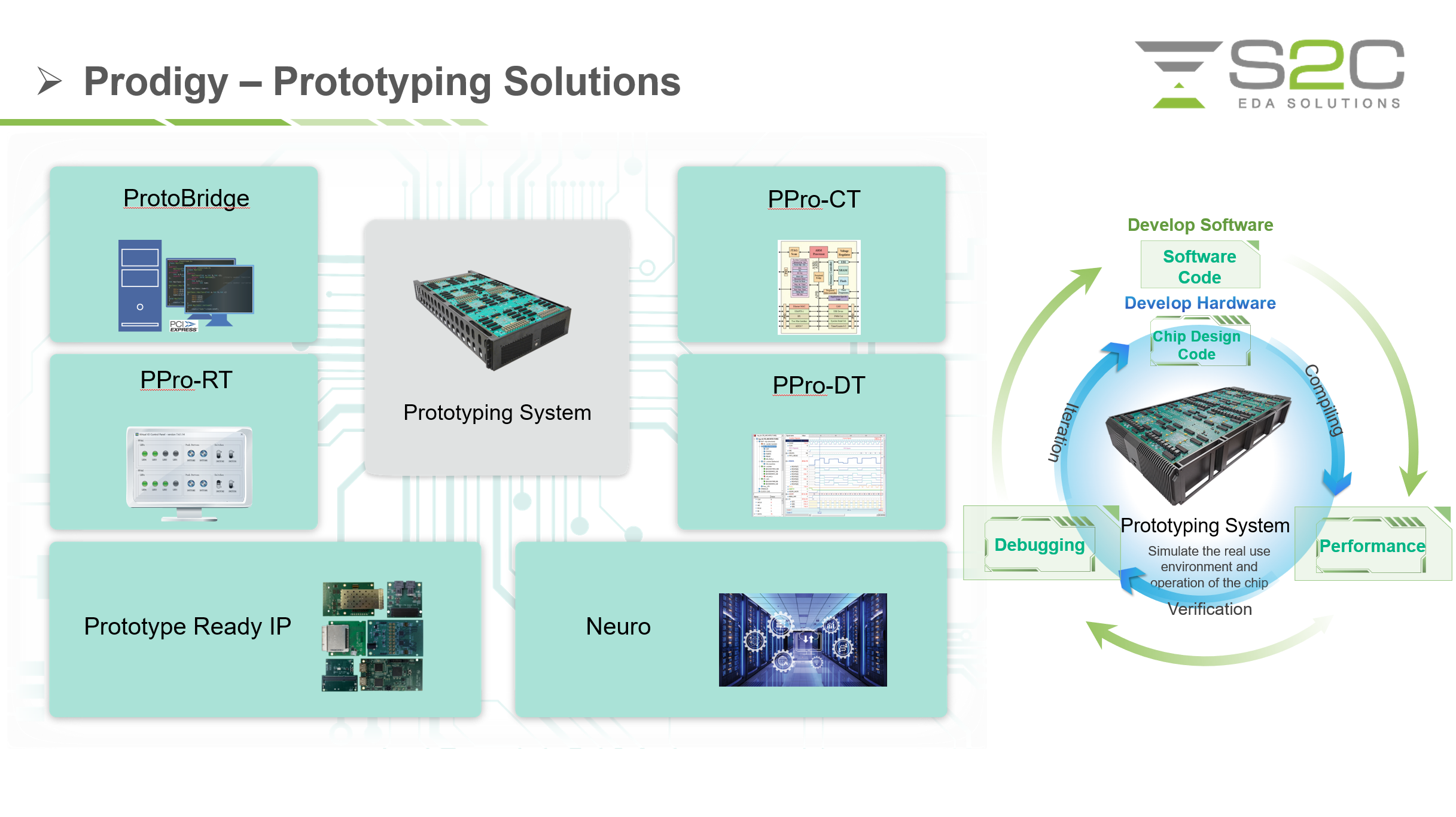

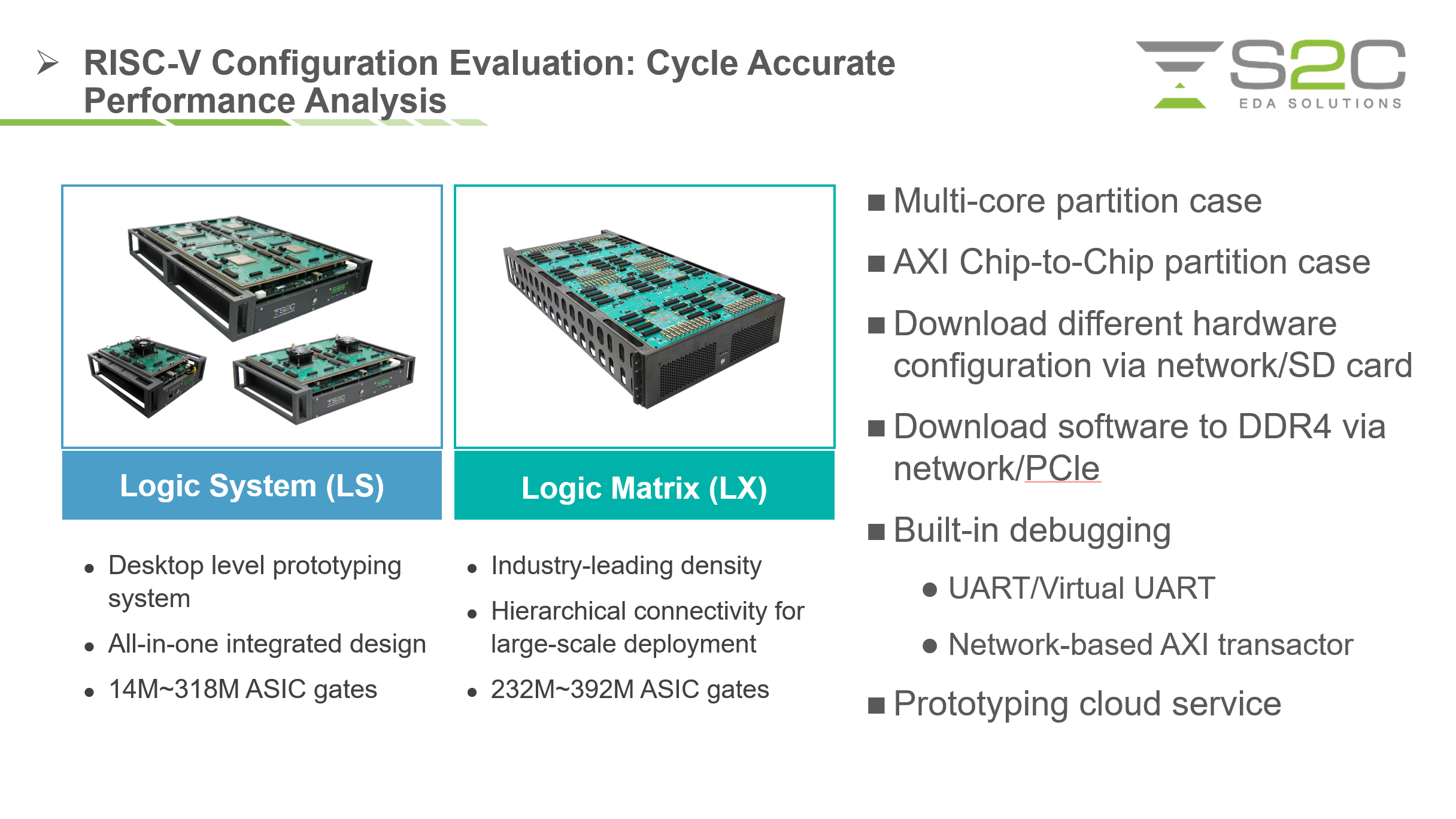

Analiz zincirinin ortasında yer alan S2C Prodigy prototipleme ailesi, donanım mantığında hata ayıklama, temel performans değerlendirmesi ve erken yazılım geliştirme için FPGA tabanlı prototipleri kolaylaştırır. Prodigy prototipleme donanımı, RISC-V IP performans doğrulamasının yanı sıra, SoC'nin çevresi etrafındaki gerçek dünya sinyallerinin uyarılması ve tüketilmesi için S2C tarafından geliştirilen kullanıma hazır I/O modüllerini de kabul eder.

Yeni emülasyon yeteneği, S2C'nin RISC-V SoC'lerin hiper ölçekli doğrulamasını yapabilen OmniArk hibrit emülasyon sistemiyle birlikte geliyor. OmniArk, otomotiv SoC'lerini derleme konusunda uzmanlaşmıştır ve verimli bir doğrulama ortamı için güçlü hata ayıklama yeteneklerine sahiptir. Büyük tasarımlar için 1 milyara kadar kapıyı ölçeklendirir ve QEMU, TBA ve ICE gibi doğrulama modlarını destekler.

Bir örnek: XiangShan RISC-V çekirdek projesinde işbirliği

RISC-V çekirdeklerinin doğru davranış modelleri, erken modelleme, FPGA tabanlı prototip oluşturma ve donanım emülasyon süreçlerinden geçer. Tasarımcılara hem IP hem de modeller üzerinde daha iyi kontrol sağlamak, bir zamanlar yalnızca donanım prototiplerinde mümkün olan görevlerin tasarım döngüsünün başlarında sanal analiz etkinliklerine geçmesini sağlayarak optimizasyon için daha fazla fırsat yaratır.

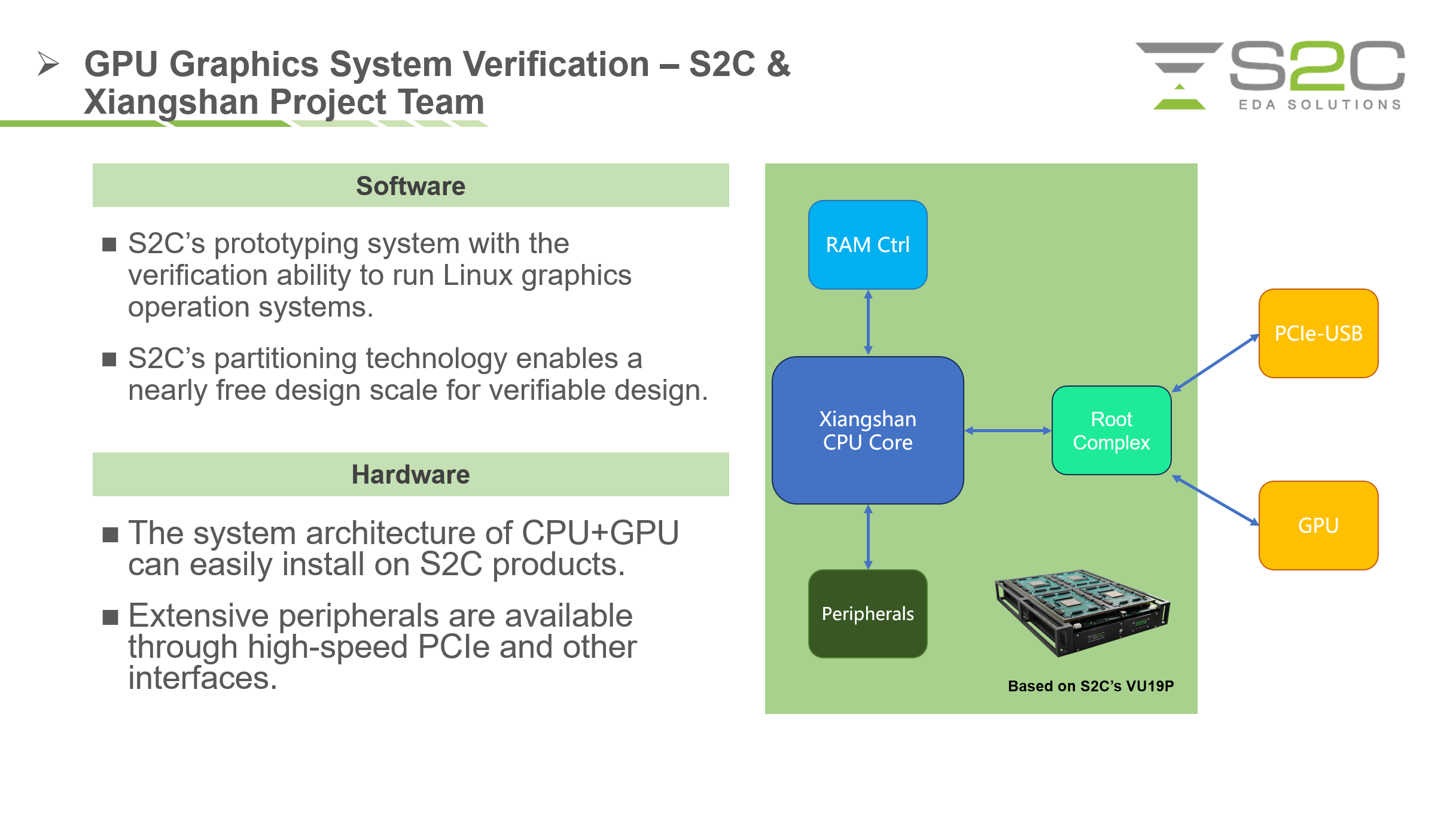

Sistematik RISC-V mimarisi analizi ve optimizasyonunun bir örneği, S2C'nin Çin Bilimler Akademisi merkezli XiangShan proje ekibiyle yaptığı işbirliğidir. XiangShan, işletim sistemi için bir Linux varyantını hedefleyen, süperskalar, altı genişlikli, sıra dışı bir RISC-V uygulamasıdır.

XiangShan ekibi, harici bir GPU ve diğer çevre birimleriyle entegre bir çekirdek doğrulama platformu oluşturmak için S2C ürünlerini kullandı. Hiper ölçekli çekirdek, PCIe ve diğer arayüzler aracılığıyla eklenen çevre birimleriyle S2C FPGA tabanlı bir prototip oluşturma platformuna bölünür.

S2C Başkan Yardımcısı Ying J. Chen, "RISC-V teknolojisi çeşitli alanlara nüfuz ettiğinden, açık kaynağı, anlaşılırlığı ve yüksek ölçeklenebilirliği bilgi işlemin geleceğini yeniden tanımlıyor" diyor. "S2C'nin üç ana ürün grubu, mikro mimari analizi için yazılım performans değerlendirmesi, sistem entegrasyonu ve RISC-V'ye dayalı spesifikasyon uyumluluk testi gibi çeşitli çözümler sağlayabilir."

Yakında S2C'den sistematik RISC-V mimarisi analizi ve optimizasyon zincirinin yaklaşan ABD ürün duyurularıyla nasıl bir araya geldiğine dair daha fazla ayrıntı bekliyoruz - şimdilik S2C'nin Çince dilindeki sitesi Yaratılış hakkında bazı bilgiler. XiangShan RISC-V projesi hakkında daha fazla ayrıntıya şuradan ulaşılabilir: ASPLOS'23'te verilen eğitimler.

Ayrıca Oku:

S2C, Bluetooth LE Audio SoC Geliştirme Zaman Çizelgesini Hızlandırıyor

S2C, Müşterinin Yüksek Performanslı Güvenli GPU Chip Doğrulamasına Ulaşmasına Yardımcı Olur

Bu gönderiyi şu yolla paylaş:

- SEO Destekli İçerik ve Halkla İlişkiler Dağıtımı. Bugün Gücünüzü Artırın.

- PlatoData.Network Dikey Üretken Yapay Zeka. Kendine güç ver. Buradan Erişin.

- PlatoAiStream. Web3 Zekası. Bilgi Genişletildi. Buradan Erişin.

- PlatoESG. Otomotiv / EV'ler, karbon, temiz teknoloji, Enerji, Çevre, Güneş, Atık Yönetimi. Buradan Erişin.

- PlatoSağlık. Biyoteknoloji ve Klinik Araştırmalar Zekası. Buradan Erişin.

- ChartPrime. Ticaret Oyununuzu ChartPrime ile yükseltin. Buradan Erişin.

- Blok Ofsetleri. Çevre Dengeleme Sahipliğini Modernleştirme. Buradan Erişin.

- Kaynak: https://semiwiki.com/prototyping/s2c-eda/333925-systematic-risc-v-architecture-analysis-and-optimization/