Bu yılki DesignCon 2023 etkinliğinde Micron, Karar Geri Bildirim Ekolayzırına duyulan ihtiyaç gibi DDR5 tasarım zorlukları hakkında bir sunum yaptı (DFE) DRAM'in içinde. Siemens EDA ve Micron, konuyla ilgili 25 sayfalık ayrıntılı bir tanıtım yazısı yazmak için bir araya geldi ve ben de bu çok daha kısa blog için en önemli noktaları toplayabildim. DDR5 spesifikasyonu, 2020'de 3200MT/sn'lik bir veri aktarım bant genişliğiyle çıktı ve kanal bozulmalarını hesaba katmak için eşitleme (EQ) devreleri gerektiriyordu.

DFE, Semboller Arası Girişimin etkilerinin üstesinden gelmek için tasarlanmıştır (ISI) ve Micron'daki tasarımcıların DRAM DFE'lerinde saat hızı, Rx göz değerlendirmesi, Bit Hata Oranı (BER) ve titreşim analizini dikkate almaları gerekiyordu. IBIS-AMI modeller, bir EDA aracı istatistiksel simülasyon akışıyla birlikte DDR5 davranışını modellemek için kullanıldı.

DDR5 spesifikasyonunun bir kısmı, DRAM'in Rx'indeki dört dokunuşlu DFE'dir ve DFE, bitlerden herhangi bir ISI'yi kaldırmak için geçmişte alınan bitlere bakar. DFE önce ISI'yi kaldırmak için bir voltaj ofseti uygular, ardından dilimleyici mevcut biti yüksek veya düşük olarak niceler.

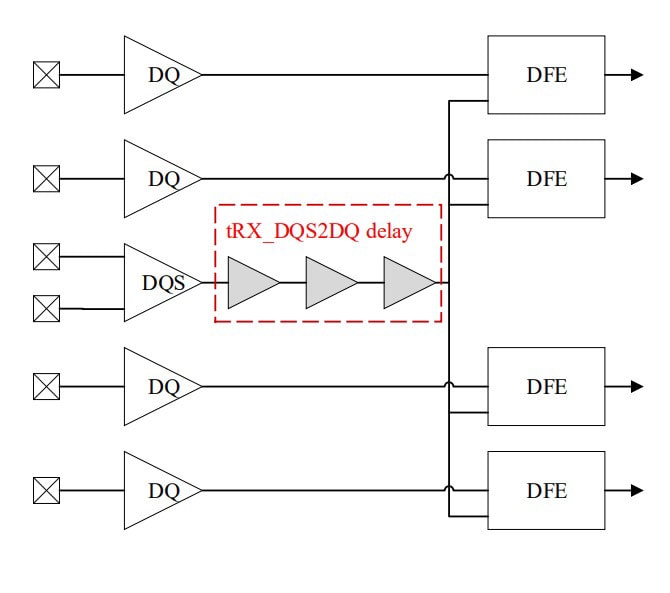

DDR5 ile saat hızı, diferansiyel flaş sinyalidir (DQS_t, DQS_c) ve tek uçlu veri sinyalleri (DQ) boyunca Rx'e iletilir. DQS sinyali arabelleğe alınır ve ardından sekiz adede kadar DQ mandalının saat girişine dağıtılarak bir saat ağacı gecikmesine neden olur.

Maksimum Göz Yüksekliği 95mV ve maksimum Göz Genişliği 0.25 Birim Aralık (UI) veya yalnızca 78.125ps'dir. 1e-16 BER'i ölçmek için istatistiksel bir yaklaşım kullanmak en pratik yöntemdir.

IBIS modelleri, birçok nesil DDR sistemi için kullanılmış olup, uçtan uca sistem simülasyonuna olanak tanımaktadır, ancak DDR5 ek EQ özellikleri ve BER göz maskesi gereksinimleri ile başlayarak, yeni bir simülasyon modeli ve analizi aranmaktadır. IBIS-AMI modelleme ile IO ayrıntılarının IP'sini korurken EDA araçlarında taşınabilir olan hızlı ve doğru Si simülasyonu vardır. IBIS-AMI istatistiksel ve bit-bit simülasyon modlarını destekler ve istatistiksel akış aşağıda gösterilmiştir.

Bu akışın sonucu, farklı BER seviyelerinde göz çevrelerini ölçmek için kullanılabilen istatistiksel bir göz diyagramıdır.

DDR5 Örnek Simülasyonu

Bir DDR5 simülasyonu modellenmiştir. HyperLynx LineSim aracı, Micron tarafından sağlanan DQ ve DQS IBIS-AMI modelleri ile ve işte sistem şeması.

EDA aracı, dalga biçimini belirli saat sürelerinde yakalar; burada, saat sürelerindeki zamanlama belirsizlikleri, sonuçta ortaya çıkan göz diyagramına aktarılır ve dilimleyici ve saati tarafından nicelemeden önce voltajı ve zamanlama marjlarını yeniden oluşturur.

Hem DQS hem de DQ zamanlama belirsizliği, zamanlama marjına benzer şekilde göz diyagramını etkiler. Şekil A, DQ sinyaline enjekte edilen titreşimi gösterir ve şekil B, DQS sinyaline enjekte edilen titreşime sahiptir. DQ (kırmızı) ve DQS (yeşil) titreşimi, şekil C'de birlikte gösterilmiştir.

Sinüzoidal titreşim efektleri, BER ve zamanlama küveti eğrisi sonuçlarını görmek için çeşitli kombinasyonlarda DQ sinyali ve DQS sinyali üzerinde modellenebilir. DDR5, periyot ve döngüden döngüye titreşim ölçümleri yerine Rj, Dj ve Tj ölçümlerine sahiptir. Rx ve Rj değerlerinin BER grafikleri üzerindeki etkisi, zamanlama küveti eğrileriyle birlikte simüle edilebilir.

Doğrusal ve Zamanla Değişmeyen (LTI) modellemenin ötesine geçen Çoklu Kenar Tepkisi (MER) tekniği, bir dizi yükselen ve düşen kenar kullanır. Özel bir gelişmiş IBIS-AMI akışıyla, her bir MER kenarında istatistiksel bir analiz gerçekleştirir ve ardından birleşik etkiyi bir çıktı göz diyagramına yerleştirir.

Modellemeye %2'lik Tx Rj değerlerinin eklenmesi, daha da gerçekçi bozulmuş BER grafiği sonuçlarını gösterir.

Özet

Sinyal Bütünlüğü efektleri bir DDR5 sisteminin tasarımına hakimdir, bu nedenle doğru sonuçlar elde etmek için tüm yeni fiziksel etkilerin ayrıntılı modellenmesini gerektirir. IBS-AMI spesifikasyonu, yönlendirilmiş bir saat kullanmak üzere Rx AMI modelleri için güncellendi. Micron, LTI olmayan etkiler de dahil olmak üzere yeni efektleri modellemek ve 5e-1 ve altı BER ile simülasyonlar elde etmek için saat hızına sahip bir DDR16 simülasyon akışını nasıl kullandıklarını gösterdi.

25 sayfanın tamamını isteyin ve okuyun beyaz kağıt burada çevrimiçi.

İlgili Bloglar

Bu gönderiyi şu yolla paylaş:

- SEO Destekli İçerik ve Halkla İlişkiler Dağıtımı. Bugün Gücünüzü Artırın.

- EVM Finans. Merkezi Olmayan Finans için Birleşik Arayüz. Buradan Erişin.

- Kuantum Medya Grubu. IR/PR Güçlendirilmiş. Buradan Erişin.

- PlatoAiStream. Web3 Veri Zekası. Bilgi Genişletildi. Buradan Erişin.

- Kaynak: https://semiwiki.com/eda/330304-ddr5-design-approach-with-clocked-receivers/