Yüksek frekanslı bir yarı iletken cihazın çeşitli elemanları arasındaki elektromanyetik (EM) bağlantıyı anlamak, tasarım özelliklerini karşılamak ve sahada güvenilir çalışmayı sağlamak için hayati öneme sahiptir. Bu EM etkileşimleri yalnızca silikon çipi değil aynı zamanda onu çevreleyen pakete de uzanıyor. Bununla birlikte, IC veya sistem tasarımcısının hem kalıp üzerindeki metalleri hem de paket katmanlarını içeren EM modellerini oluşturmak ve simüle etmek için devreye girmesi ancak projenin sonuna doğru olabilir. Paket katmanlarının kalıp üstü metal modeline dahil edilmesinin performansta spesifikasyonların ihlal edilmesine neden olabilecek bir bozulmaya neden olduğunu bulmak alışılmadık bir durum değildir. Bunu önlemek için Ansys, tasarım sürecinin erken aşamalarında hem silikon hem de paket katmanlarına sahip komple modelleri çıkarmak amacıyla silikon teknolojisinin metal yığınına paket katmanlarını kolayca ekleyebilen bir çözüm sunuyor.

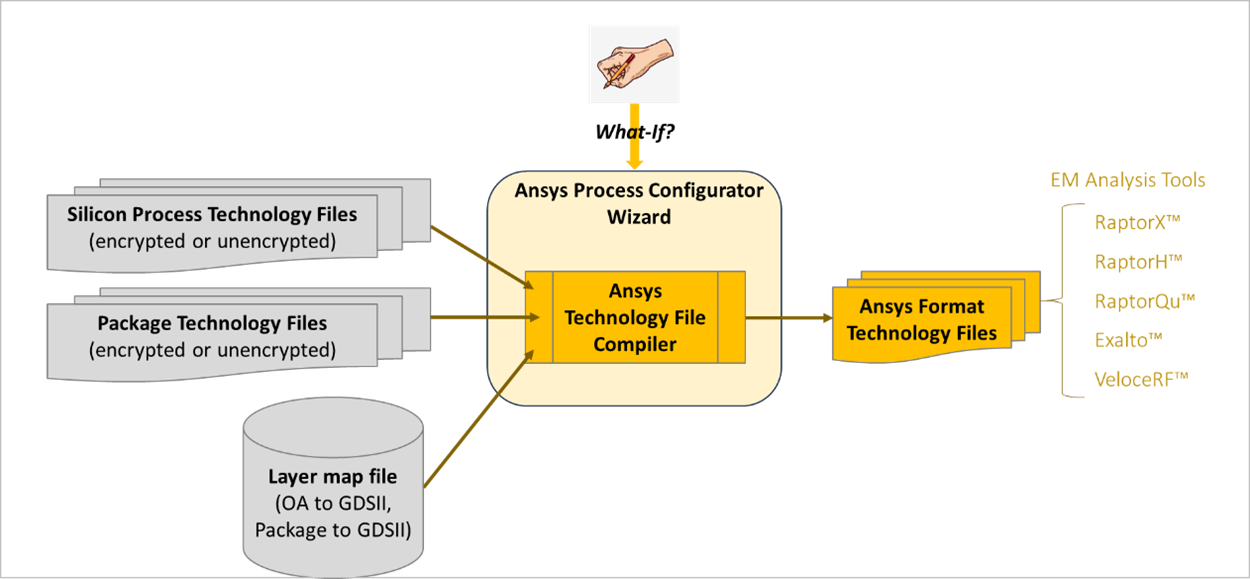

Ansys'in çip üzeri elektromanyetik analiz araçları paketi, LVS öncesi tasarım aşamasında IC düzenleri üzerinde çalışır (Ansys RaptorX™) ve LVS sonrası imza aşaması (Ansys Exalto™). Çip analizi, bir SPICE devre simülatörüyle simüle edilebilecek tam bir EM modelinin çıkarılması için paket düzeninin bölümlerini ve/veya paket katmanlarını içerebilir. Ansys araçları, her katmanın üretiminde kullanılan ara bağlantı proses teknolojisi hakkındaki kesin bilgilere dayanır. Proses bilgileri, silikon dökümhaneleri tarafından, Tasarım Kuralı Kılavuzları (DRM'ler) ve iRCX, ITF ve ICT dosyaları gibi şifrelenmemiş veya şifrelenmiş teknoloji dosyaları dahil olmak üzere çeşitli formatlarda sağlanır. Teknoloji yığınını yakalama süreci, dökümhanenin sağladığı süreç teknolojisi bilgilerini OpenAccess veya GDSII akış formatındaki fiziksel yerleşim bilgileriyle eşleştirerek Ansys formatındaki teknoloji dosyalarının bir koleksiyonunu derler (bkz. Şekil 1). Bu derlenmiş teknoloji dosyaları aynı zamanda Ansys'in çip üzerindeki diğer EM araçlarını da desteklemektedir. Ansys VeloceRF™ (endüktif cihaz düzeni sentezi) ve Ansys RaptorQu™ (süper iletken kuantum tasarımı için).

RaptorX, silikon için optimize edilmiş bir elektromanyetik çözücüdür ve karmaşık yonga paketi yapılandırmaları için bile Ansys teknoloji dosyalarını oluşturmayı ve değiştirmeyi kolaylaştıran İşlem Yapılandırıcı adı verilen çok kullanışlı bir sihirbazla birlikte gelir. Şekil 1'de gösterildiği gibi, Süreç Yapılandırıcı, yalnızca dökümhane metal yığınını içerebilen veya dökümhane metal yığınını artı seçilen ek paket katmanlarını içerebilen Ansys teknoloji dosyaları oluşturur. Dökümhane metal yığını için Proses Yapılandırıcı sihirbazına giriş, dökümhane tarafından sağlanan proses bilgileridir. Kalıp ve paket katmanlarının birlikte çıkarılması gerekiyorsa ilgili katmanlara ilişkin paket katmanı bilgilerinin de dahil edilmesi gerekir.

Dökümhane teknolojisi dosyası şifrelenmemişse veya paket katmanı bilgileri şifrelenmemişse, İşlem Yapılandırıcı sihirbazı kalıp ve/veya paket katmanlarının özelliklerini düzenleyerek ve farklı sürümleri derleyerek süreçle ilgili çeşitli "ya olursa" senaryolarını keşfetmenize olanak sağlar. Ansys teknoloji dosyalarının. Süreç Yapılandırıcı, tasarımcıların alt katmanları, arka panelleri, iletkenleri, dielektrikleri ve İçten Silikon Yollar (TSV) dahil olmak üzere yollar eklemesine veya çıkarmasına olanak tanır. Proses Yapılandırıcı ile düzenlenebilecek teknoloji özellikleri metal kalınlığı, metal iletkenliği, dielektrik kalınlığı ve dielektrik sabitidir. Ansys teknoloji dosyalarını tamamlamak için derleyici ayrıca GDS akış katmanı harita dosyasına ve katman haritalama bilgilerine ihtiyaç duyar.

"Ya şöyle olursa" deneyleri için şifrelenmemiş bir teknolojiyi değiştirmenin bazı örnekleri şunları içerir:

- Substrat boyunca bağlanmanın etkilerini araştırmak için substrat kalınlığını ve özelliklerini değiştirmek

- keşif amaçlı bir 3DIC yığınına TSV'lerin eklenmesi

- Gofret Üzerinde Gofret (WoW) teknolojisi için bir teknoloji dosyası oluşturma

Aşağıdaki örnekte gösterildiği gibi, EM cihazı üzerindeki etkilerini görmek için paket katmanları ekleme

İşlem Yapılandırıcıya yönelik giriş dosyaları ve bilgiler, hem kullanıcı arayüzü hem de toplu mod komut dosyası kullanılarak işlenebilir. Süreç Yapılandırıcının çıktıları, Ansys EM araç paketi tarafından kullanılan derlenmiş Ansys süreç teknolojisi dosyalarıdır. Süreç Yapılandırıcı, teknoloji katmanlarının doğru sırasını ve bağlantısını doğrulamayı kolaylaştıran bir teknoloji kesitini görselleştirme konusunda çok kullanışlı bir yeteneğe sahiptir. Kalınlık, direnç ve dielektrik sabiti gibi şifrelenmemiş teknoloji katmanı özellikleri de kesit görüntüleyicide görüntülenir. Teknoloji şifrelenmişse kesit görüntüleyici katman sırasını ve bağlantısını gösterir, ancak katman kalınlıkları ölçeklendirilmez ve malzeme özellikleri raporlanmaz.

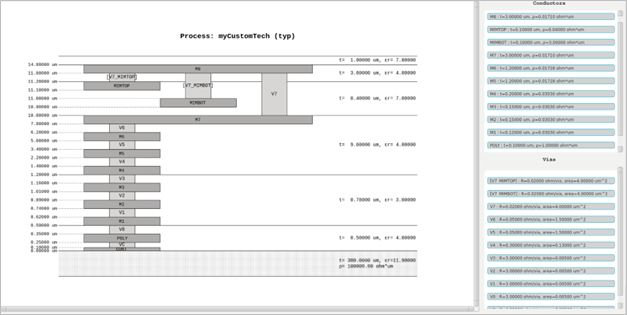

Aşağıdaki Şekil 2, kurgusal bir örnek teknoloji dosyasının yığınını göstermektedir. Sol panel, alt katmandaki alt katman özelliklerini, alt katmandan başlayarak kümülatif katman yüksekliğini, soldaki katman ve yol adlarını ve dielektrik kalınlığını ve dielektrik sabitini (e) görüntüler.r) Sağdaki. Sağ paneldeki İletken bölümü iletkenleri kalınlıkları ve dirençleri (r) ile listeler, Vias bölümü ise geçiş direncini ve alanını gösterir.

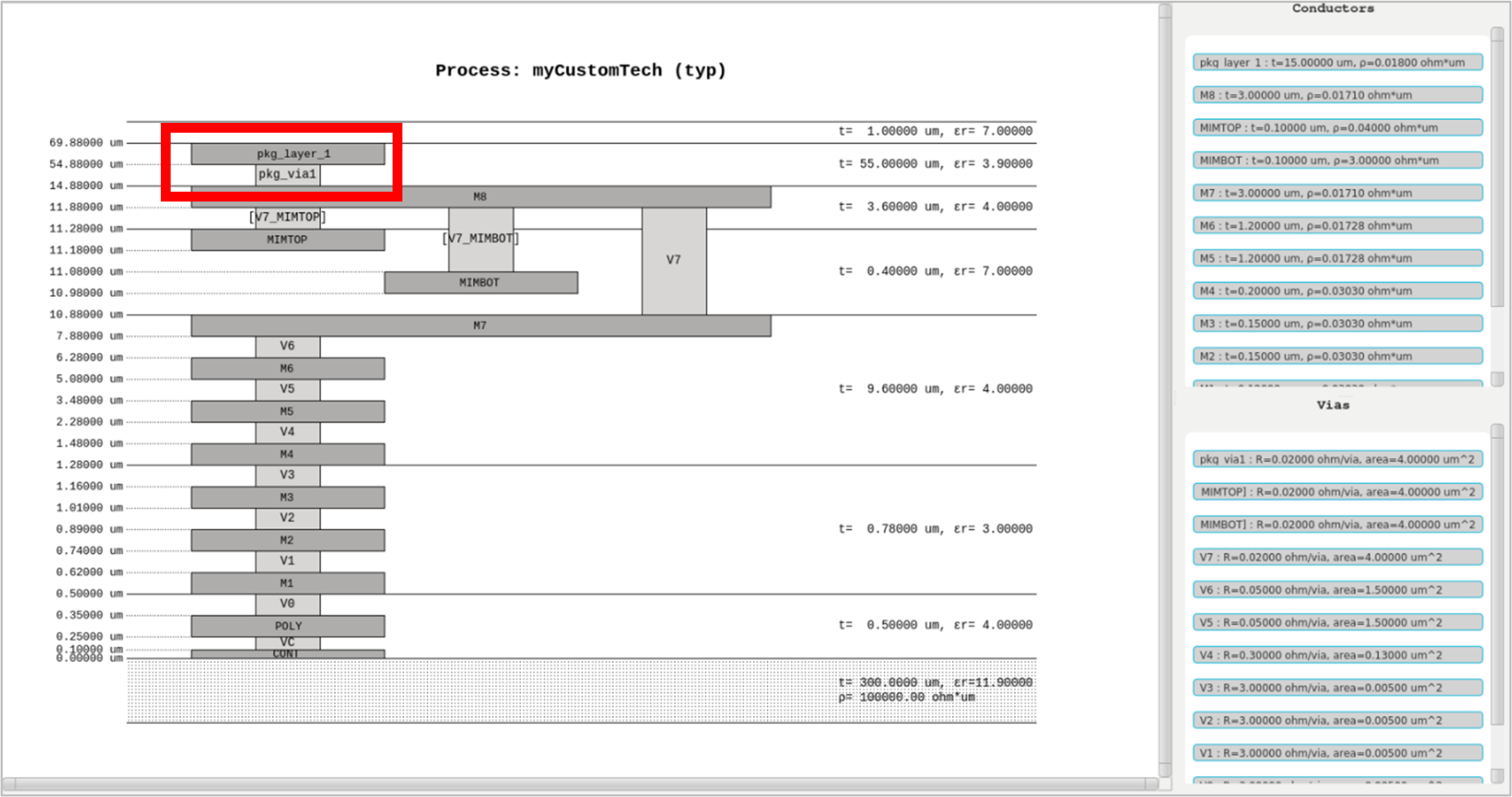

Aşağıdaki Şekil 3'teki kırmızı kutu, yığına eklenen bir yol ve paket katmanını vurgulamaktadır. Paket katmanı ve yoluyla dahil edilen bu yığın, aşağıdaki paragraflarda açıklanan ve paket katmanının bir EM cihazının performansını nasıl etkileyebileceğini gösteren simülasyon sonuçları için kullanıldı.

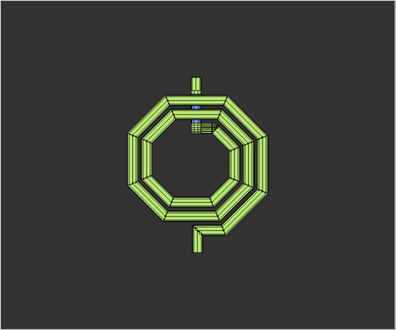

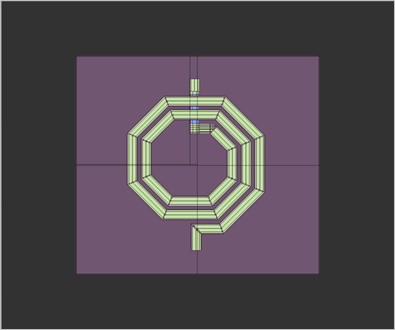

Bir paketin çip üzerindeki etkisini araştırmak için Süreç Yapılandırıcının nasıl kullanılabileceğini göstermek için basit bir düzen örneği oluşturduk: RaptorX kullanılarak çıkarılan bir EM cihazından (tek uçlu sekizgen spiral indüktör) oluşur. Ortaya çıkan elektrik modeli daha sonra SPICE düzeyinde bir devre simülatöründe performansı ilk önce üzerine bir paket katmanı yerleştirilerek ve daha sonra yine paket katmanı olmadan analiz etmek için simüle edildi. Aşağıdaki Şekil 4, paket katmanı olmadan RaptorX'in indüktör için fiziksel ağını göstermektedir.

Daha sonra aynı indüktör kullanıldı, ancak paket katmanının bir dikdörtgeni bunun üzerine yerleştirildi. Aşağıdaki Şekil 5, paket katmanı dahil olmak üzere indüktörün RaptorX ağını göstermektedir.

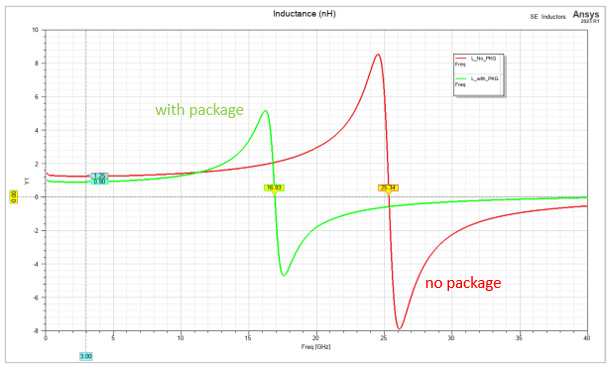

RaptorX, her indüktör için bir S parametresi modeli oluşturdu ve bunlar daha sonra bir frekans aralığında Endüktans ve Kalite Faktörü için simüle edildi. Şekil 6, frekans boyunca çizilen iki indüktörün endüktansını göstermektedir. Dahil edilen paket katmanı (yeşil) için 3 GHz'deki endüktans grafiği karşılaştırıldığında, paket katmanı olmayan model (kırmızı) için simülasyon sonuçlarına kıyasla endüktansta %28'lik bir azalma ve rezonans frekansında %33'lük bir azalma görülmektedir.

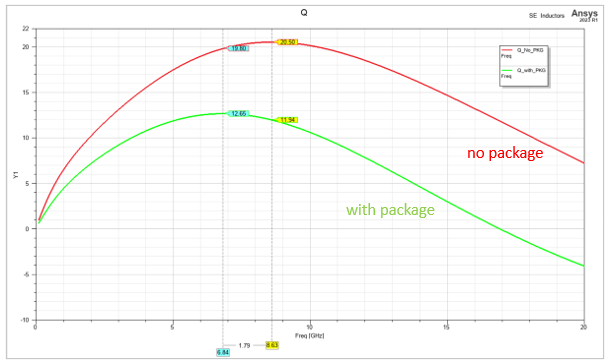

Aşağıdaki Şekil 7'de, iki indüktörün Kalite Faktörü (Q) frekansa göre çizilmiştir. Dahil edilen paket katmanı (yeşil) için Q'nun simülasyon grafiği karşılaştırıldığında, paket katmanı olmayan model (kırmızı) için simülasyon sonuçlarına kıyasla Max Q değerinde %38'lik bir azalma ve maksimum Q tepe frekansında %21'lik bir azalma görülür.

Özetle, bu simülasyon sonuçları, paket katmanları bir simülasyona dahil edildiğinde cihaz davranışında görülen keskin değişiklikleri göstermektedir. Paket katmanlarının kalıp üstü metallerle birlikte modellenmesi, bir spesifikasyonu ihlal edebilecek veya cihazın arızalanmasına neden olabilecek performanstaki bozulmayı ortaya çıkarabilir. Ansys, IC ve Sistem tasarımcılarının en karmaşık çok katmanlı paketleme konfigürasyonlarını bile yakalamasını kolaylaştırmak ve hızlı deneyleri kolaylaştırmak için Süreç Yapılandırıcıyı geliştirdi. Tasarımcıların nihai ürünlerini optimize etmek ve son aşamadaki sürprizlerden kaçınmak için mümkün olan en iyi çözümü bulmalarına yardımcı olmak için erken olası durum araştırmasıyla sola kaydırma yaklaşımını teşvik eder.

Ayrıca Oku:

Bu gönderiyi şu yolla paylaş:

- SEO Destekli İçerik ve Halkla İlişkiler Dağıtımı. Bugün Gücünüzü Artırın.

- PlatoData.Network Dikey Üretken Yapay Zeka. Kendine güç ver. Buradan Erişin.

- PlatoAiStream. Web3 Zekası. Bilgi Genişletildi. Buradan Erişin.

- PlatoESG. karbon, temiz teknoloji, Enerji, Çevre, Güneş, Atık Yönetimi. Buradan Erişin.

- PlatoSağlık. Biyoteknoloji ve Klinik Araştırmalar Zekası. Buradan Erişin.

- Kaynak: https://semiwiki.com/eda/340090-will-the-package-kill-my-high-frequency-chip-design/