Geçmişte analistler, danışmanlar ve diğer birçok uzman, en son süreç teknolojisinde uygulanan yeni bir çipin maliyetini tahmin etmeye çalışıyordu. 3nm düğümüne gelindiğinde yalnızca birkaç şirketin bunları karşılayabileceği ve angstrom aralığına girdiklerinde muhtemelen kimsenin karşılayamayacağı sonucuna vardılar.

Geçtiğimiz birkaç süreç düğümünde çok şey değişti. Artan sayıda startup, yüksek oranda alıntılanan rakamlardan çok daha az parayla başarılı bir şekilde gelişmiş düğüm çipleri üretiyor. Rakamların arkasında çip tasarımı ve üretiminde bazı geniş tabanlı değişiklikler var. Aralarında:

- Gelişmiş düğüm çiplerinin çoğu, AI/ML için kullanılan çoklu biriktirmeli işleme öğelerinin yüksek oranda kopyalanmış dizileridir. Bunlar, farklı bileşenlerin termal sorunlar, gürültü ve çeşitli kullanım durumları ve uygulamalara göre karakterize edilmesi gereken tek bir kalıba entegre edilmesine kıyasla nispeten basittir.

- Bu ilk tahminlerin oluşturulmasından bu yana ana akım haline gelen gelişmiş paketleme, çip üreticilerinin çipleri bir araya getirmesine veya Chiplets Hem maliyetli hem de faydasız olan analog işlevleri 5nm ve ötesine itmeye çalışmak yerine, farklı süreç düğümlerinde geliştirildi.

- Geçmişte, en son düğüme geçmek performans ve güç açısından pazar liderliğini garantiliyordu. Artık durum böyle değil. Olgun düğümlerdeki iyileştirmeler ve donanım ve yazılımı içeren mimari değişiklikler, birçok yonga üreticisinin en yeni düğümlere geçişi en azından bu süreçler maliyet etkin olacak kadar olgunlaşana kadar ertelemesine olanak tanıyor.

İlk tahminlerdeki en büyük sorunlardan biri, bunların o sırada mevcut olan en iyi verilere dayalı tahminler olmasıydı. Başlıca kaynak, 2016'da aşamalı olarak kaldırılan Yarı İletkenler için Uluslararası Teknoloji Yol Haritasıydı. Sonraki yıllarda çip tasarımı ve üretiminin temelleri çarpıcı biçimde değişti.

Örneğin birçok kişi, tüm yeni çiplerin bir retikülü dolduracağını ve tasarımların boyutunun ve karmaşıklığının artmaya devam edeceğini varsaydı. Bazı durumlarda karmaşıklık arttı - en yeni özelliklerin tamamının tek bir retiküle sığacağı noktanın çok ötesine geçti - ancak bu yeni özelliklerin çoğu, en yeni süreç geometrileri ve yerleşik süreç düğümlerinin bir karışımı kullanılarak geliştirildi. Diğerlerinde, bir paketteki işleme öğelerinin sayısı arttı ancak karmaşıklık aslında azaldı.

Yazılım başka bir tanımlayıcı unsurdur. Her yazılımın sıfırdan geliştirilmesi gerekmez. Ayrıca Arm, NVIDIA ve giderek artan şekilde RISC-V tasarımları için önceden var olan çok sayıda araç ve ekosistem mevcuttur. Ve büyük EDA şirketlerinin neredeyse tamamı, özellikle yazılım hata ayıklama ve pekiştirmeli öğrenme yoluyla bir şirket genelinde uzmanlıktan daha etkili bir şekilde yararlanma söz konusu olduğunda, tasarım sürecini hem kısaltmak hem de geliştirmek için AI/ML'ye yoğun yatırım yapıyor.

Sayılar

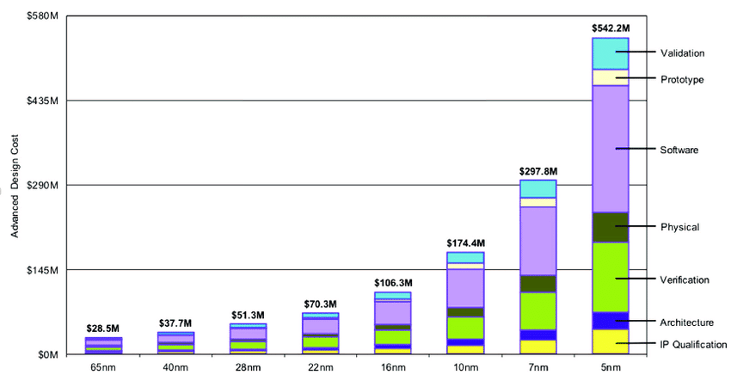

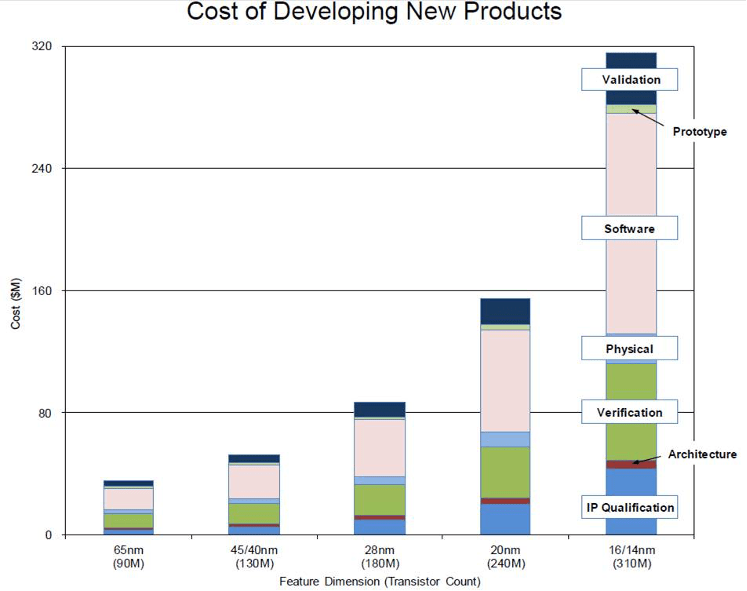

En son 2018 yılında böyle bir tahminde bulunulduğunda, IBS şekil 1'de gösterilen grafiği yayınladı. Bu, 5nm çipin maliyetini 542.2 milyon dolar olarak sabitlemişti. Eğer bu doğru olsaydı, bugün yalnızca iki ya da üç çip üretiliyor olurdu ve muhtemelen hiç kimse 3nm'nin ötesine bakmazdı.

Şekil 1: Yeni bir çip üretmenin maliyeti. Kaynak: IBS 2018

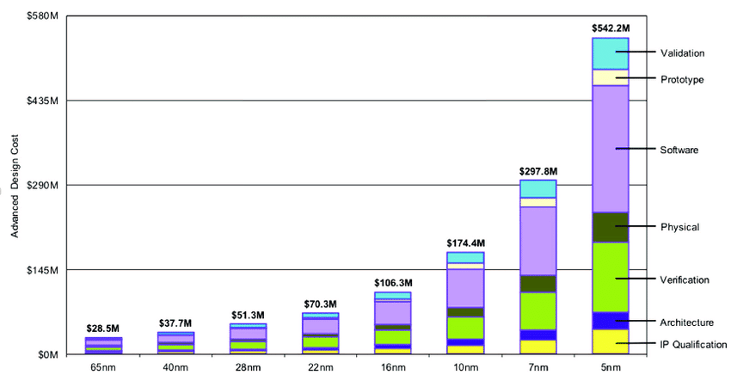

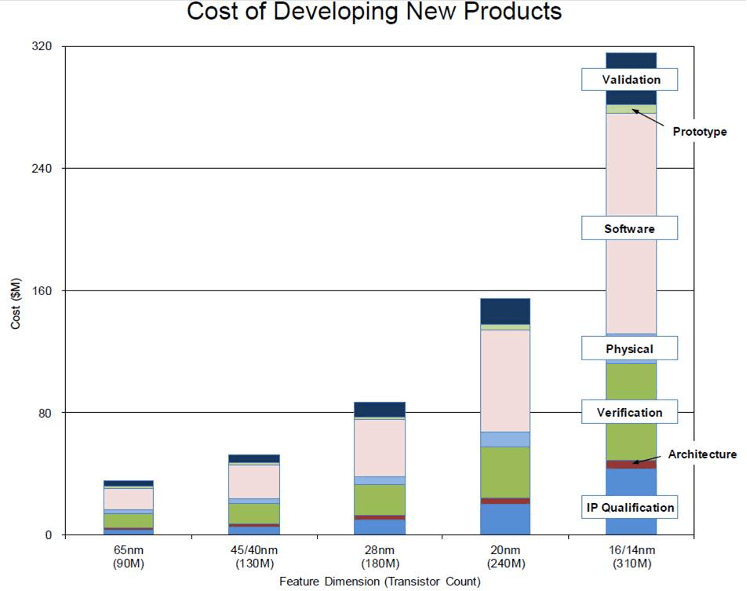

Birkaç yıl geriye gidersek ve bunu IBS'nin 2014'te oluşturduğu tabloyla karşılaştırırsak (bkz. şekil 2), bu tahminlerin zaman içinde nasıl değiştiğini görebiliriz.

Şekil 2: Yeni bir çip üretmenin maliyeti. Kaynak: IBS 2014

16 nm/14 nm'nin tahmini maliyetinin yaklaşık 310 milyon dolardan 106 milyon dolara çıktığını unutmayın. Zamanda daha da geriye gidersek, 28 nm yaklaşık 85 milyon dolardan 51 milyon dolara çıktı. Bunun tahmini maliyetlerde bir aşım mı olduğu, yoksa yeni bir düğüm daha olgunlaştığında maliyetlerde çok keskin bir düşüşü mü yansıttığı tartışma konusudur. Ancak son rakamlar benzer bir miktarda indirilirse, bu, 5nm'lik bir çipin maliyetini 280 milyon dolar aralığına, 7nm'lik bir çipin ise yaklaşık 160 milyon dolara mal olacağını gösteriyor.

Pazarlama ve iş geliştirmeden sorumlu kıdemli direktör Isadore Katz, "Qualcomm veya NVIDIA'yı düşünün" diyor. Siemens Digital Industries Yazılımı. “Eğer yeni bir çip yapmak gerçekten 542 milyon dolara mal olduysa, bunu gerçekten yapabilecek olanlar sadece onlar ve birkaç kişi daha olabilir. Ama 5nm'de bir çip üretmeyecekler. Bir mimariyi alacaklar, yeni süreç düğümüne geçişin bir parçası olarak o mimaride bazı yenilikler yapacaklar ve ardından o süreç düğümünde çalışan bir parça ailesi geliştirecekler."

Çok az şirket gerçek maliyetlerini yayınlıyor, ancak şirketlerin aldığı girişim fonlarına bakabilir ve ilk çipleri piyasaya sürüldüğünde ne kadar para harcadıklarına bakarak kaba bir maliyet bulabilirsiniz. Achronix'in ürün planlamadan sorumlu kıdemli direktörü Nick Ilyadis, "Innovium, ilk çipi için 150 milyon dolar ile inşa edildi ve daha sonra birden fazla nesli finanse eden 100 milyon dolarlık bir tur daha aldı" diyor. “2014 yılında kurulduğundan bu yana Innovium, 402 turda toplam 10 milyon dolar fon aldı ve 145'de Marvell'e 2021 milyar dolara satıldığında elinde hâlâ 1 milyon dolar nakit vardı. Üçüncü nesil çipleri 7 nm'lik bir süreç kullanılarak üretildi."

Maliyetin önemli bir kısmı ilk hamle cezasıdır. Ürün pazarlama müdürü Marc Swinnen, "Büyük dijital çiplerle ilgili harcamalarda patlama yaşandı" diyor Ansys. “Bu büyük manşet rakamları buradan geliyor. Apple'ın yeni bir çip yaratması için gerekenlere bakarsanız, bu 18 ay, yüzlerce tasarımcı, lisans, yepyeni bir maske seti, gelişmiş süreçler. İşte o zaman maliyetler artıyor. Ancak daha eski bir düğümü kullanabiliyorsanız bu maliyetler artık çok daha az.”

Bu rakamlarda gizlenebilecek çeşitli maliyetler de var. Siemens'ten Katz, "Yeni transistör işlevselliğini yeniden karakterize etmek, maske yapma yeteneklerini devreye sokmak, üretim sorunlarını anlamak ve ekstraksiyon modellerini oluşturmak büyük bir yatırım gerektiriyor" diyor. "Ancak önceki düğümlerde öğrenilen derslerden yararlanıyoruz ve bu yapı taşlarını, BSIM-CMG modelini, çıkarma modelini, talaş çeşitlemelerini ve metalleştirmeyi tamamladıktan sonra parametreleştirilmiş, veya üst katmanlarda sahip olduğumuz süreçten bağımsız teknoloji.”

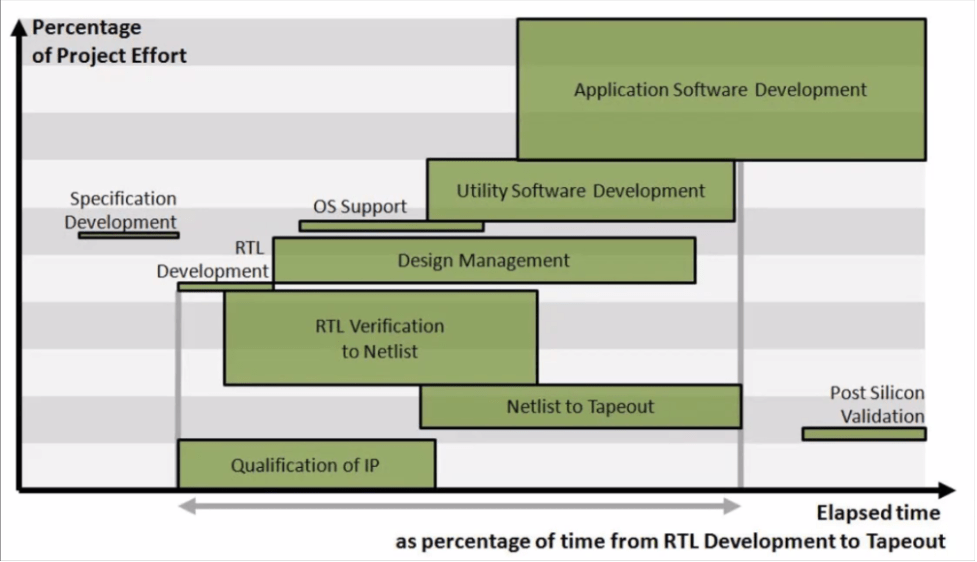

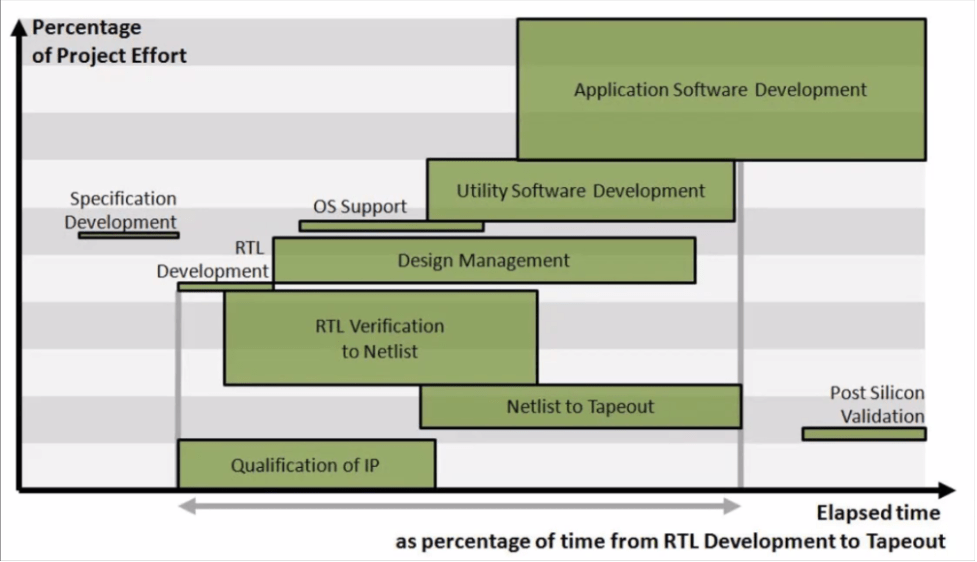

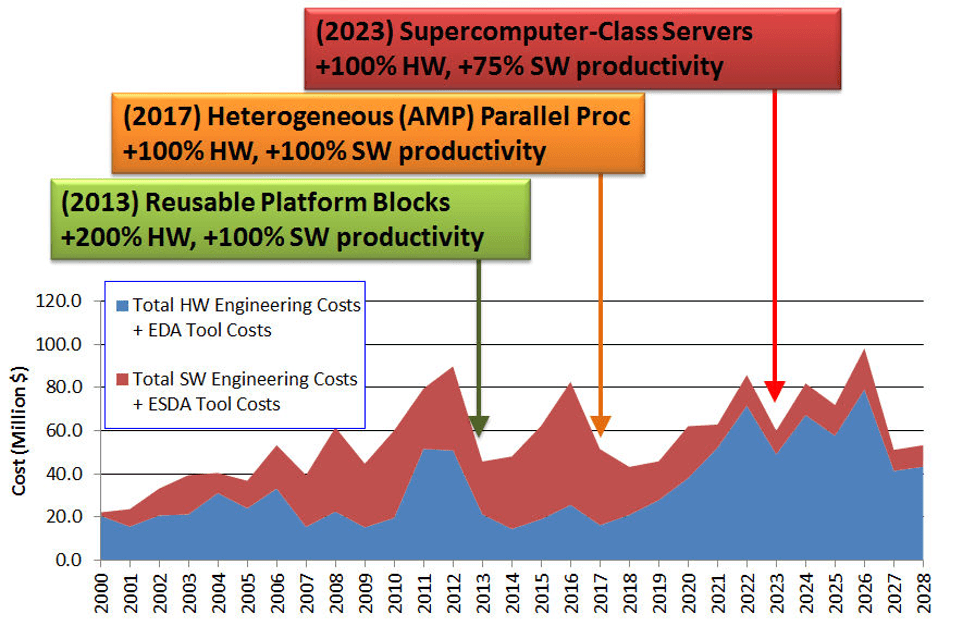

Rakamlar başkalarını da meraklandırdı. Çözümler ve iş geliştirmeden sorumlu başkan yardımcısı Frank Schirrmeister, "Bu, 3 yıl önce oluşturduğum bir grafik (bkz. Şekil 12)" diyor. arterler. "IBS'den dört veya beş veri seti almıştım ancak sayıları yayınlayamadım, bu nedenle oluşturduğum grafik harcama kategorilerinin ortalamasını aldı. Bu çip geliştirmedeki önemli adımları gösteriyor. RTL gelişiminden x ekseni boyunca bant çıkışına kadar bir zaman çizelgesi gösterir. Ve genel proje çabasının yüzdesi y eksenindedir."

Şekil 3: Çip oluşturmak için gereken zaman ve çaba. Kaynak: Frank Schirrmeister

Şekil 3'e dayanarak, bunlardan herhangi birinin zaman içinde değişip değişmediğini veya boyuta veya üretim düğümüne göre ölçeklenip ölçeklenmediğini düşünebilirsiniz. Örneğin, tarihsel olarak bunun doğru olmadığı kanıtlanmış olmasına rağmen, doğrulama maliyetinin boyutla birlikte ikinci dereceden arttığı sıklıkla iddia edilir. Ilyadis, "Doğrulama maliyetleri artıyor, çünkü tasarım ne kadar büyükse, simülasyonu yapmak o kadar uzun sürüyor ve o kadar fazla test senaryosu oluşturmanız gerekiyor" diyor. “Önceki nesillerden kullanabileceğiniz temel testler var ve bunları uygulamaya devam ediyorsunuz. Daha sonra eklenen ek işlevlerle ilişkili yeni testler var. Bu daha fazla sunucu, daha büyük sunucular, daha fazla disk gerektirir. Ek maliyet olarak altyapıya yansıyor.”

Yayınlanan maliyetlere altyapı dahil mi? Arteris'ten Schirrmeister, "Şeytan bu sayıların içinde ne olduğunu anlama konusunda ayrıntıda gizlidir" diyor. “Bütün yazılımlar buna dahil mi? Orada ne kadar yeni RTL gelişimi var? Ne kadar doğrulama? Bir emülatör satın almanız mı gerekiyor? Maskelerin maliyetine baktığınızda, en azından bu çiplerin büyüklük sırasına dokunuyor.”

Bazı maliyetler zamanla azalır. İlyadis, "Fikri mülkiyetin maliyetini düşündüğünüzde, ya kurum içi mühendislik kaynaklarını kullanarak onu geliştirmeniz gerekir, ya da lisans vermeniz gerekir, bu da satıcıya ödeme yapmanız anlamına gelir" diyor. “Genellikle lisanslar destek ve bakımla birlikte gelir; bunlar nakit harcamalardır. Sonra alet maliyetleri var. Yönlendirme daha karmaşık hale geldiğinden veya dikkate alınması gereken ek hususlar olduğundan, her nesil yeni bir araç seti gerektirir. Çipi geliştiren ekibin çalışan sayısı var. Ayrıca test donanımları ve hatta çipinizi gösterecek bir ürün oluşturmanız gerekir. Şimdi çipin kendisinin dışına çıkıyoruz, ancak bunların hepsi gerçek çip gelişimiyle ve onu pazara sunmak için neye ihtiyacınız olduğuyla ilgili. Sonra vermeye devam eden bir hediye var: yazılım. Bu çiplerin çoğu bir çeşit programlanabilirliğe sahiptir. Bunun da ötesinde, hızlandırılmış ömür testleri yapmak için test cihazları, test fikstürleri ve yanma fikstürleri de dahil olmak üzere üretim var."

Fikri mülkiyet maliyetleri bile önemli bir değişken olabilir; özellikle fikri mülkiyet satın alma yoluyla kazanılan zaman tasarrufunu veya fikri mülkiyeti geliştirmeyle ilişkili dolaylı maliyetleri dikkate alırsanız. Ürün Yönetimi Kıdemli Direktörü Brian Jeff, "SoC tasarımlarının maliyetindeki ve karmaşıklığındaki artış, bilgi işlem altyapısı üzerinde daha fazla baskı oluşturuyor" diyor. KolAltyapı İş Kolu. "Bu, belirli iş yükleri için özel işlem sağlamak ve ölçekte verimlilik tasarrufu elde etmek için özel silikona yönelik bir trendi tetikliyor. IP'yi özelleştirilebilir bir temelle geliştirerek, IP sağlayıcısının, iş ortaklarının tasarım sonrası tasarımı tekrarlamak zorunda kaldığı ortak entegrasyon, doğrulama ve doğrulama görevlerinin çoğunu üstlenmesine olanak tanır. Bu, iş ortaklarının kaynaklarını, iş yüklerine göre tam bir çip tasarımını farklılaştırmalarına ve şekillendirmelerine yardımcı olacak özellikler üzerinde yoğunlaştırmalarını sağlar. Bir örnekte, bir iş ortağı üst düzey altyapı SoC geliştirme maliyetini 80 mühendislik yılı kadar azalttı."

Maliyetlerin çoğu artımlıdır. Katz, "Süreç düğümleri arasındaki her şeyi yeniden öğrenmiyoruz" diyor. "Yapmamız gereken şeyleri hatırlıyoruz. Parametrelendirmeye veya tasarım eserlerinin en baştan itibaren temsil edilmesine, test tezgahına, IP'yi tanımlama şeklimize ve özel mantığı ve hızlandırıcıları nasıl düzenlediğimize kadar ifade etme şeklimize çok yatırım yaptık. hücreler. Nerede ayarlama yapmamız gerektiğini anlıyoruz ve bunu düzeltebileceğimiz kadranlara ve düğmelere sahibiz. Düğümler arasında kimse sıfırdan başlamaz. Transistör yüzeylerinin çalışma şeklini değiştirsek veya birinci seviye kişiselleştirme metalinin çalışma şeklini yeniden düzenlesek bile, bunun için karakterizasyona fazladan zaman harcamamız gerekiyor. Bunu nasıl çıkaracağımızı anlamak için fazladan zaman harcamamız gerekiyor ve buna uyum sağlamak için hücre tasarımlarımızda küçük ve mütevazı değişiklikler yapmamız gerekebilir. Ancak temel topoloji ortada.”

İyi geliştirilmiş IP, birden fazla nesil çipte yeniden kullanılabilir. Intel, AMD, Marvell, Broadcom, NVIDIA ve Qualcomm gibi şirketler IP'lerinin çoğunu kendi bünyesinde geliştiriyor. Bunların bir kısmı tamamen karakterize edilebilen ve önceden belirlenmiş mimarilerde yeniden kullanılabilen yongalar biçimindedir. Buradaki ödünleşim şirket içi uzmanlıktır, ancak aynı zamanda alanda daha az sürpriz vardır ve lisans maliyeti yoktur.

EDA'nın Maliyeti

Her düğüm bazı yeni sorunlar ve zorluklar yaratır ve bu da genellikle EDA satıcılarının yeni araçlara veya akışların oluşturulmasına önemli miktarda yatırım yapmasını gerektirir. Düğüm yeni olduğunda, bu araçların çoğu kabadır ve çözümler, soruna çözüm getirebilecek teknolojilerle birlikte bir araya getirilir.

Zamanla sektör neyin işe yarayıp neyin yaramadığını öğrenir, akışlar iyileşir ve sonunda otomatikleşir. Ansys'ten Swinnen, "Birçok zorluğun üstesinden kaba kuvvetle gelinir" diyor. “Mevcut araçları aldılar ve yeterli sayıda insanla çalıştırdılar. Bu, satıcılarla yakın işbirliğini gerektiriyordu. Bu, sıradan ana akım yonga tasarımcılarına verebileceğiniz bir akış değil. Zamanla biz onlardan, onlar da bizden öğreniyorlar. Aletler daha iyi hale geliyor, daha otomatik hale geliyor, pürüzlü kenarlar düzeltiliyor, aradaki manuel adımlar azaltılıyor. Bu da verimliliği çok daha yüksek hale getiriyor.”

Ancak bugün işe yarayan şey gelecekte işe yaramayabilir. Katz, "Planlamanız gereken bir portföy var" diyor. “Zamanlama, süreç değişimi ve yerden sıçrama konularına dahil oldum. Gerilim eşiklerinizi 1V'un altına düşürdüğünüzde bunların çoğu sorun haline gelir. 14 nm'ye girdiğimizde bu bilinmiyordu. Bugün anlaşıldı. İnsanlar tasarımın zamanlamasında veya düzeninde neyin yanlış gidebileceğini anlıyorlar. Metallerin gecikme ve zamanlamaya katkısı konusunda dikkat etmeniz gereken faktörleri anlıyorlar ve aynı zamanda bazı fiziksel yan etkiler, aksaklık gürültüsüne karşı hassasiyet, sızıntı. Bunların hepsi oyun kitabına eklenir. Ve başucu kitabı size son 10 veya 15 yılda yaşanan olayların her birinde yol gösteriyor. Bunları nasıl ele alıyorsunuz? Bunları nasıl otomatikleştirirsiniz? Veya bunları nasıl tasarlıyorsunuz?”

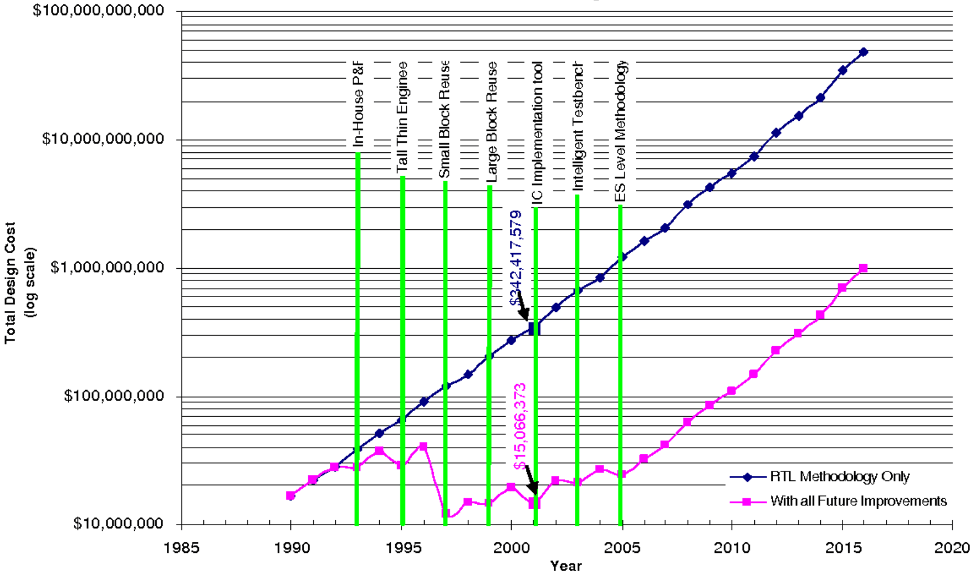

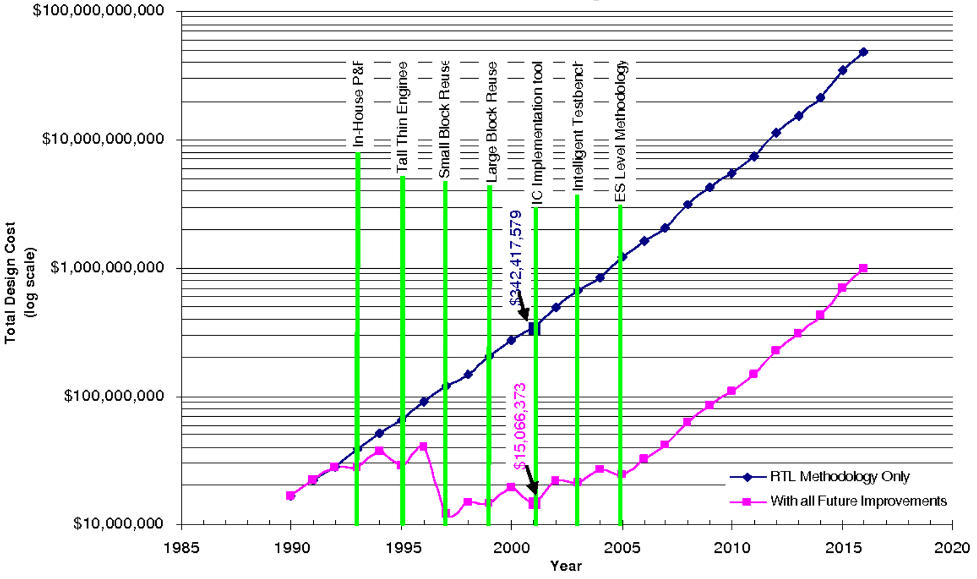

Yeniden incelemeye değer başka bir eski grafik şekil 4'te gösterilmektedir. Andrew Kahng ve Gary Smith, yeni EDA gelişmelerinin üretkenliği nasıl etkilediğini göstermek için 2001 yılında tasarım maliyetleri analizi yaptılar. Bu, ITRS tarafından 2002 yılında yayımlandı.

Şekil 4: 2001 ITRS için yeni bir tasarım maliyet modeli. Kaynak: Bildiriler Uluslararası Kaliteli Elektronik Tasarım Sempozyumu 2002

Bu, ESL gibi geleceğin teknolojilerinin hiçbir zaman ortaya çıkmadığını gösterirken diğer teknolojilerin ortaya çıktığını gösteriyor. ITRS'nin sonraki yayınları, geliştirme maliyetlerinin biraz sabit kaldığını ve zaman içinde yalnızca hafif bir maliyet artışı gösterdiğini göstermektedir. Şekil 5 (aşağıda) 2013 yılına ait çizelgedir.

Şekil 5: EDA'nın Entegre Devre Tasarım Maliyetine Etkisi. Kaynak: Andrew Kahng, 2013

Geliştirme maliyetleri özellikle yeni düğümler için artıyor. İlyadis, "Araçlar giderek daha karmaşık hale geliyor ve tasarım boyutuna göre ölçeklenmesi gerekiyor" diyor. "Genellikle güncellenen bu araçlar nesilden nesile %25 maliyet katabilir ve alet şirketleri buradan para kazanıyor. Geliştirmeleri gerekiyor, araçlarını yeni nesil fikri mülkiyetle ve ortaya çıkan yeni zorluklarla uyumlu hale getirmek için çalışmalılar, dolayısıyla bu geliştirme maliyetini artan lisans ücreti olarak size yansıtacaklar."

Ancak ana akım geliştiriciler için durum böyle değil. Swinnen, "Yarı iletken tasarımının ekonomisinde, EDA araçlarının maliyeti hiçbir zaman önemli bir husus değildir" diyor. "Bu, birisinin endişelenmesi gereken bir maliyet unsurudur, ancak çip tasarımının genel ekonomisinde EDA hiçbir zaman belirleyici faktör değildir. Üretimdir. EDA'nın tasarımın maliyetini etkilediği nokta daha çok üretkenliktir."

EDA araçlarıyla ilgili altyapı maliyetlerinin hızla arttığını görüyoruz. Schirrmeister, "Yapay zekanın araç paketlerine dahil edilmesiyle tasarım alanında daha fazla keşif yapmaya başlamak kolaylaşıyor" diyor. "Grafiklerindeki her veri noktası, ek kapasite ve bulutta çalışan döngüler anlamına geliyor. En iyi uygulamayı elde etmek için artık daha fazla işlem gücü harcıyorsunuz. Eskiden insan sayısının zamanla ve bir miktar altyapı maliyetiyle çarpımı olan şey, artık maliyetlerin yeniden dağıtımına dönüşüyor ve hesaplama maliyetinin kendisi genel maliyet denkleminde çok daha yüksek bir rol üstleniyor."

Sonuç

Şimdiye kadar geliştirilen hiçbir çip, yayınlanan rakamlarda gösterilen maliyete sahip olmadı çünkü gerçekten boş bir kağıt sayfasıyla başlayan bir çip yok. Bu sektördeki her şey fikri mülkiyetin yeniden kullanımına dayanıyor; bir kısmı IP bloklarına, bir kısmı BSIM modellerine, bir kısmı da yeni bir şirket kuran mühendislerin kafalarına bağlı. Daha fazlası olmasa da aynı şey, her zaman devasa kod kütüphaneleri üzerine inşa edilen yazılım endüstrisi için de söylenebilir.

Ancak bu sayılar öncü tasarımlar için doğru büyüklük sırasına sahiptir. Yalnızca silikon bant çıkarmaya odaklanmak değil, geliştirmeyle ilgili toplam maliyetleri anlamak önemlidir.

- SEO Destekli İçerik ve Halkla İlişkiler Dağıtımı. Bugün Gücünüzü Artırın.

- PlatoData.Network Dikey Üretken Yapay Zeka. Kendine güç ver. Buradan Erişin.

- PlatoAiStream. Web3 Zekası. Bilgi Genişletildi. Buradan Erişin.

- PlatoESG. karbon, temiz teknoloji, Enerji, Çevre, Güneş, Atık Yönetimi. Buradan Erişin.

- PlatoSağlık. Biyoteknoloji ve Klinik Araştırmalar Zekası. Buradan Erişin.

- Kaynak: https://semiengineering.com/what-will-that-chip-cost/