2024 SEMI Uluslararası Strateji Sempozyumu için organizasyon komitesi üyeleri beni teknoloji, ekonomi ve sürdürülebilirlik perspektifinden mantığın on yıl içinde nerede olacağına bakmaya davet etti. Aşağıda sunumumla ilgili bir tartışma yer almaktadır.

Mantığı anlamak için, öncü mantık aygıtlarını neyin oluşturduğunu anlamanın faydalı olduğuna inanıyorum. TechInsights ayrıntılı ayak izi analizi raporları hazırlıyor ve ben Intel ve AMD mikroişlemciler, Apple A serisi ve M serisi işlemciler, bir NVIDIA GPU ve diğer cihazlar dahil olmak üzere on adet 7nm ve 5nm sınıfı cihaz için raporlar aldım. Şekil 1 kalıp alanını neyin oluşturduğunu göstermektedir.

Şekil 1'de mantık kalıp alanının yarısından biraz daha azını oluşturur, bellek kalıbın üçte birinden biraz daha azını ve G/Ç, analog ve diğer dengeyi oluşturur. Gerçekte ölçülen SRAM bellek alanlarının, insanların Çip Üzerindeki Sistem (SOC) ürünleri için hakkında konuştuğunu duyduğum yüzdeden çok daha küçük olmasını ilginç buluyorum. Sağ alttaki grafik bir aykırı değerin olduğunu ancak bunun dışında değerlerin sıkı bir şekilde kümelendiğini gösteriyor.

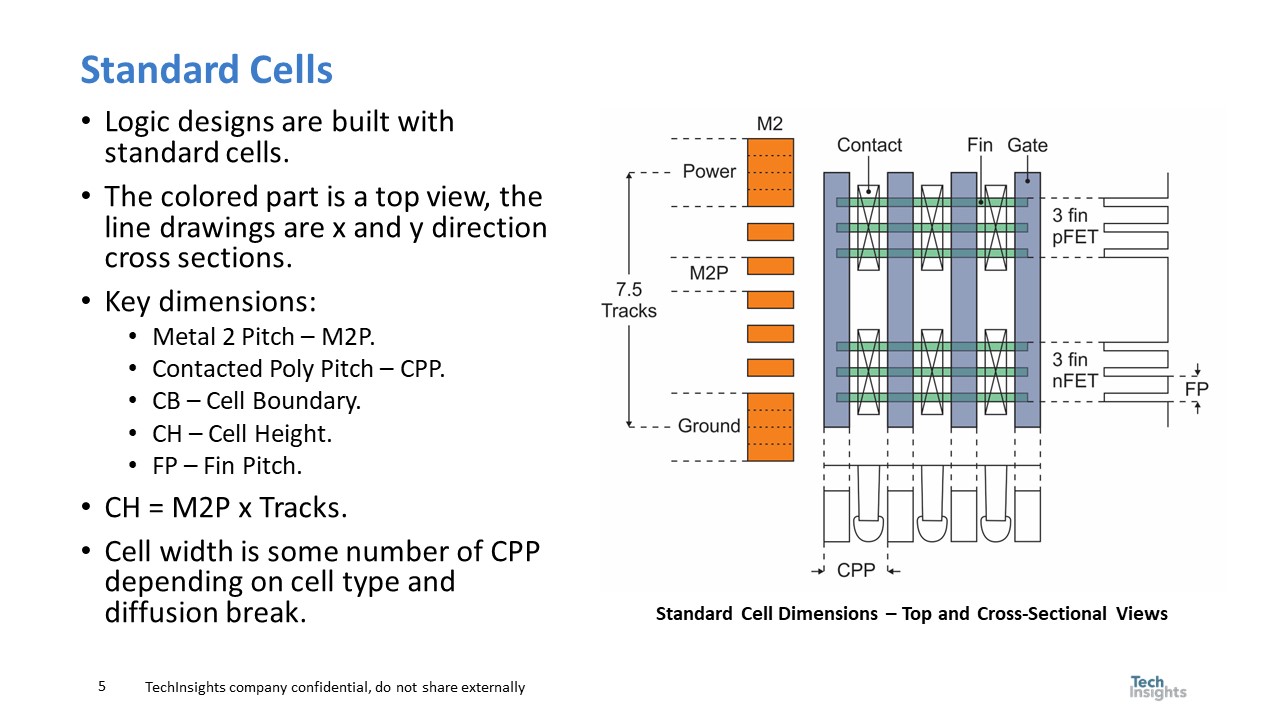

Tek mantık kalıp alanının neredeyse yarısını oluşturur, tasarımın mantık kısmıyla başlamak mantıklıdır. Mantık tasarımları standart hücrelerle yapılmıştır ve Şekil 2, standart bir hücrenin plan görünüşüdür.

Standart bir hücrenin yüksekliği tipik olarak Metal 2 Aralığı (M2P) ile ray sayısı çarpımı olarak tanımlanır, ancak şeklin sağ tarafına bakıldığında, aynı zamanda hücre yüksekliğine de uyması gereken cihaz yapısının bir kesit görünümü vardır. ve cihaz fiziği tarafından sınırlandırılmıştır. Aynı şey Temaslı Çoklu Aralığa (CPP) bağlı olan hücre genişliği için de geçerlidir ve şeklin alt kısmına bakıldığında, cihaz yapısının bir kez daha fizik tarafından kısıtlanan bir kesit görünümü vardır.

Şekil 3, hücre genişliği ve hücre yüksekliği ölçeklendirmesinin pratik sınırlarını belirlemek için yapılan bir analizin sonucunu sunar. Ölçeklendirme kısıtlamalarını detaylandıran bir sunumum var ve bu sunumda şekil 2 ile şekil 3 arasında onlarca slayt var ancak sınırlı bir süre nedeniyle yalnızca sonucu gösterebildim.

Hücre genişliği ölçeklendirmesi CPP'ye bağlıdır ve şeklin sol tarafı, CPP'nin Kapı Uzunluğu (Lg), Temas Genişliği (Wc) ve iki Temas-Kapı Ara Parçası Kalınlığından (Tsp) nasıl oluştuğunu gösterir. Lg, sızıntı nedeniyle kısıtlanmıştır ve kabul edilebilir sızıntıya sahip minimum Lg, cihaz tipine bağlıdır. Sınırlandırılmamış bir kalınlığa sahip bir kanalın yüzeyini kontrol eden tek bir kapıya sahip düzlemsel cihazlar yaklaşık 30 nm ile sınırlıdır. FinFET'ler ve yatay Nanosheets (HNS) kanal kalınlığını (~5nm) kısıtlar ve sırasıyla 3 ve 4 kapıya sahiptir. Son olarak, 2D malzemeler <1 nm kanal kalınlığına, silikon olmayan malzemelere sahiptir ve ~5 nm'ye kadar Lg üretebilir. Hem Wc hem de Tsp, parazitler nedeniyle sınırlı ölçeklendirme yeteneğine sahiptir. Sonuç olarak, 2D bir cihaz muhtemelen ~30 nm olan günümüzün CPP'lerine kıyasla ~50 nm'lik bir CPP üretebilir.

Hücre yüksekliği ölçeklendirmesi şeklin sağ tarafında gösterilmektedir. HNS, birden fazla kanatçık yerine tek nano tabaka yığınları sunar. Daha sonra CFET'li istiflenmiş cihazlara geçiş, yatay np aralığını ortadan kaldırır ve nFet ile pFET'i istifler. Şu anda 150nm ila 200nm olan hücre yükseklikleri ~50nm'ye düşürülebilir.

CPP ve Hücre Yüksekliği ölçeklemenin kombinasyonu, milimetre kare başına ~1,500 milyon transistör (MTx/mm) değerinde transistör yoğunlukları üretebilir2) günümüzün <300MTx/mm'sine kıyasla2. 2D malzemelerin muhtemelen 2030 ortası ve sonu teknolojisi olacağı, dolayısıyla 1,500 MTx/mm olacağı unutulmamalıdır.2 burada tartışılan zamanlamanın dışındadır.

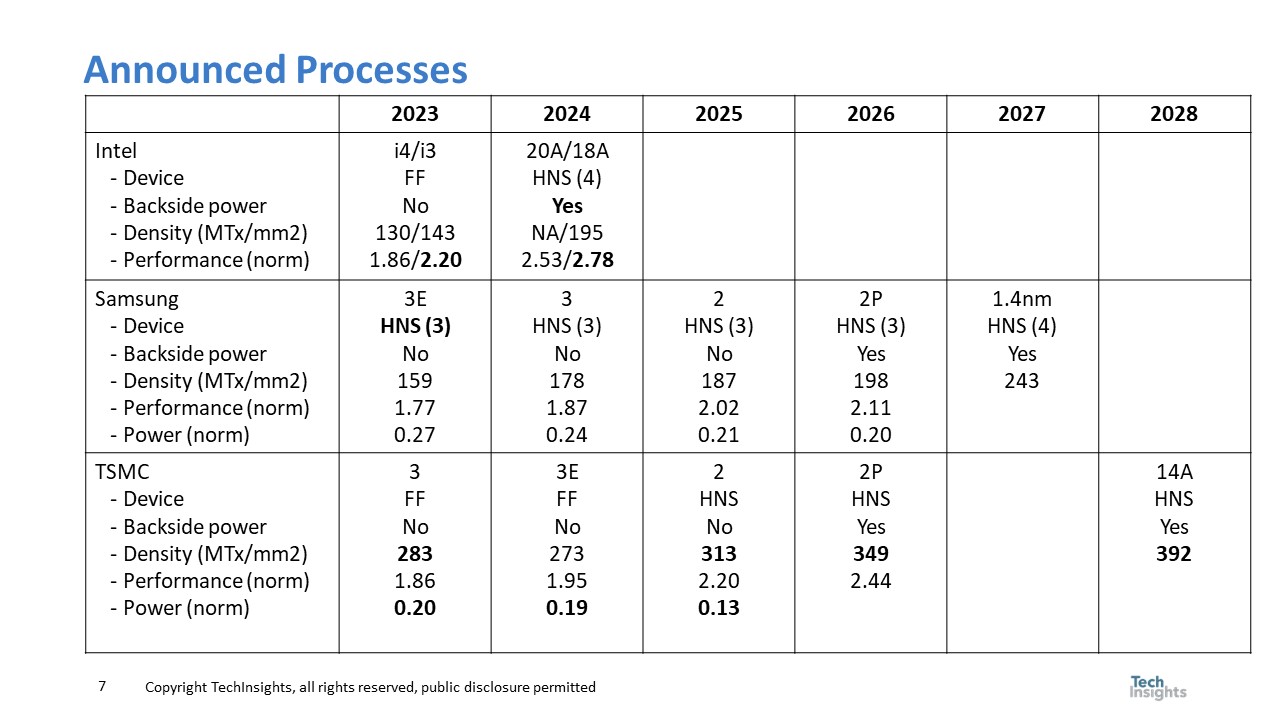

Şekil 4'te Intel, Samsung ve TSMC tarafından duyurulan süreçlerin bir özeti sunulmaktadır.

Her firma ve yıl için cihaz tipi, arka güç kullanılıp kullanılmadığı, varsa yoğunluk, güç ve performans görüntülenir. Güç ve performans göreceli ölçümlerdir ve güç Intel'de mevcut değildir.

Şekil 4'te önde gelen performans ve teknoloji yenilikleri kalın harflerle vurgulanmıştır. Samsung, HNS'yi 2023'te üretime sokan ilk şirket olurken Intel, HNS'yi 2024'e, TSMC'yi ise 2025'e kadar tanıtmayacak. Intel, arka taraf gücünü 2024'te üretime sokan ilk şirket olacak ve Samsung ve TSMC bunu 2026'ya kadar tanıtmayacak.

Analizim, Intel'in i3 ile performans lideri olduğu ve gösterilen dönem için bu durumu koruduğu sonucuna varıyor; TSMC güç liderliğine (Intel verileri mevcut değil) ve yoğunluk liderliğine sahip.

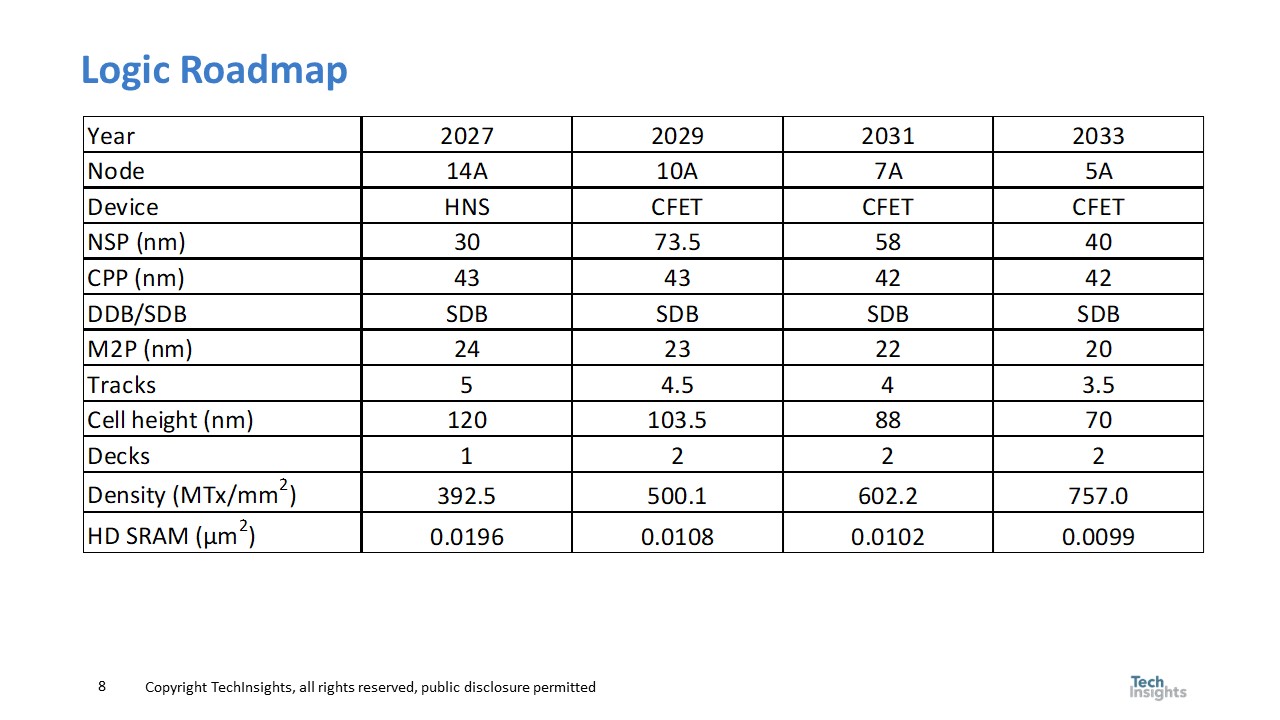

Şekil 5 mantıksal yol haritalarımızı sunmakta ve öngörülen SRAM hücre boyutlarını içermektedir (bununla ilgili daha sonra detaylı bilgi verilecektir).

Şekil 5'ten, CFET'lerin 2029 yılı civarında piyasaya sürülmesinin, mantık yoğunluğunda bir artış sağlamasını ve aynı zamanda SRAM hücre boyutlarını neredeyse yarı yarıya azaltmasını bekliyoruz (SRAM hücre boyutu ölçeklendirmesi neredeyse ön uçta durmuştur). Mantık yoğunluğunun ~757MTx/mm'ye ulaşmasını bekliyoruz2 2034 tarafından.

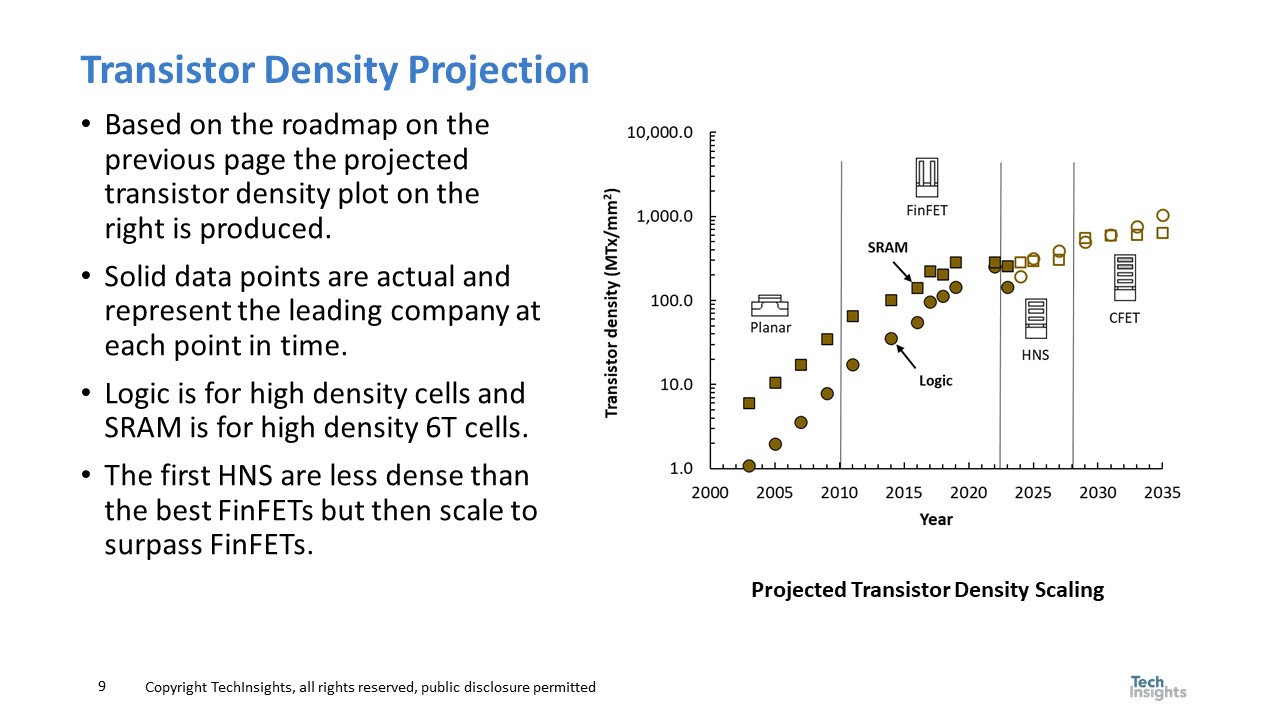

Hem mantıksal transistör yoğunluk projeksiyonları hem de SRAM transistör yoğunluk projeksiyonları şekil 6'da gösterilmektedir.

Hem mantık hem de SRAM transistör yoğunluğu ölçeklendirmesi yavaşlıyor ancak SRAM daha büyük ölçüde ve mantık artık SRAM ile benzer transistör yoğunluğuna sahip.

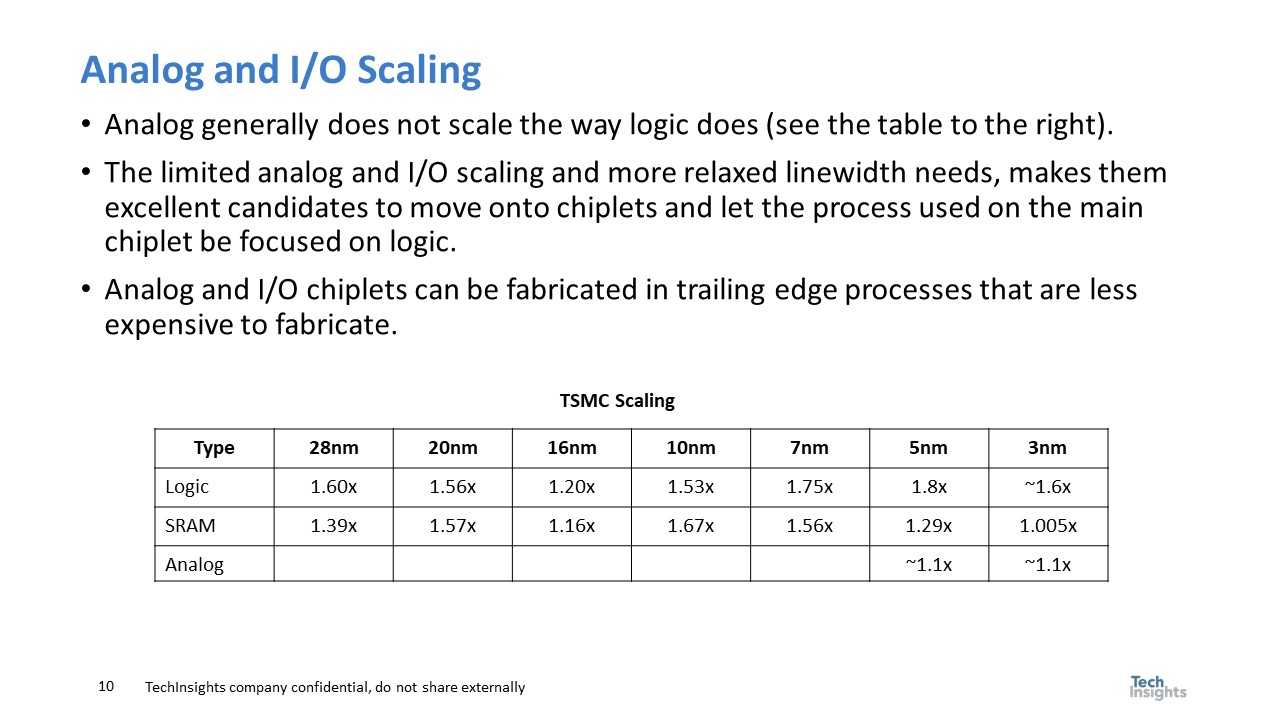

Slayt 7, Logic ve SRAM ile karşılaştırmalı olarak analog ölçeklendirmeye ilişkin TSMC verilerini özetlemektedir. Analog ve G/Ç ölçeklendirmenin her ikisi de mantıksal ölçeklendirmeden daha yavaştır.

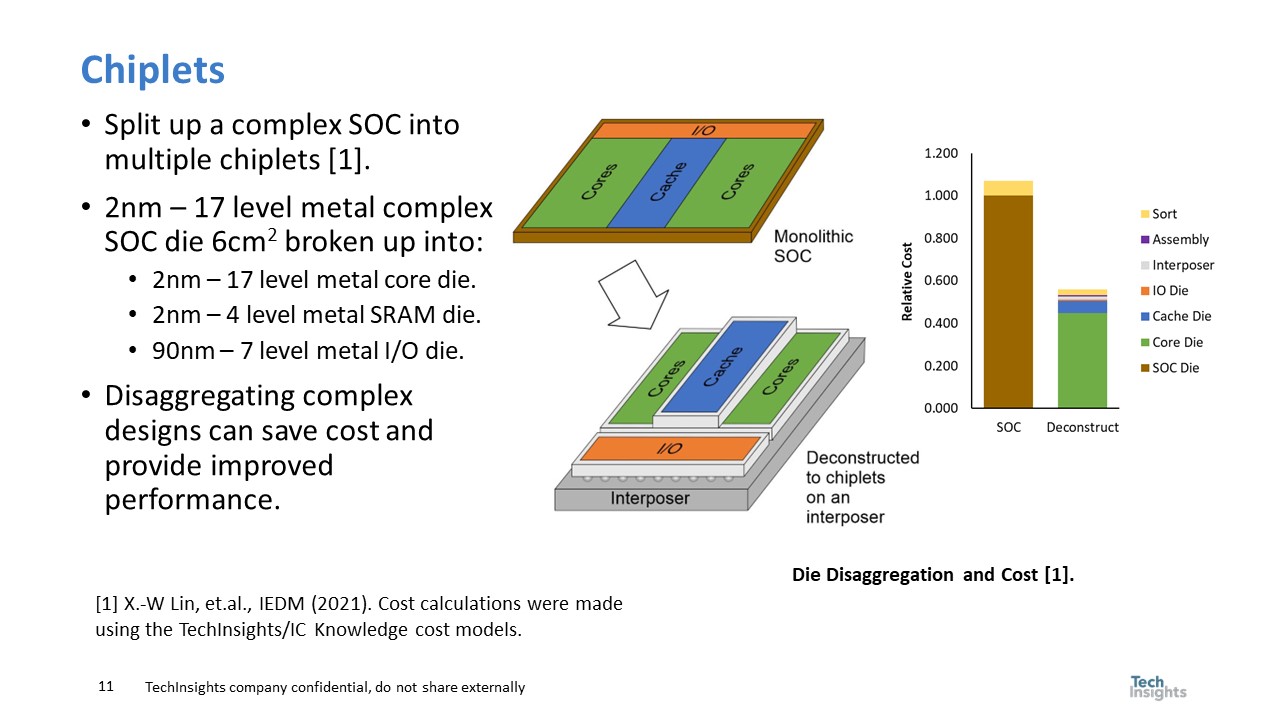

Daha yavaş SRAM ve analog ve G/Ç ölçeklendirmesine yönelik olası bir çözüm yongalardır. Chiplet'ler, SRAM ve I/O yapmak için daha ucuz ve daha optimize edilmiş süreçlerin kullanılmasını sağlayabilir.

Şekil 8'in sağ tarafındaki şekil, Synopsys ile birlikte yazdığım 2021 tarihli bir makaleden alınmıştır. Vardığımız sonuç, büyük bir SOC'yi yongalara ayırmanın, artan paketleme/montaj maliyetlerini hesaba kattıktan sonra bile maliyeti yarı yarıya azaltabileceğiydi.

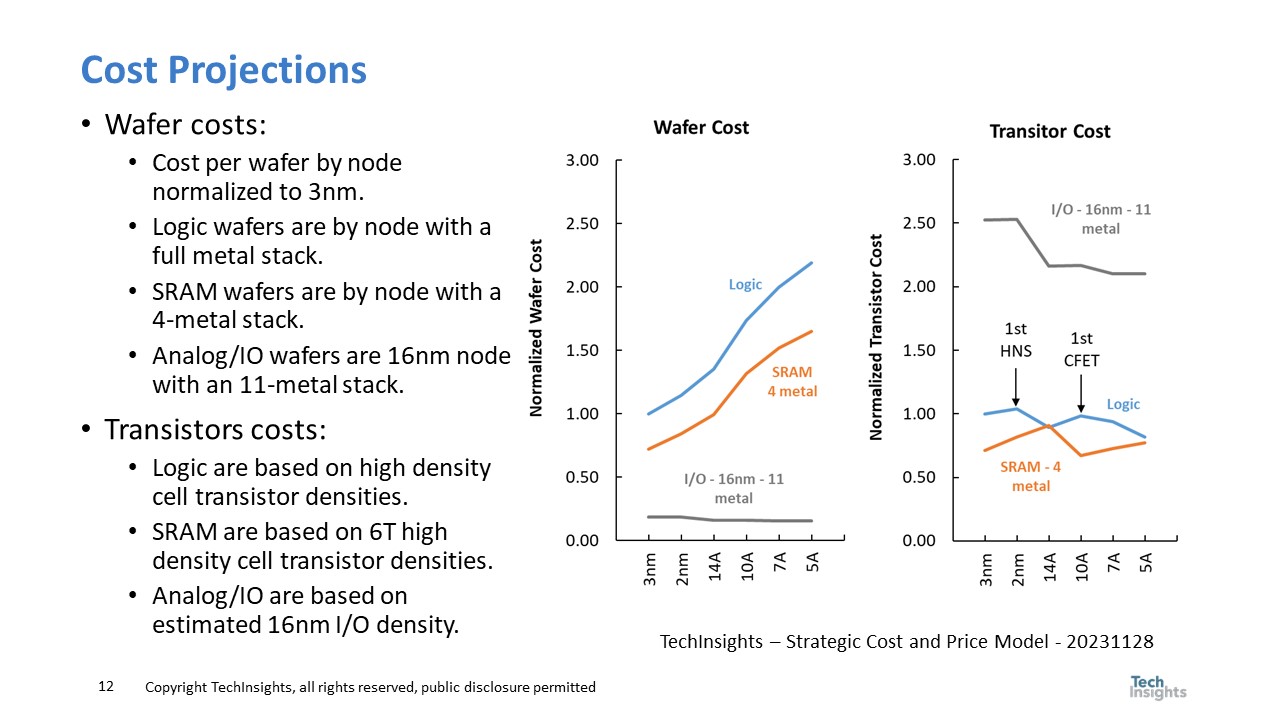

Şekil 9'da mantık, SRAM ve I/O için normalleştirilmiş devre plakası ve transistör maliyetleri gösterilmektedir (lütfen rakamın orijinal sunumdan güncellendiğine dikkat edin).

Sağdaki şekilde normalleştirilmiş gofret maliyeti gösterilmektedir. Mantıksal levha maliyeti, metal katman sayısı artan tam metal yığını içindir. SRAM plakaları aynı düğümlerdir ancak SRAM'ın daha düzenli düzeni nedeniyle 4 metal katmanla sınırlıdır. G/Ç levha maliyeti 16nm – 11 metal prosesine dayanmaktadır. Yeterli I/O performansını sağlamak amacıyla minimum maliyetli FinFET düğümü elde etmek için 16nm'yi seçtim.

Sağdaki rakam transistör maliyetine dönüştürülen wafer maliyetidir. İlginç bir şekilde, G/Ç transistörü o kadar büyüktür ki, düşük maliyetli 16nm'lik bir levhada bile en yüksek maliyete sahiptirler (G/Ç transistörü boyutu, gerçek G/Ç transistörlerinin TechInsights ölçümlerine dayanmaktadır). Mantıksal transistör maliyetleri, daralmanın mütevazı olduğu ilk TSMC HNS sayfa düğümünde 2nm'de artıyor. 14A'daki daralmanın ikinci nesil HNS düğümü olarak daha büyük olmasını bekliyoruz (bu, TSMC'nin ilk FinFET düğümünde yaptığına benzer). Bir kez daha, ilk CFET düğümünün maliyeti aynı zamanda bir düğüm için transistör maliyetini de artırmaktadır. SRAM transistör maliyeti, tek seferlik CFET daralması dışında sınırlı daralma nedeniyle artış eğilimi gösterir. Bu analizin özü, Chiplet'lerin tek seferlik bir fayda sağlayabilmesine rağmen, transistör maliyetindeki azalmanın mütevazı olacağıdır.

Sürdürülebilirliğe geçersek, şekil 10 karbon ayak izini oluşturan farklı “kapsamları” açıklamaktadır.

Kapsam 1, proses kimyasalları ve yanmadan kaynaklanan doğrudan saha emisyonlarıdır (elektrik aynı zamanda sahada üretiliyorsa kapsam 1 olabilir), Kapsam 2 ise satın alınan elektriğin karbon ayak izinden kaynaklanmaktadır. Kapsam 3 bu analize dahil edilmemiştir ancak satın alınan malzemelerin karbon ayak izinden, üretilen ürünün kullanımından ve şirket çalışanlarının kullandığı araçlar gibi şeylerden kaynaklanmaktadır.

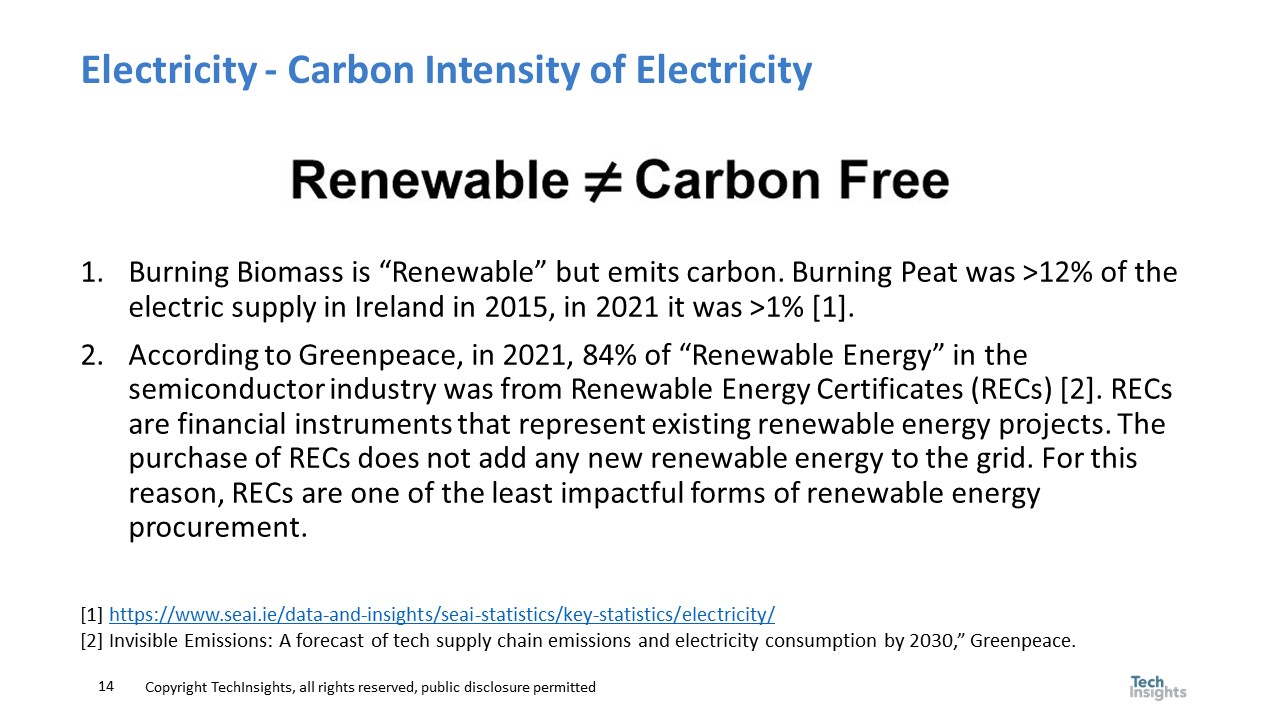

Yarı iletken endüstrisindeki pek çok şirket, elektriğin tamamı yenilenebilir olduğu için elektrikten dolayı karbon salımı yapmadıklarını iddia ediyor. Şekil 11'de yenilenebilir enerji ile karbonsuz enerji karşılaştırılıyor.

Temel sorun, Greenpeace tarafından 84 yılında yarı iletken endüstrisindeki yenilenebilir enerjinin %2021'ünün, bir şirketin başka birisinin yapmış olduğu indirimleri talep etme haklarını satın aldığı yenilenebilir enerji sertifikaları olduğunun tespit edilmesidir. Bu, düşük karbonlu elektrik kaynakları kurmak veya başkalarına düşük karbonlu elektrik sağlamaları için ödeme yapmakla aynı şey değildir ve aslında küresel karbon ayak izini düşürmez.

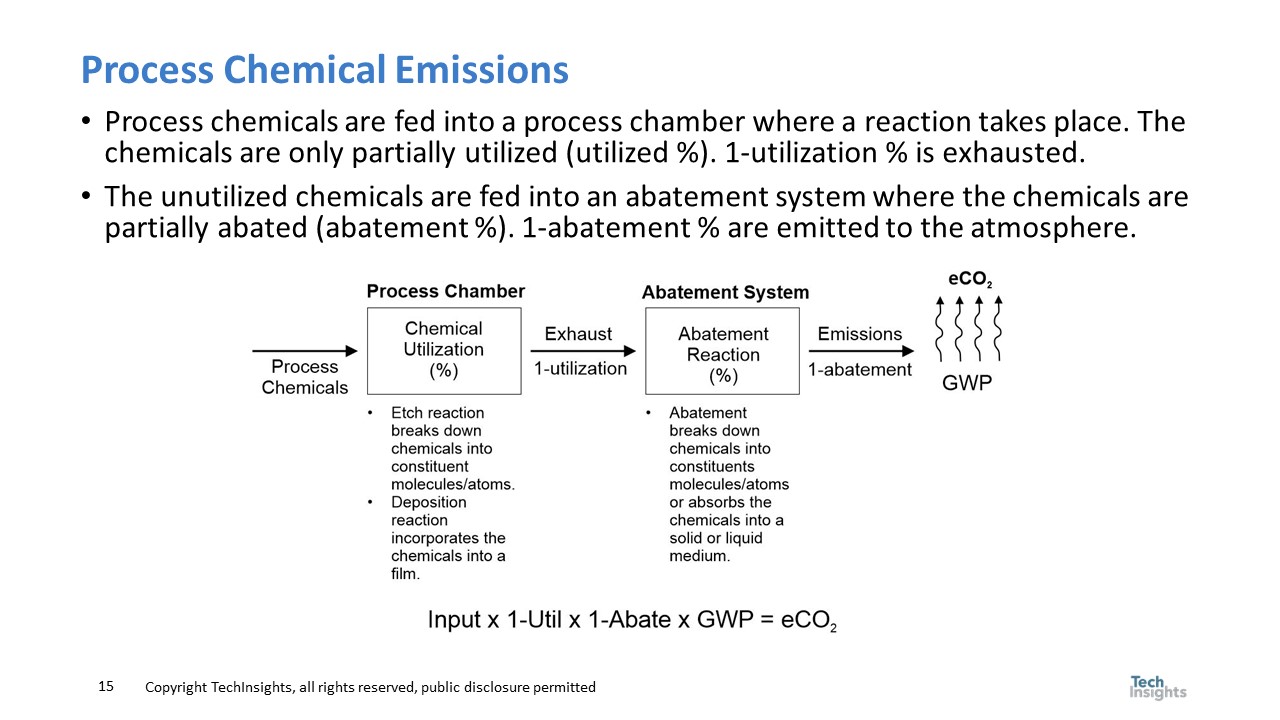

Şekil 12 proses kimyasal emisyonlarının nasıl gerçekleştiğini ve karakterize edildiğini göstermektedir.

Proses kimyasalları, kimyasalların bir yüzdesinin, kimyasalları parçalayan veya bunları biriktirilmiş bir filme dahil eden bir aşındırma veya biriktirme reaksiyonunda kullanıldığı bir işlem odasına girer. 1-kullanım, aletin egzozundan çıkan kimyasal miktarıdır. Aletin egzozu daha sonra bir azaltma odasına gidebilir ve kimyasalların bir yüzdesini daha da parçalayabilir ve azaltmadan dolayı atmosfere yapılan emisyonlar 1-azaltımdır. Son olarak emisyonun karbon eşdeğerliğini hesaplamak için Küresel Isınma Potansiyeli (GWP) uygulanır. GWP, kimyasalın atmosferde ne kadar süre kaldığını ve karbondioksite kıyasla kimyasalın ne kadar ısıyı geri yansıttığını dikkate alır. Karbon dioksitin GWP'si 1'dir, SF gibi yarı iletken proses kimyasalları6 ve NF3 sırasıyla 24,300 ve 17,400 GWP değerlerine sahiptir (IPCC AR6'ya göre).

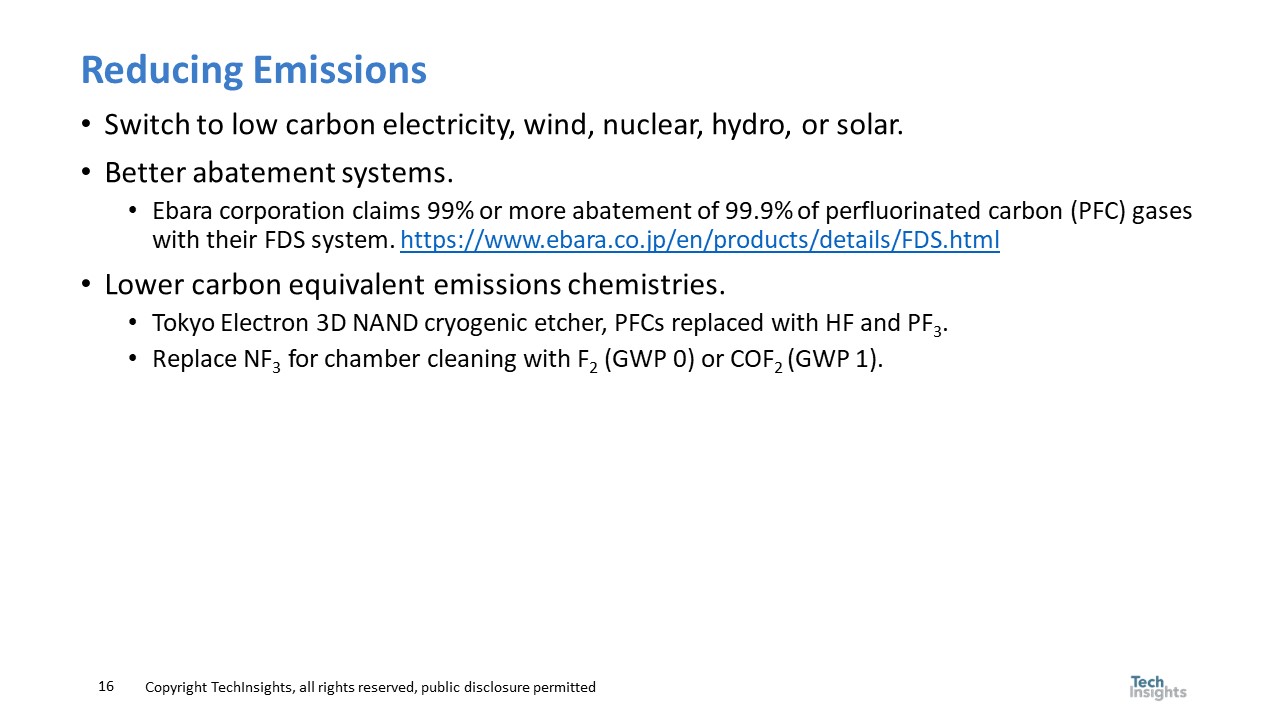

Şekil 13'te emisyonların azaltılmasına yönelik bazı seçenekler sunulmaktadır.

Kömür gibi elektrik kaynakları 820 gram COXNUMX üretiyor2 kilowatt saat başına eşdeğer emisyonlar (gCO2e/KWh) bulunurken güneş, hidroelektrik, rüzgar ve nükleer enerji sırasıyla 48, 24, 12 ve 12 gCO2e/KWh üretir.

Daha verimli azaltma sistemleri, proses gazlarını daha etkili bir şekilde parçalayabilir. Fab azaltma sisteminin verimliliği, bildirilen bazı ABD tesisleri için %0'dan (azaltma yok) ~%90'a kadar değişmektedir. Dünya çapındaki 300 mm fabrika ortalamasının ~%70 olduğunu ve 200 mm ve daha küçük levha boyutundaki fabrikaların çoğunda herhangi bir azalma olmadığını tahmin ediyoruz. %99'a varan verimliliğe sahip sistemler mevcuttur.

Daha düşük emisyon kimyası da kullanılabilir. Tokyo Electron, 3D NAND için sıfır GWP'li gazları kullanan yeni bir aşındırma aracını duyurdu. SF gibi gazlar6 ve NF3 öncelikle F yerine temizlik amacıyla odalara Flor (F) iletmek için kullanılır2 (GWP 0) veya COF2 (GWP 1) esasen bu emisyon kaynağını ortadan kaldırabilir.

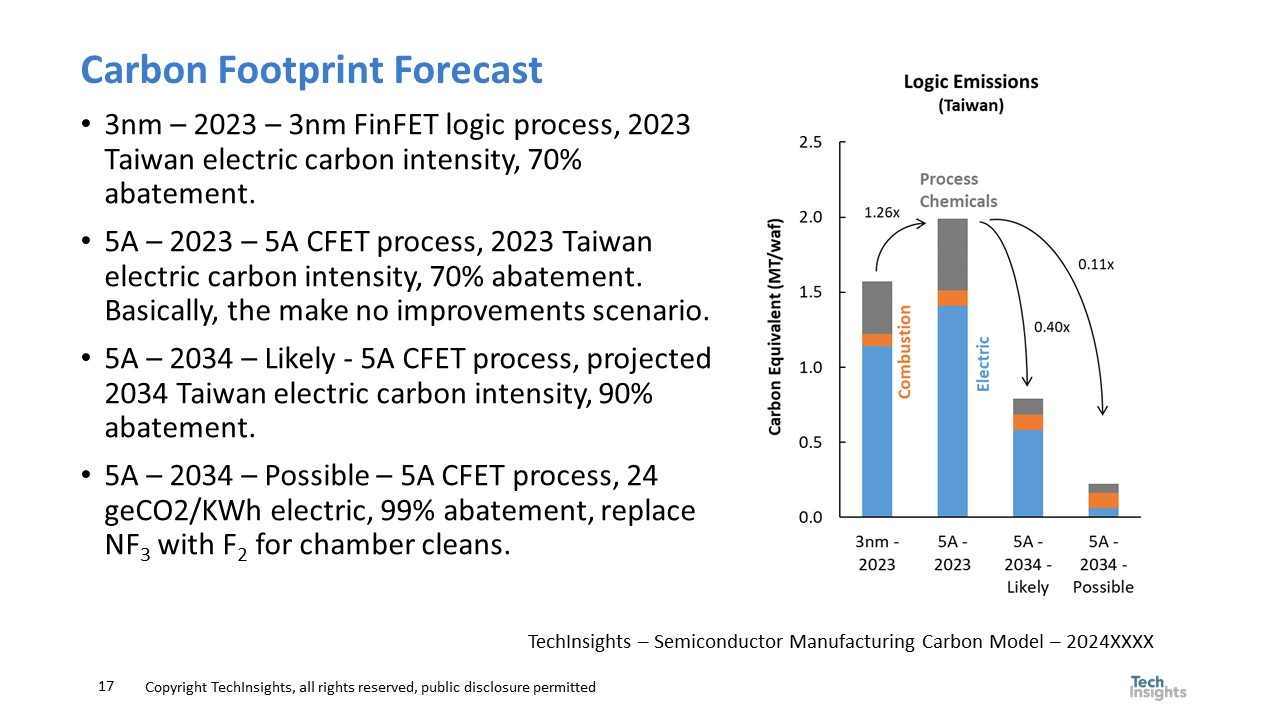

Şekil 14'te mantık için Karbon Ayak İzi Tahmini gösterilmektedir.

Şekilde soldaki ilk çubuk, Tayvan'ın elektrik karbon ayak izini ve %3 azalmayı varsayarak 2023'te Tayvan'da gerçekleştirilen 70 nm'lik bir süreci göstermektedir. İkinci çubuk bir 5A sürecidir ve aynı 2023 Tayvan elektrik karbon yoğunluğu ve %70 azaltım kullanıldığında ortaya çıkacak emisyondur. Süreç karmaşıklığındaki artış genel ayak izini 1.26 kat artıracaktır. 2034'ü sabırsızlıkla beklediğimizde Tayvan'ın elektriğinin önemli ölçüde karbonsuzlaşması bekleniyor, ayrıca %90 azaltım yaygın olmalı ve üçüncü çubuk bu koşul altında 5A sürecinin nasıl görüneceğini gösteriyor. Bu, emisyonların yarıdan fazla azaltılması anlamına gelse de, 2034 yılı için endüstri tarafından işletilen levha sayısındaki artış muhtemelen bu iyileşmeyi gölgede bırakacaktır. Sağdaki son çubuk, yeterli yatırımla mümkün olandır; düşük karbonlu elektriğe, %99 azaltım ve F kullanımına dayanmaktadır.2 oda temizliği için.

Şekil 15'te sonuçlarımız sunulmaktadır:

Transistör yoğunluğu ile levha ve kalıp maliyet tahminleri, ayrıntılı ekipman ve malzeme gereksinimlerinin yanı sıra maliyet ve fiyat tahminleri üreten bir sektör yol haritası olan TechInsights Stratejik Maliyet ve Fiyat Modeli kullanılarak oluşturuldu. Sera gazı emisyon tahminleri TechInsights Yarı İletken Üretim Karbon Modeli kullanılarak üretildi. Daha fazla bilgi için lütfen sales@techinsights.com ile iletişime geçin.

TechInsights'ın Tersine Mühendislik İş Birimindeki meslektaşlarıma teşekkür etmek isterim; onların dijital kat planı ve süreç raporları bu sunumun oluşturulmasında çok yardımcı oldu. Ayrıca TechInsights'tan Alexandra Noguera'ya bu çalışma için G/Ç transistör boyutlandırma verilerini çıkarması için teşekkür ederiz.

Ayrıca Oku:

IEDM 2023 – 300mm Wafer Fab Karbon Emisyonlarının Modellenmesi

Huawei Mate Pro 2'ta SMIC N+60

ASML Güncellemesi SEMICON Batı 2023

Bu gönderiyi şu yolla paylaş:

- SEO Destekli İçerik ve Halkla İlişkiler Dağıtımı. Bugün Gücünüzü Artırın.

- PlatoData.Network Dikey Üretken Yapay Zeka. Kendine güç ver. Buradan Erişin.

- PlatoAiStream. Web3 Zekası. Bilgi Genişletildi. Buradan Erişin.

- PlatoESG. karbon, temiz teknoloji, Enerji, Çevre, Güneş, Atık Yönetimi. Buradan Erişin.

- PlatoSağlık. Biyoteknoloji ve Klinik Araştırmalar Zekası. Buradan Erişin.

- Kaynak: https://semiwiki.com/semiconductor-manufacturers/342094-iss-2024-logic-2034-technology-economics-and-sustainability/