MOSFET geçit direnci, MOSFET'lerin ve CMOS devrelerinin aşağıdakiler gibi birçok özelliğini belirleyen çok önemli bir parametredir:

• Anahtarlama hızı

• RC gecikmesi

• Fmax – maksimum salınım frekansı

• Kapı (termal) gürültüsü

• MOS kapasitörler ve varaktörlerde seri direnç ve kalite faktörü

• Güç FET'lerinde anahtarlama hızı ve tekdüzelik

• Diğer birçok cihaz ve devre özelliği

Kapı direnci hakkında birçok akademik ve araştırma makalesi yazılmıştır. Bununla birlikte, IC tasarımcılarının ve yerleşim mühendislerinin pratik çalışmaları için birçok önemli şey tartışılmamış veya açıklanmamıştır, örneğin:

• Geçit direnci SPICE modelleri tarafından mı yoksa parazit ayıklama araçları tarafından mı ele alınıyor?

• Parazit çıkarma araçları geçit direncini nasıl ele alır?

• Düzenden veya çıkarılmış, düzen sonrası ağ listesinden geçit direnci nasıl değerlendirilebilir?

• Kapı direncinin "içsel" kapı direnci (gate poly) veya kapı metalleştirme yönlendirmesi ile sınırlı olup olmadığı nasıl belirlenir ve en kritik katmanlar ve çokgenler nelerdir?

• Kapı dağıtım etkisi (tek ve çift temaslı poli için 1/3 ve 1/12 çarpanları) IC tasarım akışında (PDK'da) yakalandı mı?

• Dökümhane PDK'larında dikey geçit direnci bileşeni yakalandı mı?

• Kapı direncini azaltmak için kapı daha geniş mi yoksa daha dar mı yapılmalı?

• Normal MOSFET'ler veya p-hücreleri ile RF için PDK'lerdeki kapı direncini işleme arasındaki fark nedir?

Bu makalenin amacı, bu soruların gizemini çözmek ve IC tasarım ve yerleşim mühendislerine tasarımlarındaki kapı direncini daha iyi anlamaları için bazı bilgiler sağlamaktır.

Kapı direnci tanımı ve ölçümü

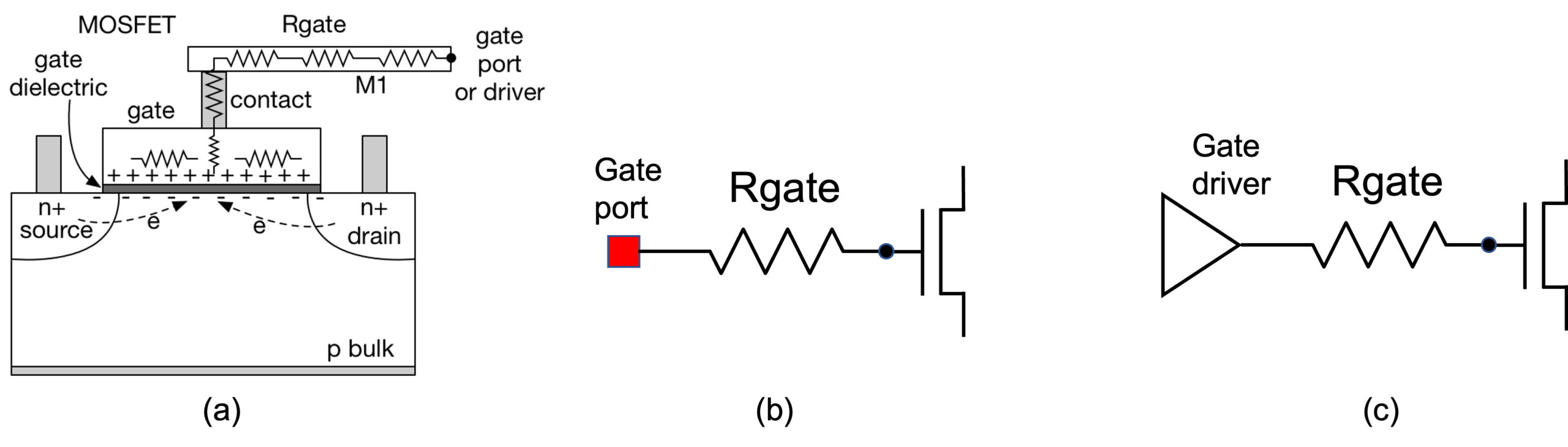

Geçit direnci, sürüş noktasından (kapı portu veya kapı sürücüsü) MOSFET geçit örneği pin(ler)ine “etkili” bir dirençtir – bkz. Şekil 1. (örnek pimi, SPICE modelinin bir terminali ile dirençli ağ ve ağ arasındaki bağlantı noktasıdır).

Bununla birlikte, Şekil 1'deki şemanın basitliği çok yanıltıcı olabilir. Geçit ağları boyut olarak çok büyük olabilir, birçok sürüş noktası, birçok (düzinelerce) katman (metal ve yol), milyonlarca çokgen ve milyonlarca kapı örneği pini (cihaz SPICE model kapı terminalleri için bağlantı noktaları) içerebilir – bkz. Şekil 2.

Geçit ağı, bir veya daha fazla sürüş noktası ve birçok varış noktası ile geniş bir dağıtılmış sistem oluşturur.

Çoğu zaman, geçit ağı, geçit voltajını bir FET'e dağıtan devasa, düzenli bir saat ağı gibi görünür ve davranır.

Böylesine büyük ve karmaşık bir sistem için eşdeğer, etkili bir kapı direnci türetmek basit ve anlaşılır bir iş değildir. SPICE devre simülasyonu, kapı direnci değerini açıkça bildirmez.

Geçit direncinin değerini bilmek, özelliklerin spesifikasyon dahilinde olup olmadığını görmek için anahtarlama hızını, gecikmeyi, gürültüyü, Fmax'ı ve diğer karakteristikleri tahmin etmek için çok faydalıdır. Ayrıca, katmana göre ve yerleşim poligonlarına göre kapı direncine katkıları bilmek, yerleşim optimizasyonu çabalarına rehberlik etmek için çok yararlıdır.

Parazit çıkarma araçlarıyla kapı direnci yönetimi

IC tasarım akışındaki kapı direncini anlamak için, parazit ayıklama araçlarının onu nasıl işlediğini ve modellediğini bilmek önemlidir.

Tüm endüstri standardı parazit ayıklama araçları, kapı direncini ve bunun çıkarılmasını benzer şekilde ele alır. Yerleşimde, MOS geçit yapısı, malzeme karmaşık bir geçit metal yığından oluşturulabilmesine ve karmaşık bir 2B yapıya sahip olabilmesine rağmen, geleneksel olarak "poli" olarak adlandırılan bir 3B maske ile temsil edilir.

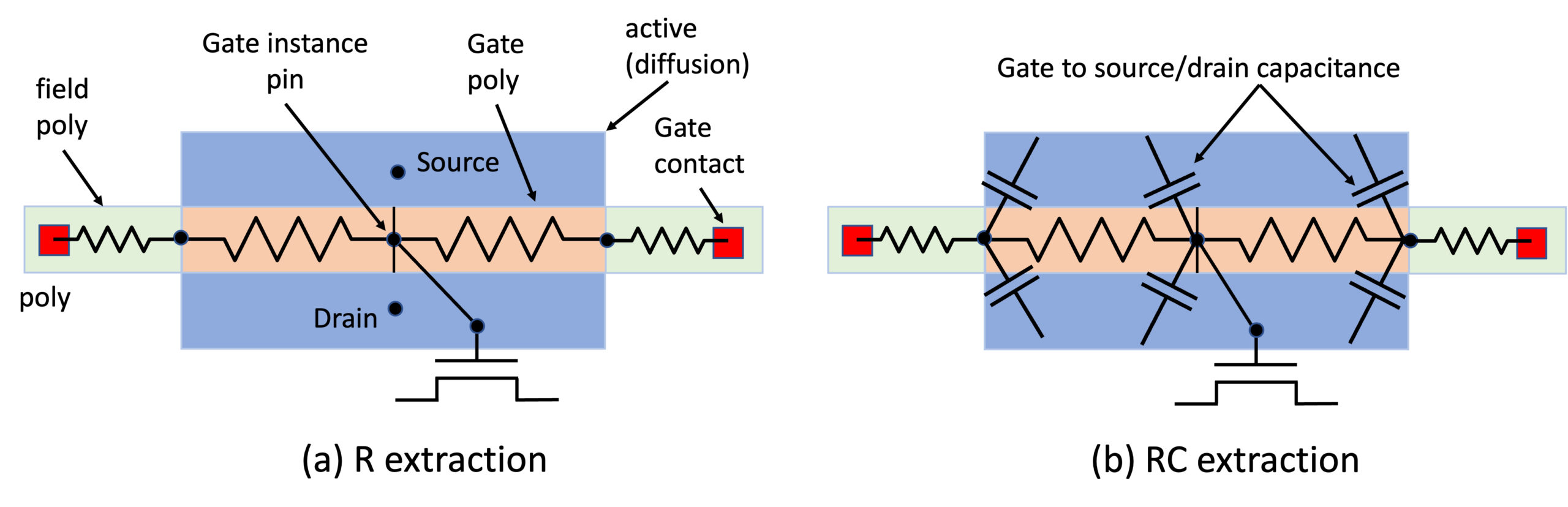

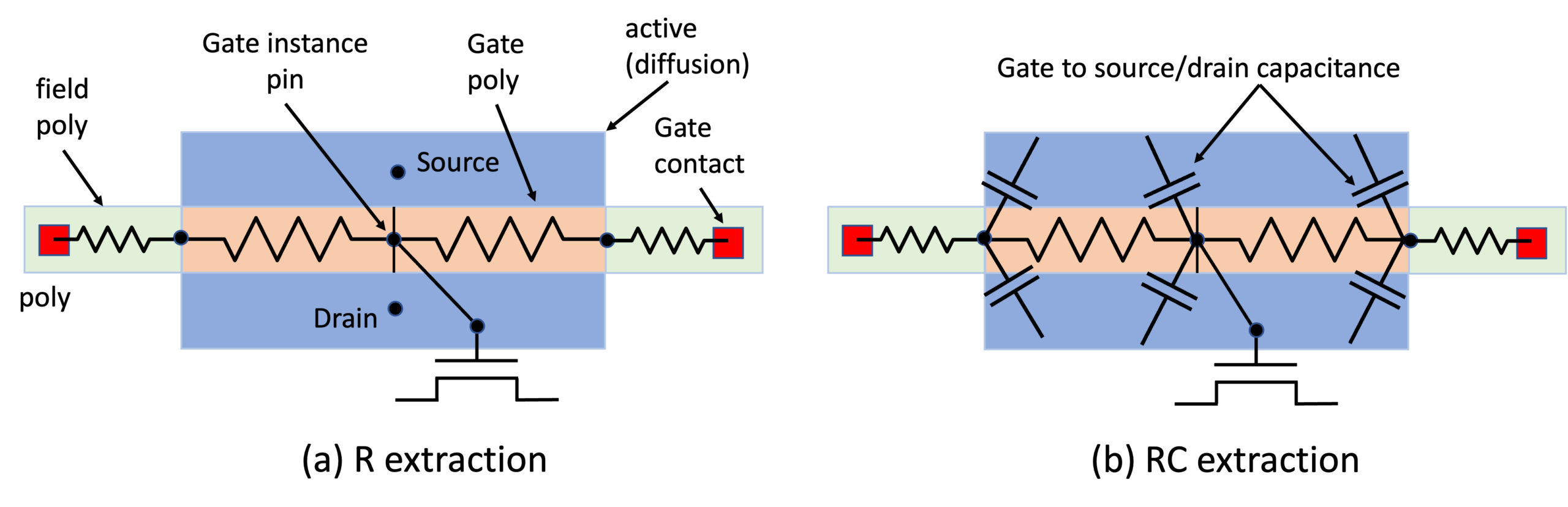

Şekil 3'te gösterildiği gibi, poli çizgisini aktif (difüzyon) katmanla kesiştiği noktada "gate poly" (poli aşırı aktif) ve "field poly" (poli dış aktif) olarak ayırarak kırarlar.

Gate poly de merkez noktasında kırılmıştır. MOSFET'in (SPICE modeli) kapı örneği pimi, kapı polinin merkez noktasına bağlanır. Gate poly, kırılma noktalarını birbirine bağlayan iki parazitik dirençle tanımlanır. PDK'da iki pozitif ve bir negatif dirençli daha doğru bir geçit poli modeli etkinleştirilebilir, ancak bazı dökümhaneler bunu kullanmamayı tercih eder (Gate Delta Modeli ile ilgili bir sonraki bölüme bakın).

Alan polisini temsil eden parazitik dirençler, geçit kontaklarına veya MEOL (Hat Ortası) katmanlarına ve ayrıca üst metal katmanlara bağlanır.

Geçit poli ve kaynak / drenaj difüzyonu ve kontakları arasındaki MOSFET dışsal parazit kapasitansı, parazit ayıklama araçları tarafından hesaplanır ve dirençli ağların düğümlerine atanır. Farklı çıkarma araçları bunu farklı şekilde yapar - bazı araçlar bu parazitik kapasitansları geçit polinin merkez noktasına bağlarken, diğer bazı araçlar bunları geçit poli dirençlerinin uç noktalarına bağlar. Geçit direnci ağına parazit kapasitans bağlantısının ayrıntıları, özellikle kapı parazit direncinin çok büyük olduğu gelişmiş düğümlerde (16nm ve daha düşük) geçici ve AC yanıtı üzerinde büyük, önemli bir etkiye sahip olabilir.

Bu ayrıntılar DSPF dosyasında görülebilir, ancak genellikle açık literatürde veya dökümhane PDK belgelerinde tartışılmaz. Metin DSPF dosyalarının görsel olarak incelenmesi sıkıcıdır ve biraz uzmanlık gerektirir. Özelleştirilmiş EDA araçları (örn. ParagonX [3]), mizanpaj sonrası ağ listeleri (DSPF, SPEF) için RC ağlarının bağlantısını görselleştirmek, bunları araştırmak (R ve C değerlerini görün ve inceleyin), elektriksel analiz gerçekleştirmek ve başka yararlı şeyler yapmak için kullanılabilir. .

Delta kapısı modeli

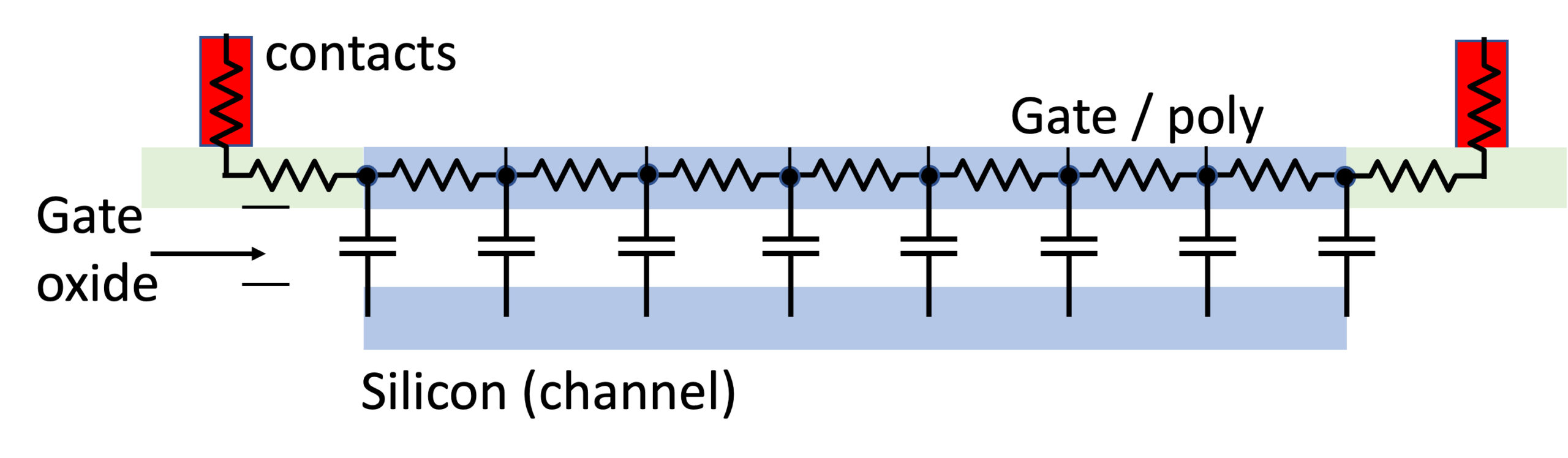

MOSFET kapısı, Şekil 4'te gösterilen, kapı genişliği boyunca büyük bir dağıtılmış RC ağı oluşturur.

Bu dağıtılmış ağ, basit toplu tek R ve tek C devresinden farklı bir AC ve geçici yanıta sahiptir. [2-3]'te, böyle bir RC ağının, bir R ve bir C elemanı olan bir ağ ile yaklaşık olarak aynı şekilde davrandığı gösterilmiştir; burada C, toplam kapasitanstır ve tek taraf için R=1/3 * W/L *rsh bağlı poli ve çift taraflı bağlı poli için R=1/12 * W/L * rsh. Bu katsayılar - 1/3 ve 1/12 - çok sayıda R ve C elemanını iki (veya üç) direnç ve bir kapasitöre indirgeyerek kapı için etkili bir şekilde doğru bir indirgenmiş sıra modeli sağlar.

Bu katsayıları standart bir RC ağ listesinde (SPICE ağ listesi veya DSPF) etkinleştirmek için, bazı akıllı insanlar sözde bir Kapı Delta Modeli icat etti - burada bir geçit iki pozitif ve bir negatif dirençle tanımlanır - Şekil 5'e bakın.

Bazı SPICE simülatörlerinin negatif dirençlerle başa çıkma sorunları vardır, muhtemelen bu modelin geniş çapta benimsenmemesinin nedeni budur. Bazı dökümhaneler ve PDK'lar delta geçidi modelini desteklerken bazıları desteklemez.

DSPF dosyalarında negatif dirençler gördüklerinde birçok kişi şaşırır. Bu dirençler kapı örneği piminin yanındaysa, bunlar geçit delta devresinin bir parçasıdır.

Kapı uzunluğu boyunca (kaynaktan tahliye yönünde) dağıtılmış etkiler, kapı genişliğine kıyasla kapı uzunluğunun küçük bir değeri nedeniyle devre analizi düzeyinde genellikle göz ardı edilir.

Ara bağlantı parazitlerinin geçit direnci üzerindeki etkisi

"Eski" teknolojilerde, metal ara bağlantılar (metaller ve yollar) çok düşük bir dirence sahipti ve kapı direnci, kapı poli tarafından yönetiliyordu. Kapı direncinin analizi ve hesaplanması çok basitti.

En son teknolojilerde (örneğin 16nm ve altı), ara bağlantılar çok yüksek dirence sahiptir ve kapı direncine önemli bir oranda (%50 veya daha fazla) katkıda bulunabilir. Yerleşime bağlı olarak, kapı direnci herhangi bir katmandan – cihazdan (gate poly, field poly), MEOL veya BEOL'den önemli katkılar alabilir.

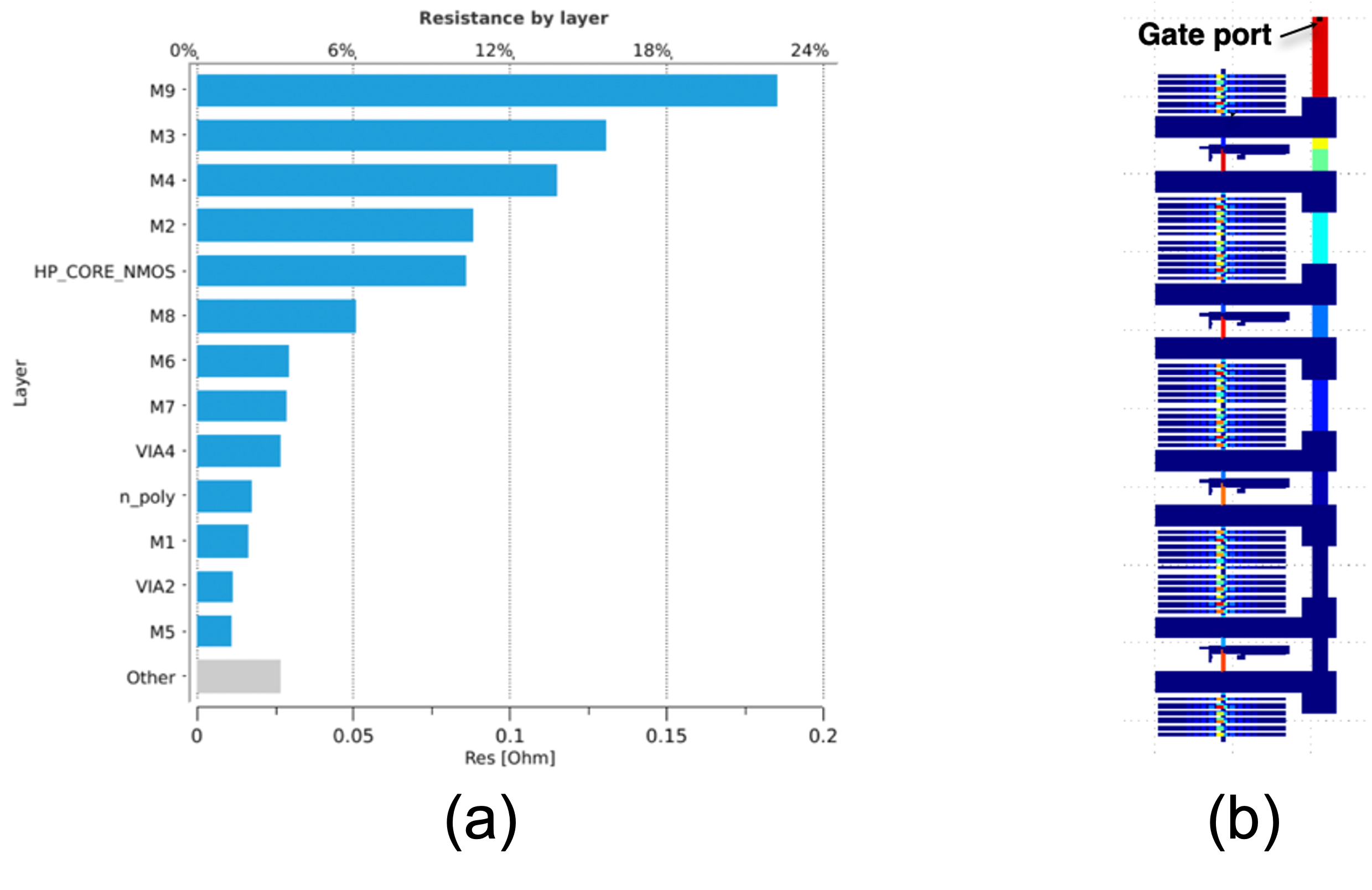

Şekil 6, ParagonX [3] kullanılarak kapı direnci simülasyonunun sonuçlarını göstermektedir. Katmana göre direnç katkılarına sahip Pareto grafiği, kapı direnci için en önemli katmanları belirlemeye yardımcı olur. Düzen poligonlarının kapı direncine yaptığı katkıların görselleştirilmesi, kapı direnci için tıkanıklık noktalarına, darboğazlara hemen işaret eder ve bu, yerleşim optimizasyon çabalarına rehberlik etmek için çok yararlıdır.

FinFET'lerde kapı direnci

Düzlemsel MOSFET'lerde kapı çok basit bir düzlemsel yapıya sahiptir ve kapıdaki akım akışı, kapı genişliği doğrultusunda tek boyutludur.

FinFET teknolojilerinde kapı çok uzun silikon kanatları sarar ve dolayısıyla çok karmaşık bir 3D yapıya sahiptir. Ayrıca, eşik voltajını ayarlamak için iş fonksiyonuna göre kapı malzemesi seçilir (FinFET'lerdeki eşik voltajı, kanal katkısıyla değil, kapı malzemeleriyle ayarlanır). Bu malzemeler çok yüksek dirence sahiptir, talep edilen poliden çok daha yüksektir (tipik levha direnci ~10 Ohm/sq'dir). Kapı, birden fazla katmandan oluşabilir - silikonlu arayüz katmanı ve bunun üzerinde bir veya daha fazla katman.

Bununla birlikte, tüm bu ayrıntılar IC tasarımcılarından ve düzen mühendislerinden soyutlanır ve "poli" ve "etkin" için olağan çokgenleri görürler - bu da tasarım işini çok daha kolaylaştırır.

SPICE modeli ve parazit ayıklama arasındaki el sıkışma

Genel olarak, hem SPICE modelleri hem de parazit ayıklama araçları geçit direncini hesaba katar. Düzeni "bildiği" için (SPICE'tan farklı olarak) parazit ayıklama, cihazların çevresindeki parazitik R ve C değerlerini hesaplamak için daha doğru bir yöntem olarak kabul edilir.

Parazitik direnci ve kapasitansın çift sayılmasını önlemek için (SPICE modelinde ve parazit ekstraksiyonunda), SPICE modellemesi ile parazit ekstraksiyonu arasında özel durum parametrelerine dayanan bir el sıkışma mekanizması vardır.

Normal cihaz ve RF Pcell kompakt modelleri

Normal MOSFET SPICE modelleri, kapı direncini yüksek frekanslar, yüksek anahtarlama hızları veya RF veya gürültü performansı için yeterince doğru tanımlamaz. Yüksek simülasyon doğruluğunu sağlamak için, dökümhaneler genellikle sabit boyutlu, bir kalkan (koruyucu halkalar ve metal kafesler) içeren ve ölçümlerden elde edilen yüksek doğruluklu modellerle tanımlanan RF P-hücrelerinin kullanılmasını önerir. Bununla birlikte, bu RF P hücreleri, standart MOSEFT'lerden çok daha geniş bir alana sahiptir ve birçok tasarımcı, alanı azaltmak için standart MOSFET'leri kullanmayı tercih eder.

Kapı direncinin dikey bileşeni

"Eski" teknolojilerde (16nm öncesi), kapı direncine yanal direnç hakimdi. Bununla birlikte, ileri teknolojilerde, kapı malzemesi katmanları arasındaki çoklu arayüzler, büyük bir dikey kapı direncine yol açar. Bu direnç, kapı poli alanı ile ters orantılıdır. Geçit örneği pinini kapı polinin merkez noktasına bağlayan ek bir direnç olarak modellenebilir – bkz. Şekil 7(a). Sonuç olarak, kapı daraldığında (daha az kanat sayısı), kapı direnci azalır, ancak çok küçük kapı genişliklerinde artar. Şekil 7(b)'de görüldüğü gibi karakteristik monoton olmayan bir davranış sergiler. "Daha dar geçidin daha düşük kapı direncine sahip olduğu" eski kural artık çalışmıyor. Tasarımcılar ve yerleşim mühendisleri, kapı direncini en aza indirmek için optimum (minimum olmayan) kapı genişliğini (kanat sayısı) seçmelidir.

![Figure7 (a) Dikey kapı direncini hesaba katan kapı modeli ve (b) kanat sayısına karşı ölçülen ve simüle edilmiş kapı direnci (ref. [2]).](https://zephyrnet.com/wp-content/uploads/2023/05/gate-resistance-in-ic-design-flow-6.jpg)

Teknolojiye, PDK'ya ve dökümhaneye bağlı olarak, dikey geçit direnci parazit ekstraksiyonuna dahil edilebilir veya edilmeyebilir. Bunu DSPF dosyasında kontrol etmek çok kolaydır – eğer kapı örneği pini doğrudan kapı polinin merkezine bağlıysa – dikey direnç dikkate alınmaz. Kapı poli merkezine pozitif bir dirençle bağlanırsa, bu dirençler dikey kapı direncini temsil eder.

Teknoloji trendleri

Teknoloji ölçeklendirmesiyle, hem geçit dirençleri hem de ara bağlantı dirençleri, bir veya iki büyüklük sırasına kadar önemli ölçüde artar. Sonuç olarak, eski düğümlerde kapı direnci için önemli olmayan yerleşim düzeni ayrıntıları, gelişmiş düğümlerde çok önemli hale gelir.

Diğer MOSFET geçidi benzeri yapılar

Bu makaledeki kapı direnci tartışması MOSFET'lere odaklanırken, aynı argümanlar ve yaklaşımlar, kapı veya kapı benzeri sistemler tarafından kontrol edilen diğer dağıtılmış sistemler için geçerlidir, örneğin:

• IGBT'ler (Yalıtılmış Kapılı Bipolar Transistörler)

• Ayırma kapasitörleri

• MOS kapasitörleri

• Varaktörler

• Derin hendek ve diğer MIM benzeri entegre kapasitörler

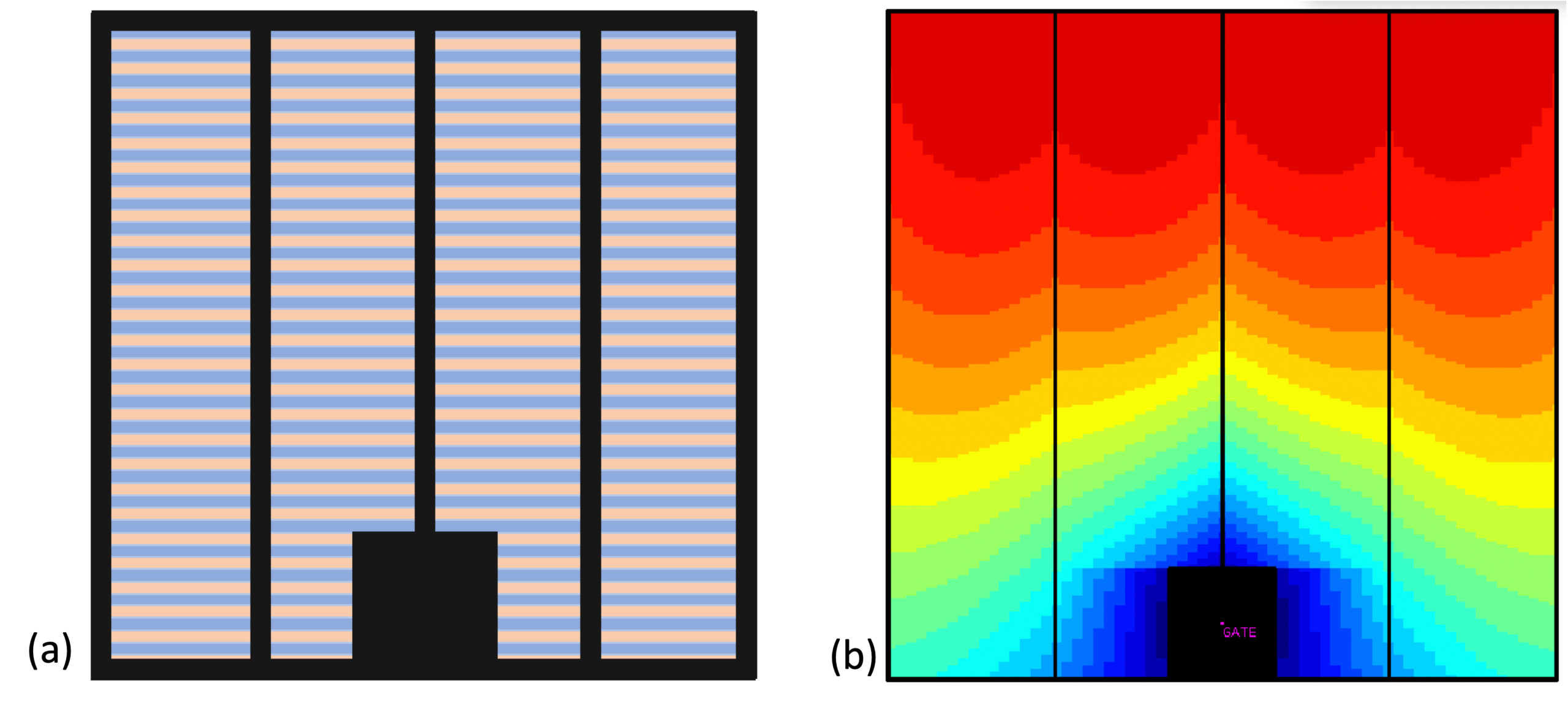

Şekil 8, ParagonX [3] kullanılarak simüle edilmiş, dikey bir MOSFET'in kapı yapısını ve cihaz alanı üzerindeki kapı gecikme dağılımını göstermektedir.

Referanslar

1. B. Razavi, et al., "Etkisi dağıtılmış geçit direncinin MOS cihazlarının performansı üzerindeki etkisi" IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, cilt. 41, s. 750-754, 11 1994.

2. AJSholten ve diğerleri, “Analog ve RF uygulamaları için FinFET kompakt modelleme”, IEDM'2010, s.190.

3. ParagonX Kullanım Kılavuzu, Diakopto Inc., 2023.

Ayrıca Oku:

Simetrik Yerleşimleriniz SPICE Simülasyonlarında Uyumsuzluklar gösteriyor. Neler oluyor?

Hızlı EM/IR Analizi, yeni bir EDA Kategorisi

Bu gönderiyi şu yolla paylaş:

- SEO Destekli İçerik ve Halkla İlişkiler Dağıtımı. Bugün Gücünüzü Artırın.

- PlatoAiStream. Web3 Veri Zekası. Bilgi Genişletildi. Buradan Erişin.

- Adryenn Ashley ile Geleceği Basmak. Buradan Erişin.

- Kaynak: https://semiwiki.com/eda/diakopto/328285-gate-resistance-in-ic-design-flow/