Birkaç yıldır görüşüyorum AMIQ EDA Kurucu ortak Cristian Amitroaie, birkaç ayda bir sektörün durumunu, tasarım ve doğrulamadaki temel eğilimleri ve bunların çip gelişimini kolaylaştırmaya ve hızlandırmaya nasıl yardımcı olabileceğini tartışmak üzere bir araya geliyor. En son sürümlerinde bahsedilen ilginç yeni bir özelliği fark ettim basın bülteni, bu yüzden Cristian'dan daha fazla bilgi istedim. Bu, canlı ve ilginç bir tartışmaya yol açtı.

Günümüzde çoğu tasarımcı ve doğrulama mühendisi kodlarını SystemVerilog'a yazıyor ancak istisnalar da var. Bazıları, SystemC'de veya SystemVerilog'dan biraz daha soyut olan diğer dillerde tasarım yapmak için üst düzey sentez (HLS) araçlarından yararlanır. Diğerleri kendi dillerinde yazıyor ve simülasyon, resmi doğrulama, sentez ve geliştirme sürecindeki diğer adımlar için kullanılan SystemVerilog dosyalarını oluşturmak için özel araçlar kullanıyor.

Cristian, zaman zaman mühendislerin öncelikle SystemVerilog olan ancak aynı zamanda Perl ve Python'un Jinja2 kütüphanesi gibi yerleşik dillerde veya özel dillerde "önişlemci" ifadeleri içeren kodlar yazdığı bir orta yol gördüklerini söyledi. Bu dosyaları işlemek ve akışın geri kalanı için saf SystemVerilog dosyalarını oluşturmak için komut dosyaları kullanırlar. Cristian'a ön işlemci kullanımının mühendislerin entegre geliştirme ortamını (IDE) kullanma şeklini nasıl değiştirdiğini sordum.

AMIQ EDA Tasarım ve Doğrulama Araçlarını kullananların (DVT) IDE ailesi, önişlemci koduyla dosyaları düzenlerken bile tüm favori özelliklerine erişebilmek istiyor. AMIQ EDA ekibi, tıpkı saf SystemVerilog'da olduğu gibi, bu tür dosyaları düzenlerken tam IDE yeteneklerini etkinleştirmek için akıllı buluşsal yöntemler geliştirdi. Bu özellikler arasında gezinme köprüleri, otomatik tamamlama, anında hata tespiti, hızlı düzeltmeler, yeniden düzenleme ve DVT IDE kullanıcılarının bağımlı olduğu tüm gelişmiş işlevler yer alır.

Bu benim için ilginçti. Karma dil dosyalarını "anlamaktan" bahsediyoruz, aslında herhangi bir derleyicinin kolayca anlayabileceği bir şey değil. Cristian, doğru anladığımdan ve bunun gerçekten olduğundan emin olmak için, bu yeteneğin geliştirilmesini koordine eden ekip lideri Zeljko Zurzic'i bu yeteneğin nasıl çalıştığını açıklamaya davet etti. Kullanıcıların yapması gereken tek şeyin, önişlemci ifadelerini içeren dosyalar (“p dosyası”) ile oluşturulan dosyalar (“g dosyası”) arasındaki eşleme hakkında DVT IDE'yi bilgilendirmek olduğunu söyledi.

Bu, çeşitli kullanım durumlarını destekleyen özel derleyici yönergeleri kullanılarak yapılır. Örneğin, DVT IDE derleyicisine "g dosyası başlık yorumundan karşılık gelen p dosyasını bulun" demenin bir yolu vardır. Bu yapıldıktan sonra kullanıcılar sanki özel bir şey yokmuş gibi p dosyalarını düzenlerler. Anında artımlı derleme, yazarken tüm SystemVerilog hatalarını işaretler, köprüler bunları kodun etrafında dolaştırır, otomatik tamamlama ve yeniden düzenleme gayet iyi çalışır, çeşitli diyagramlar talep edebilirler, vb.

Önişlemci kodunu içeren bölümler, kullanıcıların SystemVerilog koduna dönüştürüleceğini bilmeleri için belirgin bir şekilde işaretlenmiştir. İçinde DVT Eclipse IDE'si İnceleme Görünümü'nü kullanarak kodun nasıl oluşturulduğunu görebilirler; içinde VS Kodu için DVT IDE dönüşümleri "gözetleyebilirler". DVT IDE, önişlemci kodu her değiştirildiğinde ön işleme komut dosyasını otomatik olarak çalıştıracak şekilde yapılandırılabilir. Kullanıcılar istenirse ap dosyasını ilgili g dosyasıyla kolayca karşılaştırabilir.

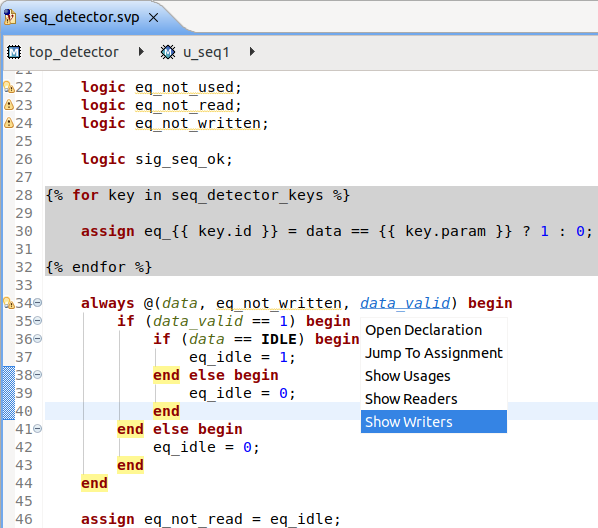

Zeljko, bu yeni yeteneği çalışırken gösteren üç ekran görüntüsü sağladı. Aşağıdaki ilki DVT Eclipse IDE'de Jinja2 ön işlemci ifadesini içeren bir dosyayı göstermektedir. SystemVerilog olmayan bu kodun varlığına rağmen kullanıcı, bir değişkenin nasıl yönlendirildiğini hızlı bir şekilde anlamak için güçlü "Yazarları Göster" özelliğinden yararlanabilir. Derleme hataları ve uyarılar ekranın en soldaki sütununda gösterilir.

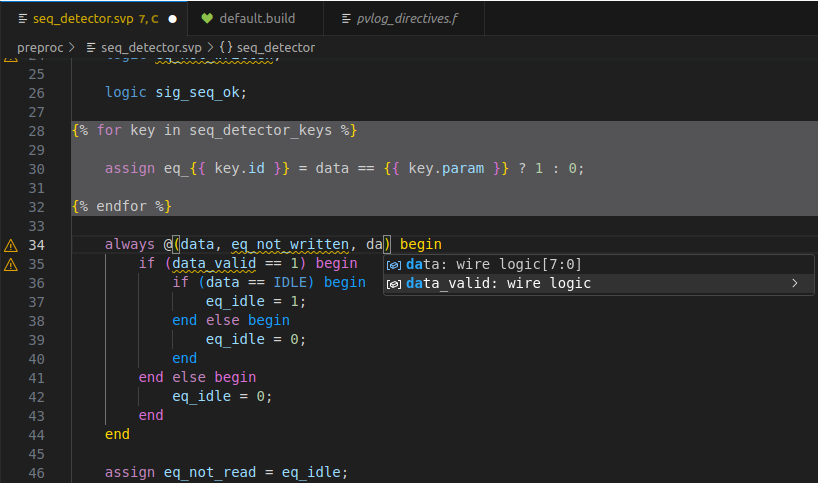

Aşağıdaki ekran görüntüsü aynı dosyayı VS Code için DVT IDE'de görüntüler, derleyici sorunlarını sol sütunda gösterir ve otomatik tamamlamanın kullanılmasını sağlar. Bu, en gelişmiş DVT işlevlerinin bile önişlemci ifadeleriyle kodda nasıl mevcut olduğunu gösterir.

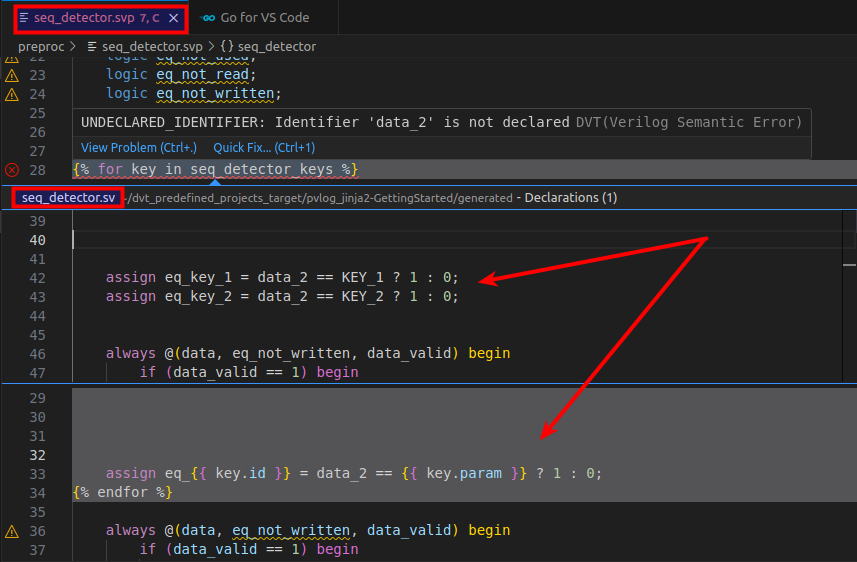

Zeljko, IDE'nin oluşturulan SystemVerilog kodunu kontrol ettiğini, bunun önemli olduğunu, çünkü önişlemci ifadesinde bir hata veya ön işleme komut dosyasında bir hata olabileceğini vurguladı. Aşağıdaki ekran görüntüsü tam da böyle bir örneği göstermektedir. Oluşturulan SystemVerilog kodu, kaynak dosyada tanımlanmayan bir değişken içeriyor. DVT IDE derleme hatasını, p dosyasını ve g dosyasında oluşturulan kodu görüntüler.

g dosyalarını görüntülemek hata ayıklamada yardımcı olabilir, ancak sonuç olarak kullanıcılar doğrudan p dosyalarıyla çalışır, bunları güçlü bir IDE kullanarak analiz eder ve düzenler. g dosyaları “salt okunur” olarak etiketlenir ve değiştirilmeleri durumunda kullanıcılar uyarılır. Bunu duyduğuma sevindim; Kod oluşturma sürecinde üzerine yazılacak herhangi bir dosyada manuel değişiklik yapmanın gerçekten kötü bir fikir olduğunu hepimiz biliyoruz.

Son olarak Cristian, bu yeni özelliğin asıl amacının, kullanıcıların sanki saf SystemVerilogmuş gibi önişlemci ifadeleriyle kodu düzenleyebilmeleri olduğunu vurguladı. Bunu mümkün kılmak, ön işlemci tabanlı akışlara güvenen birkaç önemli müşteri tarafından yürütülen önemli bir çabaydı. Açıklamaları ve zaman ayırdıkları için Zeljko ve Cristian'a teşekkür ettim.

Ön işlemci dosyalarının kullanımı veya AMIQ EDA çözümlerinin herhangi bir yönü hakkında daha fazla bilgi edinmek isterseniz, bunları Tasarım ve Doğrulama Konferansı ve Sergisinde Stand 107'de ziyaret edebilirsiniz (DVCon) Amerika Birleşik Devletleri 5 Mart ve 6 Mart'ta San Jose, Kaliforniya'da.

Ayrıca Oku:

AMIQ EDA'nın Kurucusu ve CEO'su Cristian Amitroaie ile 2024'e Bakış

Hatasız Test Bench Kodu Yazmak için Linting Kullanmak

AMIQ: Danışmanlık ve EDA'da 20. Yılını Kutluyor

Bu gönderiyi şu yolla paylaş:

- SEO Destekli İçerik ve Halkla İlişkiler Dağıtımı. Bugün Gücünüzü Artırın.

- PlatoData.Network Dikey Üretken Yapay Zeka. Kendine güç ver. Buradan Erişin.

- PlatoAiStream. Web3 Zekası. Bilgi Genişletildi. Buradan Erişin.

- PlatoESG. karbon, temiz teknoloji, Enerji, Çevre, Güneş, Atık Yönetimi. Buradan Erişin.

- PlatoSağlık. Biyoteknoloji ve Klinik Araştırmalar Zekası. Buradan Erişin.

- Kaynak: https://semiwiki.com/eda/amiq-eda/342053-handling-preprocessed-files-in-a-hardware-ide/