Onlarca yıldır kalıp boyutu, transistör sayısı, frekans ve karmaşıklık açısından SoC'lerin inanılmaz büyümesini izledim. Tüm sistem karmaşıklığını tek bir yekpare yongaya yerleştirmek yerine, artık çoklu yonga yaklaşımı kullanmak için zorlayıcı nedenler var, örneğin maksimum kalıp boyutu sınırına ulaşıldığında veya iki veya daha fazla küçük yonga kullanmanın daha uygun maliyetli olması gibi. çeşitli teknoloji düğümlerinde tasarlanmıştır. Çok kalıplı sistem yolunu seçmek, yeni yonga ara bağlantı zorluklarını beraberinde getirir:

- Güvenilir bağlantı

- Yüksek bant genişliği

- Düşük güç

- Düşük gecikme süresi

- standart desteği

Neyse ki endüstri için standartlar geliştirmek için ortak bir çaba var ve Evrensel Chiplet Ara Bağlantı Ekspres™ (UCIe™), bir bağlantı protokolünün yanı sıra kalıptan kalıba bir ara bağlantı yoluyla paket seviyesinde entegrasyonu etkinleştirerek çekiş kazandı, böylece birden fazla satıcı birlikte çalışabilirlik yoluyla bir ekosistem geliştirebilir. UCIe, üç yığın katmanını kapsar ve PHY katmanı, elektriksel arayüzü tanımlar.

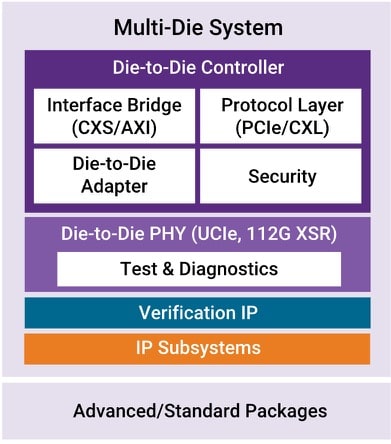

Özet oldu IP teslimi Arayüz, Temel, İşlemci, Güvenlik, Analog, Alt Sistemler gibi birçok alanda yıllardır. Ayrıca UCIe Konsorsiyumuna katılarak standardın belirlenmesine katkıda bulundular. Orada bir UCIe PHY IP'si Synopsys'ten, bir UCIe Denetleyici IP'si ve doğrulama IP'si.

Mart 2023'te Synopsys, UCIe PHY IP'lerinin video kaydına sahip olduğunu duyurdu. TSMC N3E işlem düğümü

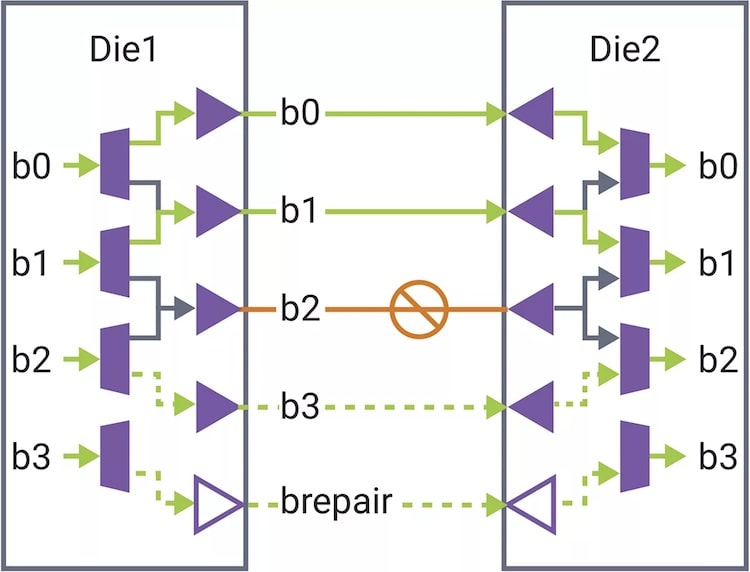

Güvenilir bağlantı için UCIe standardı, işlevsel bağlantıların onarılmasına izin veren yön başına 8 adede kadar yedek pine sahiptir.

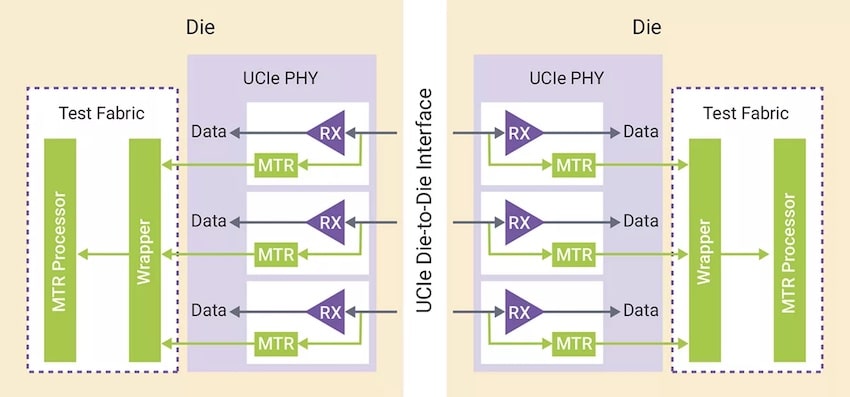

Kalıptan kalıba arayüz sinyallerindeki değişimler, Sinyal Bütünlüğü Monitörleri (SIM) tarafından izlenir, ardından İzleme, Test ve Onarım denetleyicisi, bağlantıların kestirimci bakımı için çoklu kalıp sisteminin sağlığını belirleyebilir. Synopsys'in sahip olduğu Silikon Yaşam Döngüsü Yönetimi çalışırken UCIe arayüzünü izlemek, yazılım veya donanım hatalarını tespit etmek için araçlar.

Synopsys PHY IP kullanan UCIe için bant genişliği, 5 Tbps/mm'ye varan verimliliktir. Denetleyici IP'si, akış protokollerinin yanı sıra PCI Express ve CXL protokollerini de destekleyerek güvenli, düşük gecikmeli veriler sağlar.

UCIe spesifikasyonunda hız kazanmak değerli mühendislik zamanı gerektirir, bu nedenle protokol doğrulama IP'sinin yeniden kullanılması ekibinize pazara sunma değerli zamanından tasarruf sağlayacaktır. Bir yazılım simülatöründe çalışan Doğrulama IP'si iyi bir başlangıç sağlar, ardından Sinopsis ZeBu ve prototipleme Özet HAPS Platform, çalışan yazılımın tamamında hata ayıklamak için daha fazla zaman tasarrufu sunar.

UCIe sinyallerinin kalıplar arasında yönlendirilmesi, Özet 3DIC Derleyici aracıdır ve 2.5D yongalar için çalışır.

Özet

Bugün sistem mühendisleri, uygulama için iki yaklaşım arasında, geleneksel tek çipli SoC veya çok kalıplı sistem arasında karar vermek zorunda. Synopsys gibi EDA satıcıları, uzun süredir tek çipli bir SoC için EDA görevlerini otomatikleştiriyorlar ve ayrıca çoklu kalıp sistemleri için yeni EDA araçları, doğrulama ve IP geliştirerek otomasyonlarını 2.5D alemine genişlettiler.

Çok kalıplı sistemlerin ara bağlantı zorlukları, yonga tabanlı sistemleri dikkate alan yeni projeler için riskleri azaltan UCIe gibi standartlaştırma çabalarıyla ele alınmıştır. Synopsys, çok kalıplı sistemlerin bu kadar geniş desteğine sahip birkaç EDA ve IP satıcısından biridir.

İlgili Bloglar

Bu gönderiyi şu yolla paylaş:

- SEO Destekli İçerik ve Halkla İlişkiler Dağıtımı. Bugün Gücünüzü Artırın.

- PlatoAiStream. Web3 Veri Zekası. Bilgi Genişletildi. Buradan Erişin.

- Adryenn Ashley ile Geleceği Basmak. Buradan Erişin.

- PREIPO® ile PRE-IPO Şirketlerinde Hisse Al ve Sat. Buradan Erişin.

- Kaynak: https://semiwiki.com/eda/synopsys/329299-chiplet-interconnect-challenges-standards/