Gelişmiş süreç düğümleri, hem daha büyük tasarımların ele alınmasında hem de tasarım süreci karmaşıklığının artmasında EDA için zorluklar yaratır.

Tasarım çevrim süresini sıkıştırmaya yönelik sola kaydırma tasarım metodolojileri buna bir yanıttır. Bu aynı zamanda bazılarının tasarım araçlarının ve akışlarının nasıl oluşturulacağı ve optimize edileceği konusunda yeniden düşünmeye zorladı.

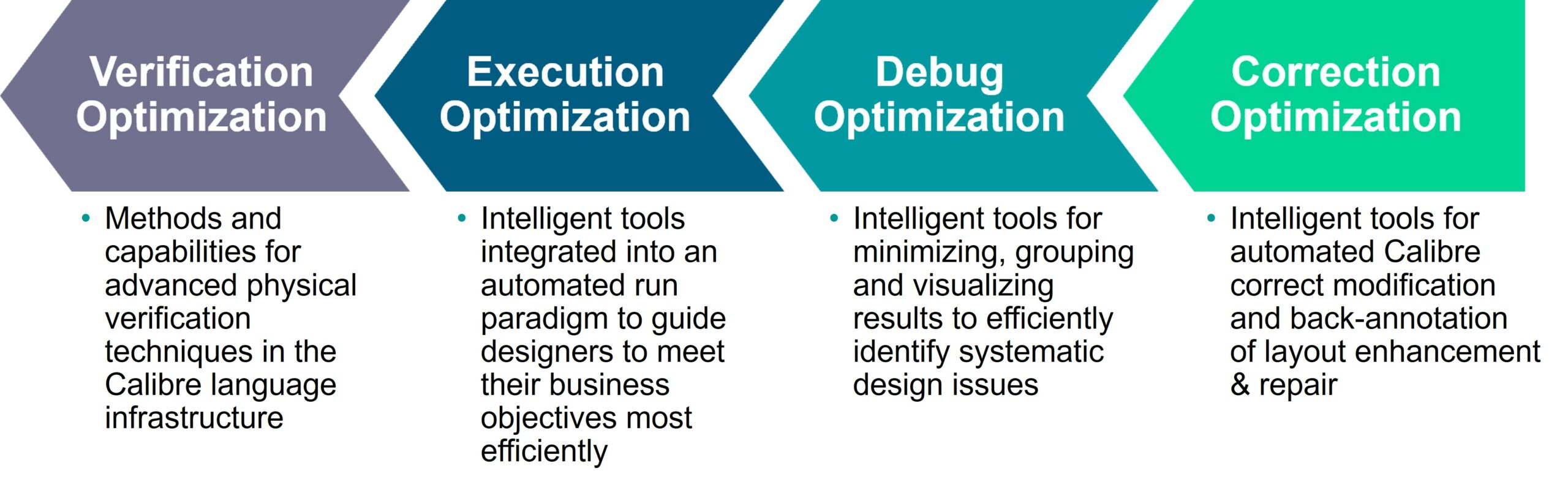

SemiWiki, Calibre'nin bir sola kay tasarımcı üretkenliğini hedefleme stratejisi birkaç ay önce, bunun sağlayabileceği faydalara ("ne") odaklanarak. Bu sefer "nasıl" konusuna, özellikle de Siemens'in Calibre'nin dediği şeye daha yakından bakacağız. optimizasyonun dört ayağı (bu diyagramlar Siemens EDA kağıdı bu temayla ilgili).

Optimize Fiziksel Doğrulama (PV) hem erken tasarım aşamalarında odaklanmış ve verimli bir şekilde kanıtlanmış imzalama yeteneklerinin sunulması hem de PV aralığının genişletilmesi anlamına gelir.

Verimli araç ve akış infaz yalnızca performans ve bellek kullanımını yönlendirmekle ilgili değildir. Çalıştırma yapılandırmalarını yapılandırmak ve optimize etmek için harcanan zamanı ve çabayı azaltmak da kritik öneme sahiptir.

Debug Erken aşamadaki doğrulama, giderek hangi ihlallerin şu anda düzeltilmesi gerektiğini tespit edebilmek ve tasarımcılara temel nedenleri hızlı bir şekilde bulma konusunda daha fazla yardım sağlamakla ilgilidir.

Calibre'yi entegre etme Düzeltme PV akışının erken aşamaya aktarılması, uygulama ve imzalama aracı kontrolleri arasındaki olası farklılıkları önleyerek tasarım süresinden ve çabasından tasarruf sağlayabilir.

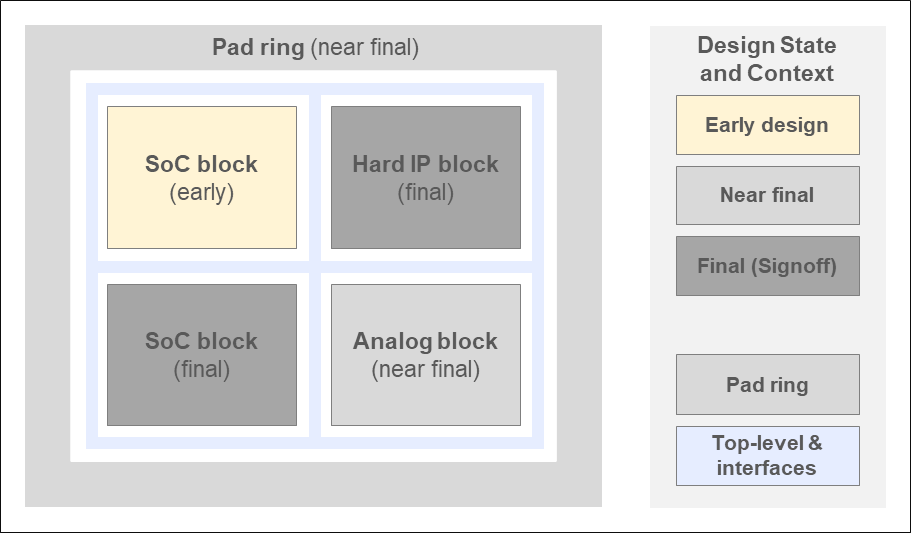

Makaleyi baştan sona okurken, tasarım süreci hakkında şu şekilde düşünmeyi faydalı buldum:

Mevcut Tasarım

- Tasarımın şu anda ilgilendiğimiz kısmı (blok, fonksiyonel ünite, çip)

- Bir tasarım durumuna sahiptir; örneğin uygulama öncesi, erken fiziksel, finale yakın, imza

Tasarım bağlamı

- Mevcut tasarımımızın etrafındaki diğer tasarım parçalarının durumları

Doğrulama amacı

- Mevcut tasarımımız için şimdi doğrulamamız gerekenler

- Mevcut tasarım durumu, bağlam ve mevcut tasarım hedefleri ve önceliklerinin bir fonksiyonu

- Çoğunlukla tam kontrollerin daha küçük bir alt kümesi

Aşağıda genellikle buna benzer bir senaryoyla karşılaşacağız.

Bazen kontrolleri gizlemek veya daha önceki aşamadaki bloklardan gelen sonuçları filtrelemek isteriz. Bazen sadece üst düzey arayüzleri kontrol etmek isteyebiliriz. Farklı ekipler aynı anda aynı veritabanı üzerinde farklı kontroller yürütüyor olabilir.

Doğrulama yapılandırması ve analizi yüksek mühendislik maliyetine sahip olabilir. Tasarım olgunlaştıkça bu durumun kapsanacak geniş senaryo dizisine yayılması nasıl önlenebilir? Calibre'nin her senaryo için kesin bir doğrulama amacı ileterek hazırlık, analiz, hata ayıklama ve düzeltme zamanını ve çabasını en aza indirerek burada karşılamaya çalıştığı asıl zorluk budur.

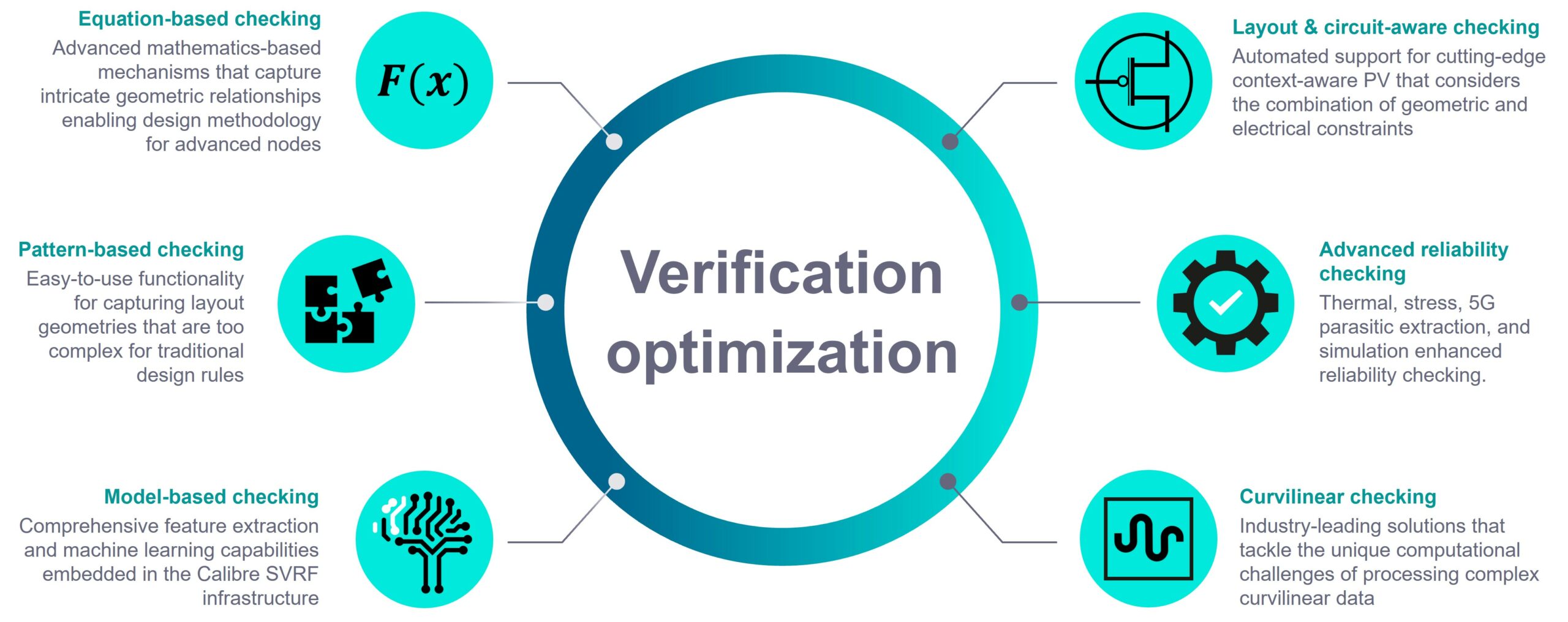

Fiziksel Doğrulamayı Genişletme

Gelişmiş düğüm fiziksel doğrulaması, Calibre nmPlatform'da hem kontrollerin nasıl yapıldığı hem de bunların artan kapsamı ve karmaşıklığı konusunda bazı temel değişikliklere yol açtı

SVRF (standart doğrulama kuralı) formatını kullanan karmaşık matematiksel denklemler gerektiren denklem tabanlı kontroller (eqDRC) buna iyi bir örnektir. Ayrıca daha programlanabilir kontrollerin ve hem kontrollerin hem de sonuç açıklamalarının Calibre araç takımına ve dil altyapısına tamamen entegre edilmesinin önemini vurgulayan bir vurgu.

PERC (programlanabilir elektrik kuralı kontrolü), geleneksel ESD'yi kapsayan ve voltaja bağlı DRC gibi daha yeni kontrollere geçiş sağlayan, doğrulama konusunda genişleyen başka bir alandır.

Daha sonra, bireysel çipler ve 3 boyutlu istiflenmiş paketler için termal ve gerilim analizi ve gelecekteki destek için eğrisel düzen kontrolleri gibi yeni ortaya çıkan teknikler var.

Makalede yararlı bir özet diyagram sunulmaktadır (burada ele alabileceğimizden çok daha ayrıntılı olarak).

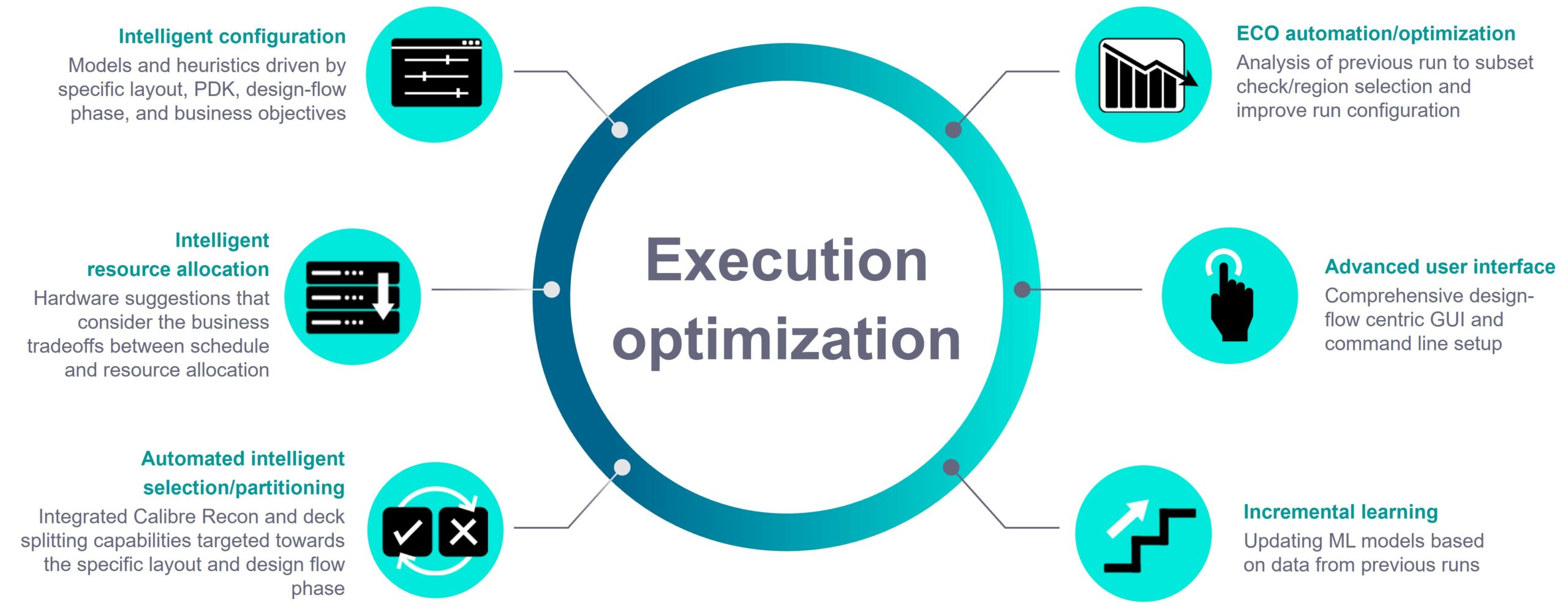

Yürütme Verimliliğini Artırma

EDA araç konfigürasyonu, yukarıdan aşağıya (tasarım kısıtlamaları) ve aşağıdan yukarıya (araç ve uygulama ayarları) bir karışımıdır; akış ilerledikçe giderek aşağıdan yukarıya ve karmaşık hale gelir. Ancak sola kaydırmalı bir akışta erken tasarım kontrolleri için gereken tüm zaman alıcı PV yapılandırma çabalarını istemiyoruz.

Calibre, geleneksel deneme-yanılma yapılandırma aramasını, tasarımcının doğrulama amacını anlayan daha akıllı, yönlendirmeli ve yapay zeka destekli bir yapılandırmayla değiştirir. Tasarımcılar, tasarımın beklenen durumu (“temizlik”) ve hatta ilgili hata türleri ve tasarımın kritik kısımları hakkında ayrıntılar sunarak çalışma süresini en aza indiren hedefli kontrol setleri oluşturabilir.

Calibre tarafından kullanılan bazı teknikler aşağıda gösterilmiştir.

Hata Ayıklamayı Hızlandırma

Tasarım bağlamına yönelik kontrollerin kolaylaştırılması, doğrulama raporlarındaki sinyal-gürültü oranını faydalı bir şekilde artırır. Ancak şu anda hangi ihlallerin ele alınması gerektiğini belirlemek (örneğin, bir tasarımcının yalnızca blok arayüzlerini doğrulaması gerekebilir) ve ardından bunların temel nedenlerini bulmak için hala yapılması gereken işler var.

Calibre, ortak temel nedenlere ilişkin değerli ipuçları ve ipuçları elde etmek için birikmiş deneyimi ve tasarım farkındalığını ortaya koyuyor - Calibre'nin hata ayıklama sinyalleri. Yapay zeka destekli teknikler, tasarımcılara bildirilen hataları analiz etme, bölümleme, kümeleme ve görselleştirme konusunda yardımcı olur.

Calibre'nin hata ayıklama özelliklerinden bazıları aşağıda gösterilmiştir.

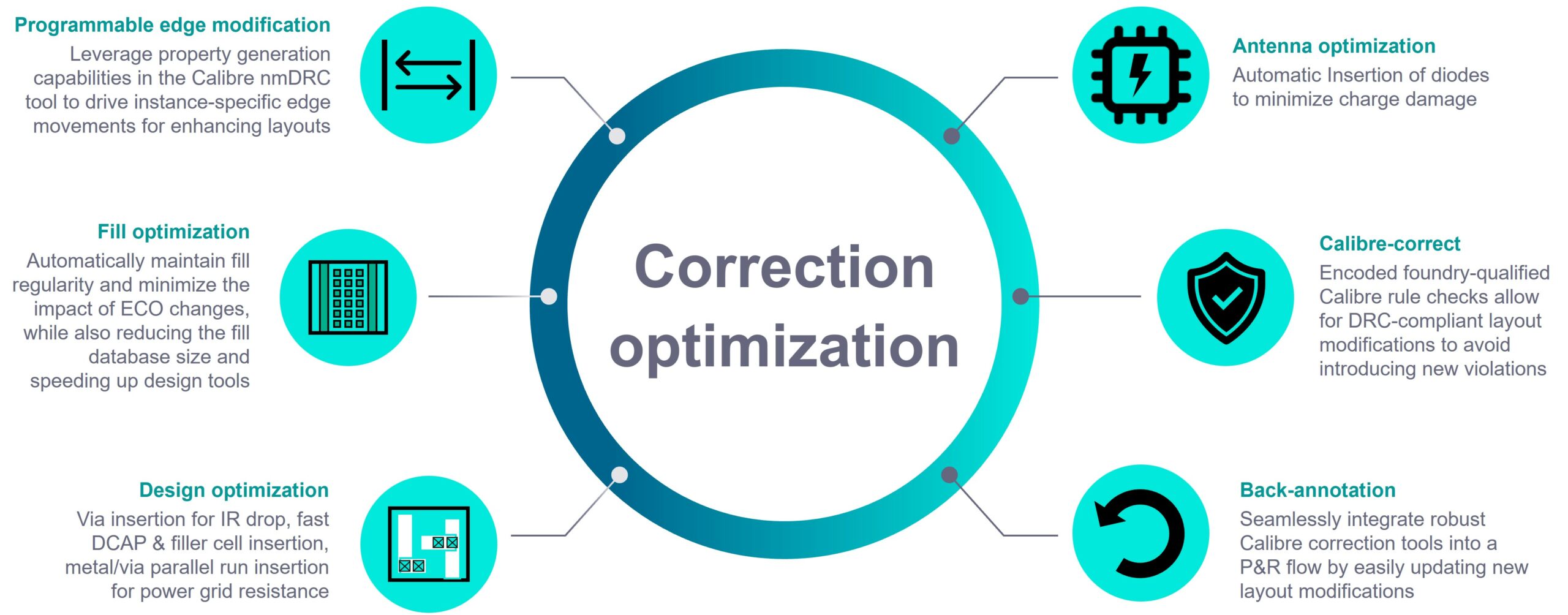

Düzeltmeyi Kolaylaştırma

Calibre PV'yi daha önceki tasarım aşamalarında çalıştırıyorsak, düzeltmeler için neden Calibre'nin kanıtlanmış inşaat bazında doğru düzen değişikliklerini ve imzalama araç setindeki optimizasyonlarını kullanmıyoruz - uygulama ve imzalama aracı kontrollerindeki potansiyel farklılıklardan kaynaklanan riskleri ortadan kaldırıyoruz? Calibre öncelikli olarak bir doğrulama aracı olmasına rağmen her zaman bazı tasarım düzeltme yeteneklerine sahiptir ve önde gelen tüm düzen akışlarıyla zaten sıkı bir şekilde entegre edilmiştir.

Ancak kritik neden, düzen araçlarının geleneksel olarak yapmaları istenen bazı görevlerde her zaman o kadar iyi olmamasıdır. Bu, ister dolgu maddesinin yerleştirilmesi durumundaki yavaşlık, ister yaptıkları işlerde kesinlik eksikliği olsun – çünkü kalite kural denetiminden çıkış yapmadıkları için – ya daha sonra yeniden çalışma ya da artan tasarım marjı anlamına gelir.

Daha önceki bir SemiWiki makalesinde özellikle ele alınmıştır Calibre Design Enhancer'ın tasarım düzeltme yetenekleri.

Makalede Calibre optimizasyonunun bazı örnekleri gösterilmektedir.

Özet

SoC tasarım marjları hakkında yakın zamanda yayınlanan bir makale, bunların her bir ana tasarım aşamasında başlangıçta bağımsız olarak nasıl uygulandığına dikkat çekti. Süreç küçülmelerinden elde edilen getirilerin azalması, bunun izin verdiği maliyetli aşırı tasarımı açığa çıkardıkça, bu durum, marjlamaya yönelik tüm süreç yaklaşımında bir değişikliği zorunlu kıldı.

Tasarım akışı araçlarıyla benzer bir noktadayız sanki. Artık "araçları yukarıya doğru" akışlar oluşturmak ve iyi tasarım akışları üretmeyi ummak yeterli değil, bunun yerine EDA araçlarını ve tasarım akışlarını birlikte optimize ettiğimiz daha "aşağıya doğru" bir yaklaşıma geçin.

Bu kesinlikle Calibre'nin sola kaydırma stratejisinin izlediği yön. optimizasyonun bu dört sütununu temel alıyoruz.

Orijinal Siemens EDA makalesinde daha fazla ayrıntıyı burada bulabilirsiniz:

IC tasarım ve uygulama akışlarına yönelik Calibre sola kaydırma çözümlerinin dört temel dayanağı.

Bu gönderiyi şu yolla paylaş:

- SEO Destekli İçerik ve Halkla İlişkiler Dağıtımı. Bugün Gücünüzü Artırın.

- PlatoData.Network Dikey Üretken Yapay Zeka. Kendine güç ver. Buradan Erişin.

- PlatoAiStream. Web3 Zekası. Bilgi Genişletildi. Buradan Erişin.

- PlatoESG. karbon, temiz teknoloji, Enerji, Çevre, Güneş, Atık Yönetimi. Buradan Erişin.

- PlatoSağlık. Biyoteknoloji ve Klinik Araştırmalar Zekası. Buradan Erişin.

- Kaynak: https://semiwiki.com/eda/siemens-eda/335057-optimizing-shift-left-physical-verification-flows-with-calibre/