Med GOMACTech konferenca, ki je prejšnji teden potekala v Južni Karolini. Imel sem Zoom klic z Deepakom Shankarjem, ustanoviteljem in podpredsednikom tehnologije pri Mirabilis Design Inc., da bi postavil vprašanja in si ogledal predstavitev v živo VisualSim – platforma za modeliranje, simulacijo, raziskovanje in sodelovanje za razvoj elektronike in SoC. Zaradi česar je VisualSim tako značilen je, da je opremljen s približno 500 bloki IP na visoki ravni, pripravljenimi za uporabo, vključno s 35 procesorji ARM, približno 100 procesorji in več kot 30 različnimi povezavami. Uporabniki VisualSim te bloke IP hitro vizualno povežejo skupaj, da ustvarijo svoje sisteme, skupaj z omrežji. Avtomobilski oblikovalec lahko modelira celotno omrežje, vključno s komunikacijami 5G, ethernetom, posodobitvami SDA in OTA z VisualSim.

Model na visoki ravni omogoča najhitrejše arhitekturno raziskovanje in sklepanje arhitekturnih kompromisov, še preden se implementacija sploh začne s kodo RTL. Modelirate lahko zapletene dejavnosti, kot so avtobus, spomini in celo predpomnilnik, ter merite stvari, kot so zakasnitve od konca do konca in zakasnitev. Inženirji lahko izmerijo, kakšno je njihovo razmerje zadetkov/zgrešenih predpomnilnikov in kaj se zgodi z zahtevami do predpomnilnikov L2. Vsi priljubljeni omrežni protokoli so modelirani: AXI, CHI, CMN600, Arteris NOC, UCIe itd.

S tem pristopom modeliranja lahko arhitekt modelira SoC, celotno letalo ali avtomobilski sistem in nato začne meriti njegovo zmogljivost, da ugotovi, ali izpolnjuje zahteve. VisualSim je večdomenski simulator, ki lahko integrira analogne, programske, energetske sisteme, digitalne in omrežne v en sam model.

Za predstavitev v živo mi je Deepak pokazal zasnovo na osnovi čipov, ki je imela ločene čiplete za DSP, GPE, procesor AI in CPE, vse skupaj povezane z uporabo UCIe, in vsak blok IP je bil parametriran, da omogoča prilagajanje in raziskovanje.

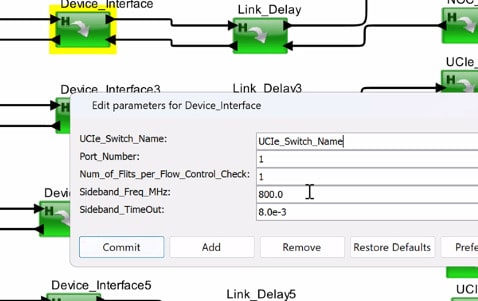

V blok UCIe je bil vključen IP, imenovan stikalo UCIe, in uporabnik lahko prilagodi ta blok s petimi parametri, vsi na visoki ravni.

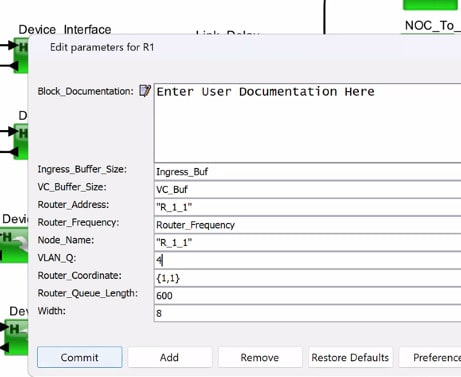

Blok IP usmerjevalnika je imel 10 parametrov za prilagajanje.

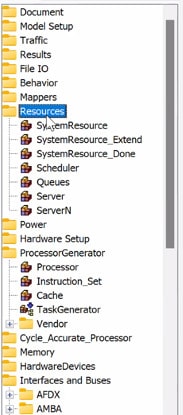

Za iskanje posameznega bloka IP je bil na levi strani grafičnega uporabniškega vmesnika na voljo drsni seznam z vsako družino IP v knjižnici. V nekaj sekundah lahko brskate, izberete in začnete prilagajati IP.

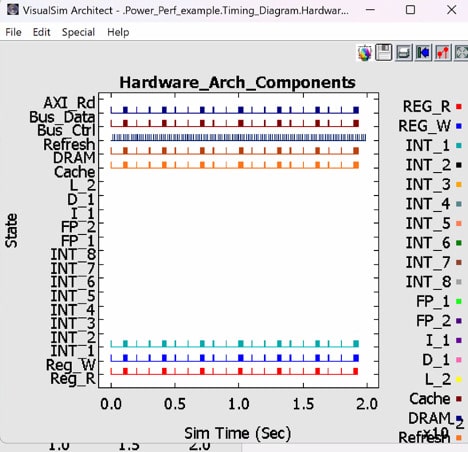

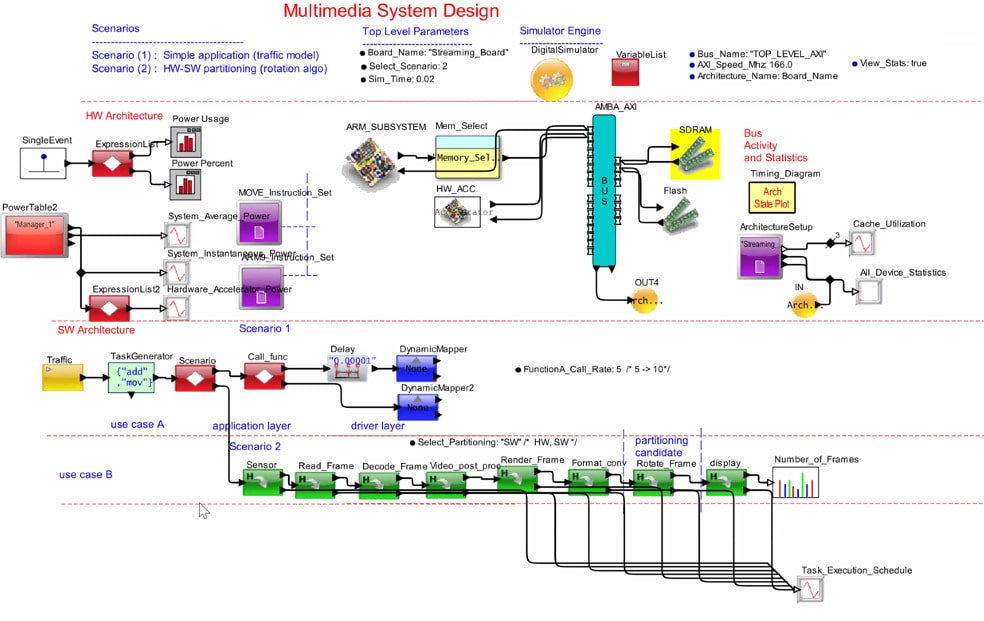

V VisualSim povezujete vsak IP v toku podatkov in ostajate na visoki ravni. Naslednja predstavitev v živo je bila namenjena zasnovi multimedijskega sistema in za simulacijo 20 ms je bilo potrebnih približno 15 sekund stenskega časa, ki se izvaja na prenosnem računalniku. Med izvajanjem simulacije si lahko ogledate zmogljivost sistema kot trenutno moč, merite uporabo cevovoda, uporabo predpomnilnika, uporabo pomnilnika in si celo ogledate časovni diagram. Ta simulacija v realnem času je sprožila 7.5 milijona dogodkov in stranka je zgradila ta model v manj kot 2 tednih, ki je vključeval celoten sistem na čipu.

Drug primer stranke, ki ga je omenil Deepak, vključuje 45 mojstrov in je bil v celoti preizkušen v približno 4 tednih.

Pogledate lahko znotraj katerega koli od blokov IP in analizirate meritve, kot je uspešno/neuspešno, nato razumete, zakaj ni uspelo. Obstaja celo mehanizem AI, ki pomaga pri učinkovitejši analizi podatkov, na primer pri iskanju prekoračitve medpomnilnika, ki je povzročila napako. Medtem ko se vaš model izvaja, so zajeti analitiki za pomoč pri merjenju zmogljivosti sistema in prepoznavanju arhitekturnih ozkih grl.

VisualSim se posodobi dvakrat na leto, nato pa so na voljo posodobitve popravkov, ko se dodajo novi bloki IP. Arhitekt definira zahteve v Excelovi datoteki z meritvami, kot so omejitve zakasnitve in zasedenost medpomnilnika.

Uporabniki VisualSim lahko določijo obseg velikosti tovora glede na bajte, razpone hitrosti in želene vrednosti. Vaš sistemski model lahko preletite med kombinacijami, da poiščete najboljši nabor parametrov. Simulator celo razume, kako raziskati najmanjše, največje in želene vrednosti. Določiti morate, kateri sistemski parametri bodo raziskani. Nato je bila prikazana predstavitev multimedijskega sistema in nato simulirana v živo.

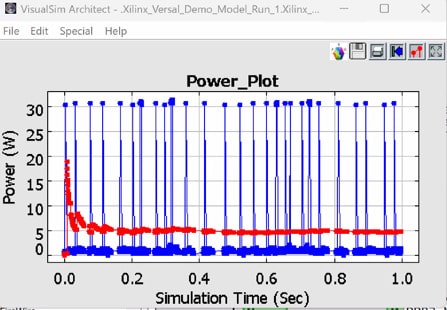

Za blok FPGA izberete prodajalca in številko dela, nato pa si lahko po izvedbi simulacije ogledate zakasnitev za vsako nalogo in statistiko kanala NOC. Prikazana je bila krivulja moči za 1 sekundo delovanja pri uporabi delov Xilinx Versal.

Vse predstavitve v živo so se izvajale na prenosniku Windows. Drugi podprti operacijski sistemi so: Unix, Mac. Zagon VisualSim zahteva minimalno HW infrastrukturo, ker so modeli visoke ravni.

Uporabniki VisualSim prejmejo več kot 500 primerov, ki so vnaprej zgrajeni, da vam pomagajo hitro začeti, kot je celoten komunikacijski sistem z anteno, sprejemnikom, FPGA z osnovnim pasom in vmesnikom Ethernet. Sistemski arhitekti, ki uporabljajo VisualSim, lahko sodelujejo z vsemi strokovnjaki na nižji ravni, kot so oblikovalci RTL.

Kompromise na sistemski ravni je mogoče modelirati in ovrednotiti, na primer:

- Prehod iz modulacije 64-QAM v QPSK

- Hitrejši do počasnejši procesor

- Spreminjanje specifikacij Ethernet

Če začnete z VisualSim za modeliranje, implementacijo in nato merjenje, pričakujte 95-odstotno natančnost v primerjavi z rezultati implementacije RTL. Obljuba uporabe modelov visoke ravni je odprava težav z zmogljivostjo pred implementacijo ali integracijo. Za celoten model sistema dejansko ni potrebno kodiranje.

Mirabilis ima do zdaj 65 strank po vsem svetu in okoli 250 izvedenih projektov. Nekatere znane stranke vključujejo: NASA, Samsung, Qualcomm, Broadcom, GM, Boeing, HP, Imagination, Raytheon, AMD, Northrup Grumman.

Povzetek

V starih časih je načrtovalec sistemov morda med jedjo v restavraciji narisal svoje zamisli na prtiček, nato pa se vrnil na delo in sestavil nekaj Excelovih preglednic s skrivnostnimi enačbami, da bi ustvaril model. Danes je na voljo nova izbira in to je dajanje VisualSim iz Mirabilisa poskusi. Zdaj lahko modelirate celoten sistem v samo nekaj tednih, skupaj z arhitekturnimi kompromisi med izvajanjem dejanskih simulacij, vse preden se lotite podrobnih podrobnosti izvedbe.

Sorodni dnevniki

Delite to objavo prek:

- Distribucija vsebine in PR s pomočjo SEO. Okrepite se še danes.

- PlatoData.Network Vertical Generative Ai. Opolnomočite se. Dostopite tukaj.

- PlatoAiStream. Web3 Intelligence. Razširjeno znanje. Dostopite tukaj.

- PlatoESG. Ogljik, CleanTech, Energija, Okolje, sončna energija, Ravnanje z odpadki. Dostopite tukaj.

- PlatoHealth. Obveščanje o biotehnologiji in kliničnih preskušanjih. Dostopite tukaj.

- vir: https://semiwiki.com/ip/343387-a-modeling-simulation-exploration-and-collaborative-platform-to-develop-electronics-and-socs/