При рассмотрении архитектуры SoC легко попасть в ловушку простых повествований. Они предполагают, что центр вычислений вращается вокруг центрального ядра или основного кластера, обычно Arm, а в последнее время, возможно, варианта RISC-V. Добавьте пару ускорителей, а остальное уже детали. Но для сегодняшних конкурентоспособных продуктов такая точка зрения является опасным упрощением. Большинство продуктов необходимо настраивать в зависимости от приложения, производительности, времени автономной работы и стоимости единицы продукции. Во многих системах ядра ЦП общего назначения по-прежнему могут управлять управлением, однако тяжелая работа для самых популярных приложений перешла к проверенным основным DSP или ускорителям искусственного интеллекта специального назначения. В небольших, чувствительных к цене и потребляющих электроэнергию системах DSP также могут управлять управлением и искусственным интеллектом в одном ядре.

Когда только DSP может выполнить эту работу

Хотя ЦП общего назначения или ЦП с расширениями DSP могут выполнять некоторую обработку DSP, они не предназначены для обработки потоков потоковых данных с высокой пропускной способностью, характерных для широкого спектра протоколов связи, высококачественных аудиоприложений, высококачественной обработки сигналов изображений, критически важных с точки зрения безопасности Радарная и лидарная обработка или обработка нейронных сетей, распространенная при распознавании и классификации объектов.

DSP изначально поддерживают арифметику с фиксированной и плавающей запятой, необходимую для обработки аналоговых значений, которые доминируют в обработке сигналов, и поддерживают конвейеры массового параллельного выполнения для ускорения сложных вычислений, через которые протекают эти значения (например, БПФ и фильтры), а также поддерживают значительную пропускную способность. для потоковой передачи данных. Тем не менее, эти DSP по-прежнему являются процессорами, полностью программируемыми, поэтому сохраняют гибкость и готовность к будущему, которых ожидают разработчики приложений. Вот почему, после многих лет повсеместного распространения встроенных процессоров Arm и новой волны вариантов RISC-V, DSP по-прежнему лежат в основе устройств, которые вы используете каждый день, включая средства связи, автомобильные информационно-развлекательные системы и ADAS, а также домашнюю автоматизацию. Они также поддерживают функции искусственного интеллекта во многих компактных энергочувствительных устройствах — интеллектуальных колонках, интеллектуальных пультах дистанционного управления и даже интеллектуальных наушниках, слуховых аппаратах и наушниках.

Серия Tensilica LX и LX8

Серия Tensilica Xtensa LX на протяжении многих лет предлагает стабильную платформу DSP. Пара статистических данных, которые были для меня новыми, заключается в том, что Tensilica насчитывает более 60 миллиардов устройств, проданных на базе своих ядер, и они занимают второе место по доходам от лицензирования процессоров (после Arm), что подчеркивает, насколько доминируют их решения в этой области.

Клиенты зависят от стабильности платформы, поэтому Tensilica медленно развивает архитектуру; последний выпуск, LX7, вышел еще в 2016 году. Как и следовало ожидать, Tensilica гарантирует, что платформы остаются совместимыми со всеми основными операционными системами, инструментами отладки и решениями ICE, поддерживаемыми экосистемой стороннего программного обеспечения/инструментов разработки. ISA была расширяемой с самого начала, задолго до появления RISC-V, предлагая те же возможности дифференциации, которые сейчас популярны в RISC-V. Платформа в первую очередь ориентирована на встроенные приложения, обеспечивая высокую производительность при низком энергопотреблении.

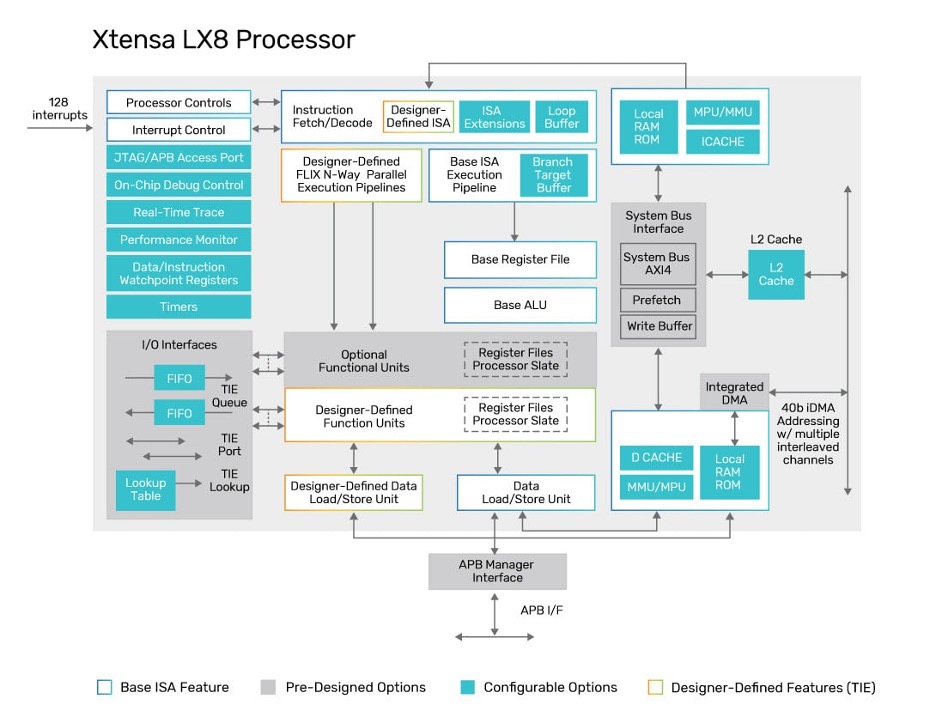

Последняя версия этой серии, LX8, была выпущена недавно и добавляет в архитектуру две основные функции для поддержки растущего интеллекта на периферии: новую подсистему памяти L2 и интегрированный DMA. Мне всегда нравится рассматривать подобные функции с точки зрения того, как они позволяют достичь более масштабных системных целей, поэтому вот мое мнение.

Во-первых, кэш L2 улучшит производительность при промахах L1, что, например, должно привести к более высокой частоте кадров в секунду для приложений распознавания объектов. L2 также можно разделить на секции кэша и фиксированной памяти, что обеспечивает гибкость приложений за счет оптимизации памяти L2 для различных рабочих нагрузок. Встроенный DMA, помимо других функций, поддерживает передачу 1D, 2D и 3D, что очень важно для функций искусственного интеллекта. 1D может поддерживать голосовой поток, 2D — изображение, а 3D будет необходим для кубов данных радара/лидара. Эта аппаратная поддержка еще больше увеличит частоту кадров. Кроме того, iDMA в LX8 поддерживает декомпрессию нулевых значений — знакомую необходимость передачи весов обученной сети, когда значительные участки значений могут быть обнулены либо посредством квантования, либо сокращения и сжимаются до чего-то вроде <12:0>, а не до строки из двенадцати нулей. . Это хорошо для сжатия, но расширенная структура должна быть восстановлена, прежде чем тензорные операции можно будет применять в выводе. Опять же, аппаратная поддержка ускоряет эту задачу, сокращая задержку между обновлениями матрицы весов.

Это не революционные изменения, но они необходимы для производителей продуктов, которые должны оставаться на переднем крае производительности, сохраняя при этом низкое энергопотребление. И SK Hynix, и Synaptics предоставили свои одобрения. Вы можете прочитать пресс-релиз ВОТ.

Поделитесь этим постом через:

- SEO-контент и PR-распределение. Получите усиление сегодня.

- PlatoData.Network Вертикальный генеративный ИИ. Расширьте возможности себя. Доступ здесь.

- ПлатонАйСтрим. Интеллект Web3. Расширение знаний. Доступ здесь.

- ПлатонЭСГ. Углерод, чистые технологии, Энергия, Окружающая среда, Солнечная, Управление отходами. Доступ здесь.

- ПлатонЗдоровье. Биотехнологии и клинические исследования. Доступ здесь.

- Источник: https://semiwiki.com/artificial-intelligence/335014-cadence-tensilica-spins-next-upgrade-to-lx-architecture/