В проектах ИС предусмотрены приложения физической проверки, такие как Layout Versus Schematic (LVS) на уровне транзисторов, чтобы гарантировать эквивалентность компоновки и схем, кроме того, существует проверка электрических правил (ERC) для соединений с областями скважин, называемая мягкой проверкой. Соединения всех устройств должны иметь наиболее стабильные сигналы напряжения. Следовательно, путь должен проходить через слои металла, чтобы уменьшить сопротивление и такие факторы, как падение ИК-излучения. При обнаружении связей другие материалы, такие как Уэллс, были обязательными. Мягкие проверки — это метод, наиболее часто используемый для обнаружения такой ситуации. калибр Линейка продуктов Siemens — самый популярный инструмент для проверки DRC и LVS, поэтому я прочитал техническую статью Терри Микса, чтобы узнать больше о мягких проверках.

Соединение двух металлических слоев в схеме микросхемы требует точного выравнивания обоих металлических слоев и переходного слоя. Вот сравнение с использованием как вида сбоку, так и вида сверху вниз, где первый пример не соединен, поскольку Metal1 и Metal 2 не перекрываются, а второй пример соединен правильно.

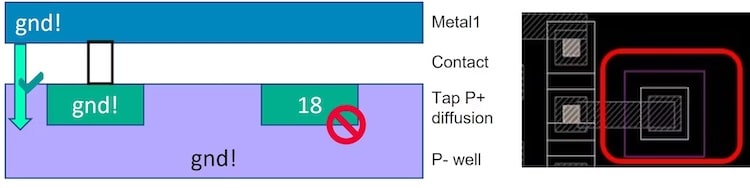

Мы хотим, чтобы наш инструмент ERC выявлял ошибки подключения скважин во время программных проверок, чтобы их можно было исправить. Следующая схема микросхемы имеет ошибку подключения и показана на виде сбоку, где сигнал Metal1, обозначенный как Gnd, подключен к области диффузии, называемой диффузией отвода. С правой стороны находится еще один слой Metal1 с рассеянием, но это соединение создает путь с высоким сопротивлением между Rwell и Gnd и помечается как ошибка при программной проверке.

Другой пример ошибки мягкого соединения происходит в макете IC ниже, где мы можем применить только одно имя к каждому полигону. Цифровая сеть электропитания VDD не может сосуществовать с аналоговой сетью электропитания AVDD, и нам необходимо разделить их на две формы. Мягкие проверки помогают выявить эти проблемы.

Компоновка микросхемы с цифровыми и аналоговыми источниками питания может оказаться довольно сложной для правильной компоновки, поэтому еще важнее проводить мягкие проверки.

Мягкие проверки включены во время запуска LVS, и с Калибр nmLVS есть отчет о результатах программной проверки, который затем можно просмотреть с помощью Калибр РВЭ Зритель.

При нажатии на результаты RVE вы узнаете, какая ячейка имеет ошибку программной проверки, сетевые имена, верхние и нижние имена и другие свойства. Эта информация помогает определить, что нужно исправить в макете микросхемы. При нажатии на нижний слой, например PWell, для ошибки программной проверки геометрия отображается желтым цветом.

При той же ошибке программной проверки нажатие на верхний слой показывает:

Во время отладки вы также можете отображать все формы верхнего слоя: зеленые фигуры — это выбранные фигуры верхнего слоя цепи, а желтые — отклоненная форма верхнего слоя цепи.

Отладка ошибок программной проверки с помощью RVE включает в себя нажатие на связность выбранных и отклоненных цепей. Окна Net Info показывают подробную информацию, например, какие слои задействованы и отсутствуют ли в фигурах связность. Просмотр того, какие порты подключены к сети, позволяет выявить отсутствие ошибок VDD или GND. Этот пример показывает, что сеть 18 отклонена, поскольку у нее отсутствует связь с Metal1.

Обзор

Проверки LVS обязательны для обеспечения безошибочной компоновки микросхемы, а мягкие проверки являются частью проверок LVS. В инструменте Caliber nmLVS компании Siemens есть проверенный процесс отладки, который использует RVE, чтобы помочь дизайнерам макетов быстро выявлять сбои программной проверки, чтобы дизайнеры могли вносить исправления и выполнять повторную проверку до тех пор, пока все проверки не будут пройдены. Компания Siemens написала технический документ для чтения в Интернете. Обнаружение и отладка ошибок подключения программной проверки.

Похожие статьи

Поделитесь этим постом через:

- SEO-контент и PR-распределение. Получите усиление сегодня.

- PlatoData.Network Вертикальный генеративный ИИ. Расширьте возможности себя. Доступ здесь.

- ПлатонАйСтрим. Интеллект Web3. Расширение знаний. Доступ здесь.

- ПлатонЭСГ. Углерод, чистые технологии, Энергия, Окружающая среда, Солнечная, Управление отходами. Доступ здесь.

- ПлатонЗдоровье. Биотехнологии и клинические исследования. Доступ здесь.

- Источник: https://semiwiki.com/eda/342526-soft-checks-are-needed-during-electrical-rule-checking-of-ic-layouts/