Podczas GOMACTech konferencja, która odbyła się w zeszłym tygodniu w Karolinie Południowej, rozmawiałem przez Zoom z Deepakiem Shankarem, założycielem i wiceprezesem ds. technologii w Mirabilis Design Inc., aby zadać pytania i obejrzeć prezentację na żywo VisualSim – platforma do modelowania, symulacji, eksploracji i współpracy w celu opracowywania elektroniki i układów SoC. To, co sprawia, że VisualSim jest tak wyjątkowy, to fakt, że jest dostarczany w zestawie z około 500 blokami IP wysokiego poziomu, gotowymi do użycia, w tym 35 procesorami ARM, około 100 procesorami i ponad 30 różnymi interkonektami. Użytkownicy VisualSim szybko łączą ze sobą te bloki IP, tworząc swoje systemy wraz z sieciami. Projektant motoryzacyjny może modelować całą sieć, w tym komunikację 5G, aktualizacje Ethernet, SDA i OTA za pomocą VisualSim.

Model wysokiego poziomu pozwala na najszybszą eksplorację architektury i dokonywanie kompromisów architektonicznych na długo przed rozpoczęciem wdrażania z kodem RTL. Możesz modelować złożone działania, takie jak magistrala, pamięci, a nawet pamięć podręczna, mierząc takie elementy, jak kompleksowe opóźnienia i opóźnienia. Inżynierowie mogą zmierzyć współczynnik trafień/porażek w pamięci podręcznej i co dzieje się z żądaniami do pamięci podręcznej L2. Modelowane są wszystkie popularne protokoły sieciowe: AXI, CHI, CMN600, Arteris NOC, UCIe itp.

Dzięki takiemu podejściu do modelowania architekt może modelować SoC, kompletny samolot lub system samochodowy, a następnie rozpocząć pomiary jego wydajności, aby sprawdzić, czy spełnia wymagania. VisualSim to wielodomenowy symulator, który może zintegrować systemy analogowe, oprogramowanie, systemy zasilania, cyfrowe i sieciowe w jeden model.

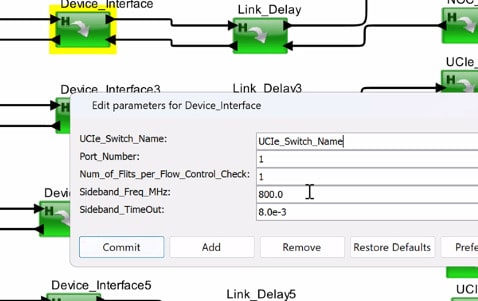

Na potrzeby demonstracji na żywo Deepak pokazał mi projekt oparty na chipletach, który miał oddzielne chiplety dla DSP, GPU, procesora AI i CPU, wszystkie połączone razem za pomocą UCIe, a każdy blok IP został sparametryzowany, aby umożliwić dostosowywanie i eksplorację.

Do bloku UCIe wprowadzono adres IP zwany przełącznikiem UCIe, a użytkownik może dostosować ten blok za pomocą pięciu parametrów, a wszystko to na wysokim poziomie.

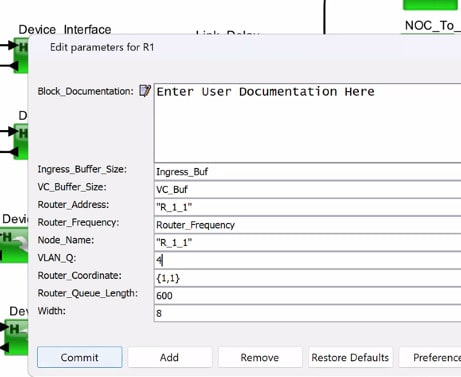

Blok IP routera miał 10 parametrów do dostosowania.

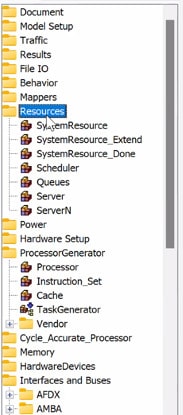

Aby znaleźć każdy blok IP, po lewej stronie GUI znajdowała się przewijana lista zawierająca każdą rodzinę adresów IP w bibliotece. W ciągu kilku sekund możesz przeglądać, wybierać i rozpocząć dostosowywanie adresu IP.

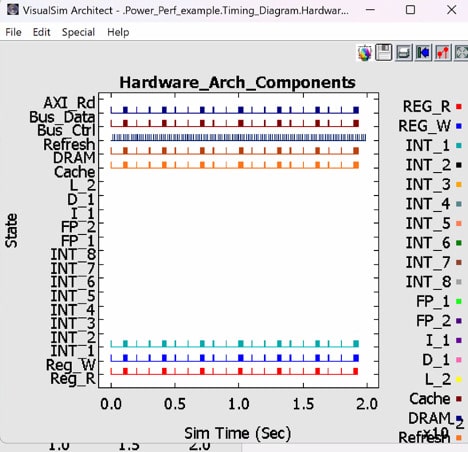

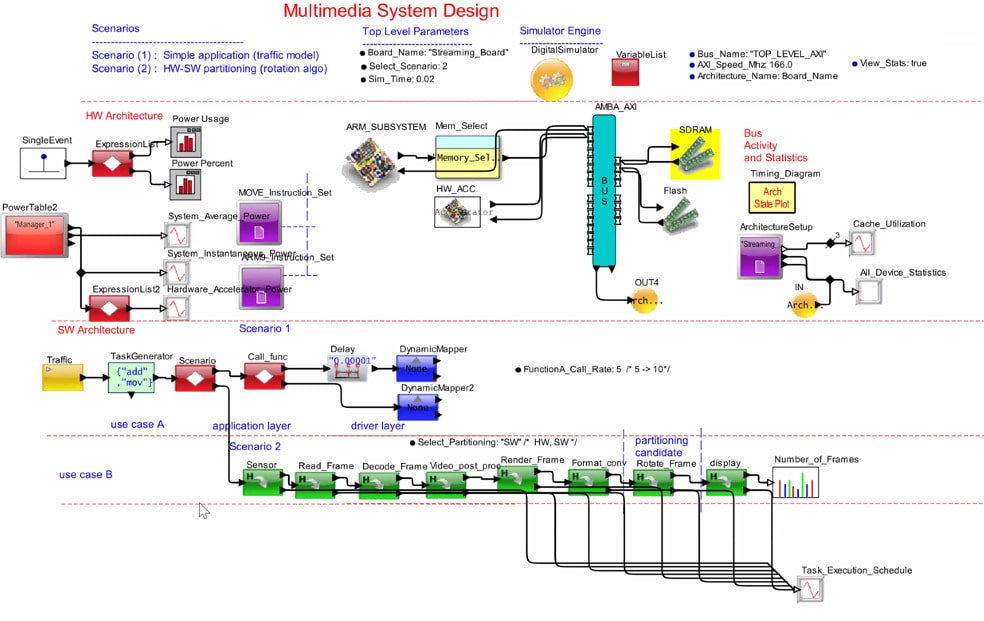

W VisualSim łączysz każdy adres IP w przepływie danych, pozostając na wysokim poziomie. Następne demo na żywo dotyczyło projektu systemu multimedialnego, a symulacja czasu 20 ms zajęła około 15 sekund czasu pracy na ścianie, pracując na laptopie. Podczas trwania symulacji można wyświetlić wydajność systemu jako moc chwilową, zmierzyć wykorzystanie rurociągu, wykorzystanie pamięci podręcznej, wykorzystanie pamięci, a nawet wyświetlić diagram czasowy. Ta symulacja w czasie rzeczywistym wywołała 7.5 miliona zdarzeń, a klient zbudował ten model w niecałe 2 tygodnie, co obejmowało cały SoC.

Inny przykład klienta, o którym wspomniał Deepak, obejmuje 45 mistrzów i został ukończony w około 4 tygodnie, w pełni przetestowany.

Możesz zajrzeć do dowolnego bloku IP i przeanalizować metryki, takie jak pass/fail, a następnie zrozumieć, dlaczego się nie udało. Dostępny jest nawet silnik sztucznej inteligencji, który pomaga efektywniej analizować dane, na przykład znajdować przepełnienie bufora, które spowodowało awarię. Podczas działania modelu rejestrowane są analizy, które pomagają mierzyć wydajność systemu i identyfikować wąskie gardła w architekturze.

VisualSim jest aktualizowany dwa razy w roku, a po dodaniu nowych bloków IP wydawane są aktualizacje. Architekt definiuje wymagania w pliku Excel, uwzględniając takie metryki, jak limity opóźnień i zajętość bufora.

Użytkownicy VisualSim mogą definiować zakres rozmiaru ładunku pod względem bajtów, zakresów prędkości i preferowanych wartości. Model systemu można przeglądać w różnych kombinacjach, aby znaleźć najlepszy zestaw parametrów. Symulator rozumie nawet, jak badać wartości minimalne, maksymalne i preferowane. Możesz zdefiniować, które parametry systemu będą badane. Następnie pokazano demonstrację systemu multimedialnego, a następnie przeprowadzono symulację na żywo.

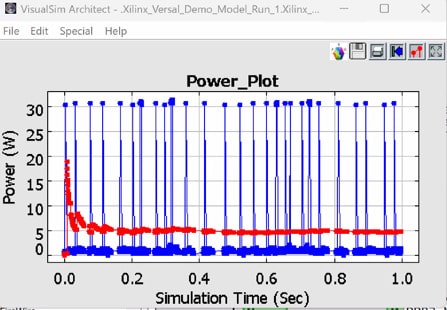

W przypadku bloku FPGA wybierasz dostawcę i numer części, a następnie możesz zobaczyć opóźnienie dla każdego zadania i statystyki kanału NOC po przeprowadzeniu symulacji. Pokazano wykres mocy dla 1 sekundy działania przy użyciu części Xilinx Versal.

Wszystkie demonstracje na żywo były uruchamiane na laptopie z systemem Windows. Inne obsługiwane systemy operacyjne to: Unix, Mac. Uruchamianie VisualSim wymaga minimalnej infrastruktury sprzętowej, ponieważ modele są na wysokim poziomie.

Użytkownicy VisualSim otrzymują ponad 500 gotowych przykładów, które pomogą Ci szybko rozpocząć pracę, jak kompletny system komunikacyjny z anteną, transceiverem, FPGA z pasmem podstawowym i interfejsem Ethernet. Architekci systemów korzystający z VisualSim mogą współpracować ze wszystkimi specjalistami niskiego szczebla, takimi jak projektanci RTL.

Można modelować i oceniać kompromisy na poziomie systemu, takie jak:

- Zmiana modulacji z 64-QAM na QPSK

- Szybszy lub wolniejszy procesor

- Zmiana specyfikacji Ethernetu

Jeśli zaczniesz od VisualSim, aby modelować, wdrażać, a następnie mierzyć, możesz spodziewać się dokładności na poziomie 95% w porównaniu z wynikami wdrożenia RTL. Obietnicą stosowania modeli wysokiego poziomu jest wyeliminowanie problemów z wydajnością przed wdrożeniem lub integracją. Tak naprawdę nie jest wymagane kodowanie całego modelu systemu.

Mirabilis ma dotychczas 65 klientów na całym świecie i zrealizował około 250 projektów. Do znanych klientów należą: NASA, Samsung, Qualcomm, Broadcom, GM, Boeing, HP, Imagination, Raytheon, AMD, Northrup Grumman.

Podsumowanie

W dawnych czasach projektant systemów mógł rysować swoje pomysły na serwetce podczas jedzenia w restauracji, a następnie wracać do pracy i łączyć arkusze kalkulacyjne Excela z tajemniczymi równaniami, aby stworzyć model. Dzisiaj mamy nowy wybór i jest nim dawanie VisualSim od Mirabilis, spróbuj. Możesz teraz modelować cały system w ciągu zaledwie kilku tygodni, dokonując kompromisów architektonicznych podczas przeprowadzania rzeczywistych symulacji, a wszystko to przed zapoznaniem się ze szczegółowymi szczegółami implementacji.

Powiązane blogi

Udostępnij ten post przez:

- Dystrybucja treści i PR oparta na SEO. Uzyskaj wzmocnienie już dziś.

- PlatoData.Network Pionowe generatywne AI. Wzmocnij się. Dostęp tutaj.

- PlatoAiStream. Inteligencja Web3. Wiedza wzmocniona. Dostęp tutaj.

- PlatonESG. Węgiel Czysta technologia, Energia, Środowisko, Słoneczny, Gospodarowanie odpadami. Dostęp tutaj.

- Platon Zdrowie. Inteligencja w zakresie biotechnologii i badań klinicznych. Dostęp tutaj.

- Źródło: https://semiwiki.com/ip/343387-a-modeling-simulation-exploration-and-collaborative-platform-to-develop-electronics-and-socs/