W dniu 13 września 2021 r. spółka Andes Technology Corporation pomyślnie przeprowadziła ofertę publiczną GDR (Globalny kwit depozytowy) na Giełdzie Papierów Wartościowych w Luksemburgu. W tamtym czasie Andes stał się jedynym międzynarodowym publicznym dostawcą protokołu IP procesorów w architekturze zestawu instrukcji RISC-V (ISA). Umożliwiło to inwestorom na całym świecie udział we wzroście Andów przewidzianym dla RISC-V. Ten zastrzyk kapitału podsyciłby ambicje Andes, aby stać się liderem na szybko rozwijającym się, szybko rozwijającym się rynku otwartego standardu RISC-V. W 2015 roku, uznając ogromny potencjał RISC-V ISA, Andes został założycielem i członkiem głównym RISC-V International.

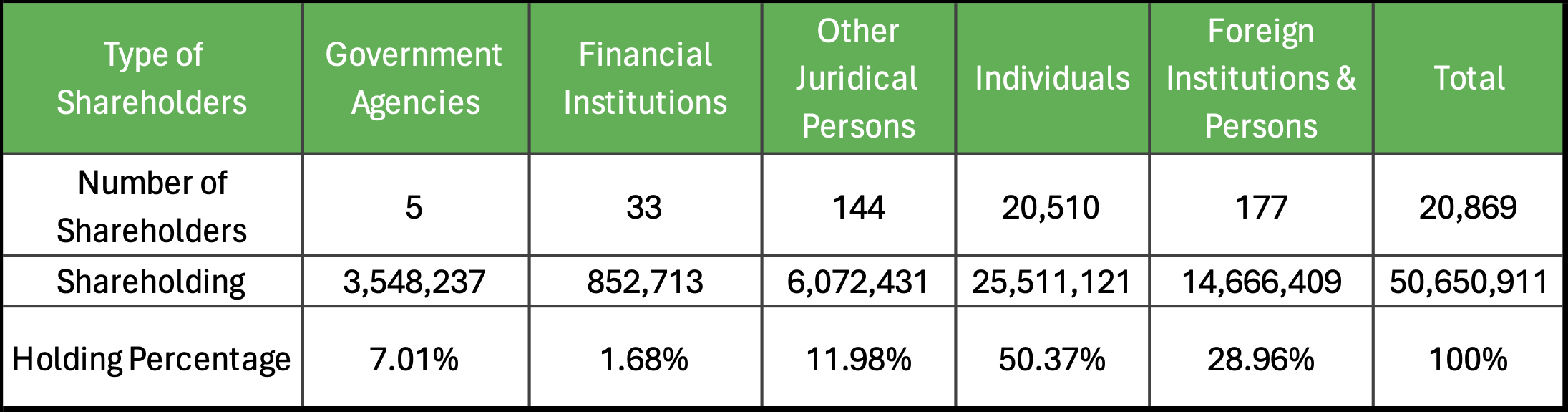

Stan na 2 kwietnia 2023 r.; Jednostka: Akcje,%

Inwestycja opłaciła się szczególnie dlatego, że zbiegła się z ratyfikacją rozszerzenia wektorowego RISC-V w listopadzie 2021 r. Wydarzenie to stanowiło punkt zwrotny w ewolucji architektury zestawu instrukcji RISC-V. Rozszerzenie wektora RISC-V pojawiło się w czasie, gdy przetwarzanie w centrach danych przechodziło z przetwarzania ogólnego na przetwarzanie AI, które obsługuje niezwykle duże zbiory danych. Przetwarzanie wektorowe przoduje w wydajnym przetwarzaniu dużych tablic lub danych strukturalnych. Przetwarzanie wektorów może sprawić, że RISC-V stanie się kolejnym ważnym ISA na świecie.

Wysoce równoległa architektura procesora wektorowego zmniejsza opóźnienia i obciążenie. Osiąga lepszą efektywność energetyczną poprzez maksymalizację wykorzystania zasobów procesora i minimalizację cykli bezczynności, zapewniając w ten sposób wyższą wydajność na wat. Co więcej, sprzęt do implementacji jednostek przetwarzania wektorowego (VPU) i rejestrów wektorowych RISC-V jest prostszy niż wysoce równoległe architektury używane do przetwarzania grafiki. A VPU zapewniają znacznie mniej złożony model programowania.

Zespoły badawczo-rozwojowe Andes zarówno w Ameryce Północnej, jak i powiększony personel na Tajwanie skupiły się na opracowywaniu najnowocześniejszych architektur dla wysokiej klasy procesorów RISC-V. Warto zauważyć, że obaj osiągnęli znaczący kamień milowy, opracowując pierwszy silnik wektorowy RISC-V (RVV), AndesCore™ NX27V, w oparciu o specyfikację RISC-V International RVV. Projekt, będący dowodem zwinności i innowacyjności zespołu inżynierów Andes, został ukończony w ciągu roku i oparty na wersji V0.8 specyfikacji rozszerzenia wektora RISC-V, a później zmodyfikowany do wersji V1.0 po ratyfikacji RVV. To osiągnięcie doprowadziło do kilku znaczących zwycięstw w projektowaniu OEM.

W zeszłym roku na konferencji International Symposium on Computer Architecture (ISCA) 2023 w Orlando na Florydzie firma META przedstawiła swój artykuł zatytułowany „MTIA: First Generation Silicon Targeting Meta's Rekomendacja Systems”, który dotyczy centrum danych firmy i projektu serwerów AI. W konstrukcji serwera znajdują się 64 elementy przetwarzające (PE), które obsługują specjalnie zbudowany, zastrzeżony akcelerator MRETA. Każdy PE zawiera dwa procesory: jeden skalarny i jeden wektorowy. Obydwa są urządzeniami Andes IP, które inżynierowie META w dużym stopniu dostosowali do indywidualnych potrzeb, korzystając z rozszerzeń Andes Custom Extensions (ACE) w celu stworzenia całkowicie unikalnego rozwiązania ukierunkowanego na specyficzne wymagania obliczeniowe AI firmy META.

Projekt potwierdził skuteczność RISC-V z rozszerzeniami Vector Extensions jako potężnego rozwiązania zaspokajającego potrzeby centrów danych opartego na sztucznej inteligencji w czasach, gdy zapotrzebowanie na sprzęt do przetwarzania danych w centrach danych eksploduje. Według Analiza rynku na przyszłośćraport „Data Center CPU Market Outlook (2023–2033)” Oczekuje się, że rynek procesorów do centrów danych znacząco wzrośnie w ciągu najbliższych kilku lat, napędzany rosnącym zapotrzebowaniem na przetwarzanie w chmurze, analizę dużych zbiorów danych i sztuczną inteligencję (AI) . Do kluczowych czynników tego wzrostu należy potrzeba szybszego przetwarzania danych, zwiększona wydajność i obniżone koszty.

W 2021 r. oprócz rozszerzeń wektorowych RISC-V International ratyfikowało 11 kolejnych rozszerzeń. Rysunek 1 ilustruje plan działania produktu Andes obsługujący te rozszerzenia. Do końca 2022 r. dostarczono N25F-SE, 27 Series i 45, a w 2023 r. firma Andes dostarczyła na rynek sześć nowych rdzeni RISC-V, takich jak D25F-SE, D23, N225, NX45V, AX45MPV jak również AX65. Plan rozwoju obejmuje energooszczędny i wysoce zabezpieczony podstawowy procesor RISC-V AndesCore™ D23 aż po AX65, pierwszy z serii 60, który został wydany w czwartym kwartale 2023 r. i jest obecnie dostarczany do projektów klientów.

AX65 to 13-stopniowy, 4-procesorowy, 64-bitowy procesor poza kolejnością z profilem RVA 22 (profil RVA22U64 określa funkcje ISA dostępne dla środowisk wykonawczych w trybie użytkownika w 64-bitowych procesorach aplikacji). Wyposażona w 13-stopniowy potok, 4-stopniowe dekodowanie i 8-stopniowe wykonywanie poza kolejnością, seria jest przeznaczona dla gniazd procesorów aplikacyjnych systemu Linux dla komputerów, sieci i wysokiej klasy kontrolerów.

AX65 umożliwia klastry wielordzeniowe od jednego do czterech do ośmiu rdzeni. Wydajność jest na światowym poziomie, przy częstotliwości zegara 2.4 GHz w siedmionanometrowym procesie TSMC. Specyfikacja liczb całkowitych (Specint 2006) wynosi 8.25 na gigaherc, a SpecFp2006 to 10.2 na gigaherc, co jest najbardziej znaną wydajnością SPEC CPU® 2006 z dwupoziomową konstrukcją pamięci podręcznej. W późniejszym terminie dostarczone zostaną modele AX66, AX63 i AX67.

Kolejnym obszarem, w który firma Andes poczyniła znaczne inwestycje, są wysokowydajne procesory IP RISC-V klasy motoryzacyjnej. Według The SHD Group przewiduje się, że penetracja układów SoC RISC-V w projektach motoryzacyjnych osiągnie 21.4% do 2030 r. „Raport rynkowy RISC-V: prognozy zastosowań w heterogenicznym świecie”. Firma Andes opracowała produkty zgodne z bezpieczeństwem funkcjonalnym, w tym N25F-SE, pierwszy na świecie procesor IP w pełni zgodny z normą ISO 26262 RISC-V; D25F-SE, który obsługuje instrukcje rozszerzenia DSP; oraz procesory serii 45-SE, które spełniają najwyższy poziom ASIL, funkcja ASIL D. ACE zostanie ulepszona w celu dodania obsługi procesorów serii 45.

Dzięki popytowi, jakiego doświadczyli produkty Andes RISC-V, firma w dalszym ciągu utrzymuje rentowność i szybko się rozwija. W latach 2021–2023 przychody Andów wykazały prawie 30% wzrost. Było to napędzane przez ponad 300 licencjobiorców komercyjnych i ponad 600 podpisanych umów licencyjnych z rozproszonymi geograficznie klientami na Tajwanie, w Chinach, Korei, Japonii, Europie i USA. W tym samym okresie zatrudnienie w firmie na całym świecie wzrosło o prawie 70%.

Wnioski

W epoce charakteryzującej się szybką ewolucją technologiczną, Andes Technology Corp. stoi na czele innowacji na rynku procesorów IP RISC-V. Od pionierskiej emisji zagranicznych kwitów depozytowych (GDR) po przełomowe postępy w architekturze RISC-V, Andes Technology stale na nowo definiuje standardy branżowe i kształtuje przyszłość informatyki. Ponieważ zapotrzebowanie na wydajne i wydajne rozwiązania obliczeniowe stale rośnie, Andes Technology w dalszym ciągu angażuje się w dostarczanie niezrównanych rozwiązań RISC-V, aby napędzać transformacyjne zmiany w globalnym krajobrazie technologicznym.

Przeczytaj także:

WEBINAR NA ŻYWO: Architektura zestawu instrukcji RISC-V: zwiększanie mocy obliczeniowej

Udostępnij ten post przez:

- Dystrybucja treści i PR oparta na SEO. Uzyskaj wzmocnienie już dziś.

- PlatoData.Network Pionowe generatywne AI. Wzmocnij się. Dostęp tutaj.

- PlatoAiStream. Inteligencja Web3. Wiedza wzmocniona. Dostęp tutaj.

- PlatonESG. Węgiel Czysta technologia, Energia, Środowisko, Słoneczny, Gospodarowanie odpadami. Dostęp tutaj.

- Platon Zdrowie. Inteligencja w zakresie biotechnologii i badań klinicznych. Dostęp tutaj.

- Źródło: https://semiwiki.com/ip/343097-andes-technology-pioneering-the-future-of-risc-v-cpu-ip/