Under GOMACTech konferanse holdt i South Carolina forrige uke hadde jeg en Zoom-samtale med Deepak Shankar, grunnlegger og VP Technology hos Mirabilis Design Inc. for å stille spørsmål og se en live demo av VisualSim – en modellerings-, simulerings-, utforsknings- og samarbeidsplattform for å utvikle elektronikk og SoCs. Det som gjør VisualSim så særegen er at den leveres med rundt 500 høynivå IP-blokker klare til bruk, inkludert 35 ARM-prosessorer, rundt 100 prosessorer og over 30 forskjellige sammenkoblinger. Brukere av VisualSim kobler raskt disse IP-blokkene sammen visuelt for å lage systemene sine, komplett med nettverk. En bildesigner kan modellere hele nettverket, inkludert 5G-kommunikasjon, Ethernet, SDA og OTA-oppdateringer med VisualSim.

En høynivåmodell gir raskest mulig arkitektonisk utforskning og arkitektoniske avveininger, langt før implementeringen til og med begynner med RTL-kode. Du kan modellere komplekse aktiviteter som en buss, minner og til og med cache, og måle ting som ende-til-ende forsinkelser og latens. Ingeniører kan måle hva deres cachetreff/miss-forhold er, og hva som skjer med forespørsler til L2-cacher. Alle de populære nettverksprotokollene er modellert: AXI, CHI, CMN600, Arteris NOC, UCIe, etc.

Med denne modelleringstilnærmingen kan en arkitekt modellere en SoC, komplett fly- eller bilsystem, og deretter begynne å måle ytelsen for å se om den oppfyller kravene. VisualSim er en multi-domene simulator som kan integrere analog, programvare, strømsystemer, digital og nettverk i en enkelt modell.

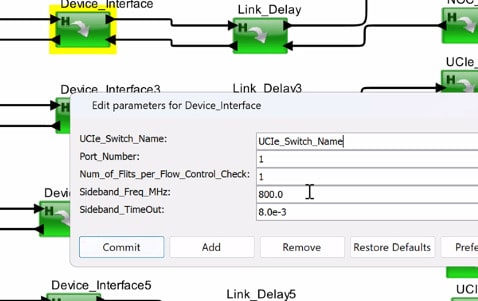

For live-demoen viste Deepak meg en brikkebasert design som hadde separate brikker for DSP, GPU, AI-prosessor og CPU, alle koblet sammen ved hjelp av UCIe, og hver IP-blokk ble parameterisert for å tillate tilpasning og utforskning.

Ved å presse inn i UCIe-blokken var det en IP kalt en UCIe-svitsj, og en bruker kan tilpasse denne blokken med fem parametere, alle på et høyt nivå.

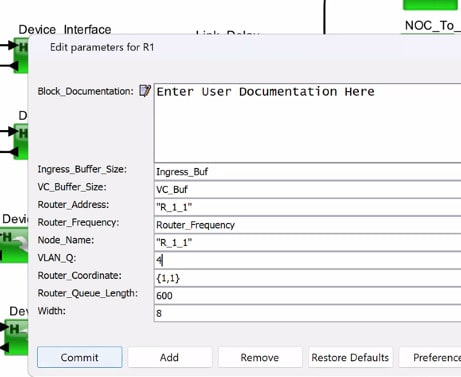

En ruter IP-blokk hadde 10 parametere for tilpasning.

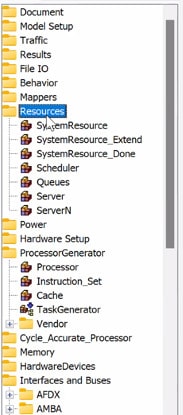

For å finne hver IP-blokk var det en rullebar liste på venstre side av GUI, med hver familie av IP i biblioteket. I løpet av sekunder kan du bla gjennom, velge og begynne å tilpasse en IP.

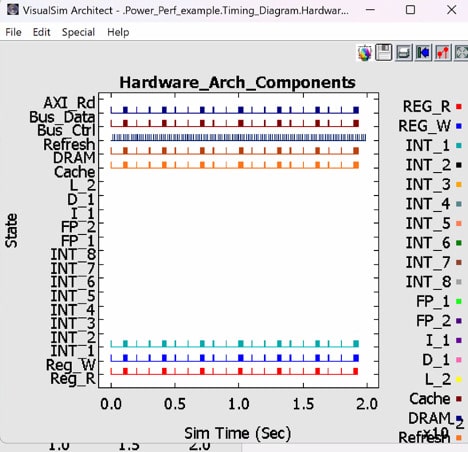

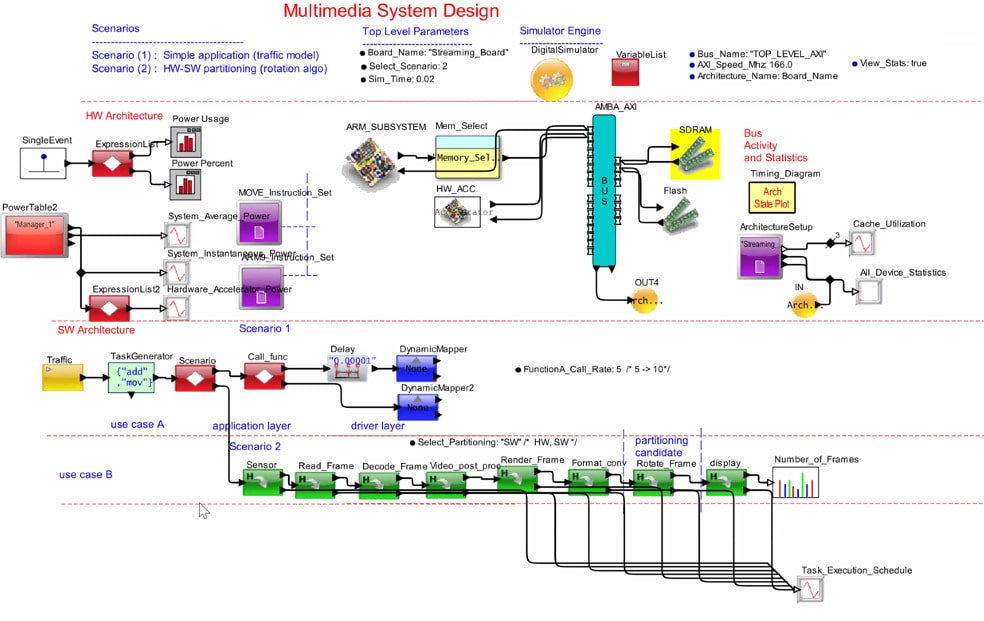

I VisualSim kobler du til hver IP i dataflyten, og holder deg på et høyt nivå. Den neste live-demoen var for et multimediasystemdesign, og å simulere 20 ms tok det omtrent 15 sekunder med veggtid på en bærbar datamaskin. Mens simuleringen kjører kan du se systemytelsen som øyeblikkelig kraft, måle pipelineutnyttelse, hurtigbufferutnyttelse, minnebruk og til og med se et tidsdiagram. Denne sanntidssimuleringen utløste 7.5 millioner hendelser, og kunden bygde denne modellen på under 2 uker, som inkluderte hele SoC.

Et annet kundeeksempel som Deepak nevnte inkluderer 45 mastere og ble fullført på omtrent 4 uker, fullstendig testet.

Du kan se inn i hvilken som helst av IP-blokkene og analysere beregninger som bestått/ikke bestått, og deretter forstå hvorfor det mislyktes. Det er til og med en AI-motor som hjelper til med å analysere data mer effektivt, som å finne et bufferoverløp som forårsaket en feil. Mens modellen din kjører, fanges det analyser for å hjelpe med å måle systemytelse og identifisere arkitektoniske flaskehalser.

VisualSim oppdateres to ganger per år, og så er det patchoppdateringer for når nye IP-blokker legges til. En arkitekt definerer krav i en Excel-fil, med beregninger som latensgrenser og bufferbelegg.

Brukere av VisualSim kan definere rekkevidden av nyttelaststørrelse i form av byte, hastighetsområder og foretrukne verdier. Systemmodellen din kan sveipes over kombinasjonene for å finne det beste settet med parametere. Simulatoren forstår til og med hvordan man utforsker min, maks og foretrukne verdier. Du får definere hvilke systemparametere som skal utforskes. En multimediesystemdemo ble vist neste gang og deretter simulert live.

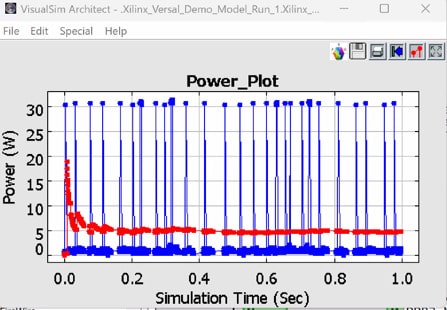

For en FPGA-blokk velger du leverandør og delenummer, og så kan du se latensen for hver oppgave og kanalstatistikken til NOC etter at en simulering er kjørt. Et kraftdiagram ble vist for 1 sekunds drift ved bruk av Xilinx Versal-deler.

Alle live-demoene ble kjørt på en Windows-bærbar datamaskin. Andre støttede operativsystemer er: Unix, Mac. Å kjøre VisualSim krever minimal HW-infrastruktur, fordi modellene er på høyt nivå.

VisualSim-brukere mottar over 500 eksempler som er forhåndsbygd for å hjelpe deg i gang raskt, som et komplett kommunikasjonssystem med antenne, transceiver, FPGA med basebånd og Ethernet-grensesnitt. Systemarkitekter som bruker VisualSim kan samarbeide med alle spesialister på lavt nivå, som RTL-designere.

Avveininger på systemnivå kan modelleres og evalueres, som:

- Endring fra 64-QAM til QPSK-modulasjon

- Raskere til tregere prosessor

- Endring av Ethernet-spesifikasjoner

Hvis du starter med VisualSim for å modellere, implementere og deretter måle, forvent å se 95 % nøyaktighet sammenlignet med RTL-implementeringsresultater. Løftet om å bruke høynivåmodeller er å eliminere ytelsesproblemer før implementering eller integrasjon. Det er egentlig ingen koding som kreves for en hel systemmodell.

Mirabilis har 65 kunder over hele verden så langt og rundt 250 prosjekter fullført. Noen av de kjente kundene inkluderer: NASA, Samsung, Qualcomm, Broadcom, GM, Boeing, HP, Imagination, Raytheon, AMD, Northrup Grumman.

Oppsummering

I gamle dager kan en systemdesigner ha tegnet ideene sine på en serviett mens de spiste på en restaurant, og deretter gå tilbake til jobben og flette sammen noen Excel-regneark med mystiske ligninger for å lage en modell. I dag er det et nytt valg, og det er å gi VisualSim fra Mirabilis et forsøk. Du kan nå modellere et helt system på bare noen få uker, sammen med å gjøre arkitektoniske avveininger mens du kjører faktiske simuleringer, alt før du går inn i detaljerte implementeringsdetaljer.

Relaterte blogger

Del dette innlegget via:

- SEO-drevet innhold og PR-distribusjon. Bli forsterket i dag.

- PlatoData.Network Vertical Generative Ai. Styrk deg selv. Tilgang her.

- PlatoAiStream. Web3 Intelligence. Kunnskap forsterket. Tilgang her.

- PlatoESG. Karbon, CleanTech, Energi, Miljø, Solenergi, Avfallshåndtering. Tilgang her.

- PlatoHelse. Bioteknologisk og klinisk etterretning. Tilgang her.

- kilde: https://semiwiki.com/ip/343387-a-modeling-simulation-exploration-and-collaborative-platform-to-develop-electronics-and-socs/