Det er mye diskusjon om å fjerne hindringer for innovasjon i disse dager. Halvledersystemer er kjernen i å låse opp mange former for teknisk innovasjon, hvis bare vi kunne ta tak i problemer som nedbremsing av Moores lov, reduksjon av strømforbruk, forbedring av sikkerhet og pålitelighet og så videre. Men det er en annen ganske betydelig barriere som er temaet for dette innlegget. Det er den dramatiske forskjellen mellom prosessor- og minneytelse. Mens systemer med CPUer og GPUer leverer utrolige ytelsesnivåer, halter minnene som administrerer kritiske data for disse systemene betydelig. Dette er minneveggproblemet, og jeg vil gjerne undersøke hvordan Arteris slipper løs innovasjon ved å bryte ned minnevegg.

Hva er minneveggen?

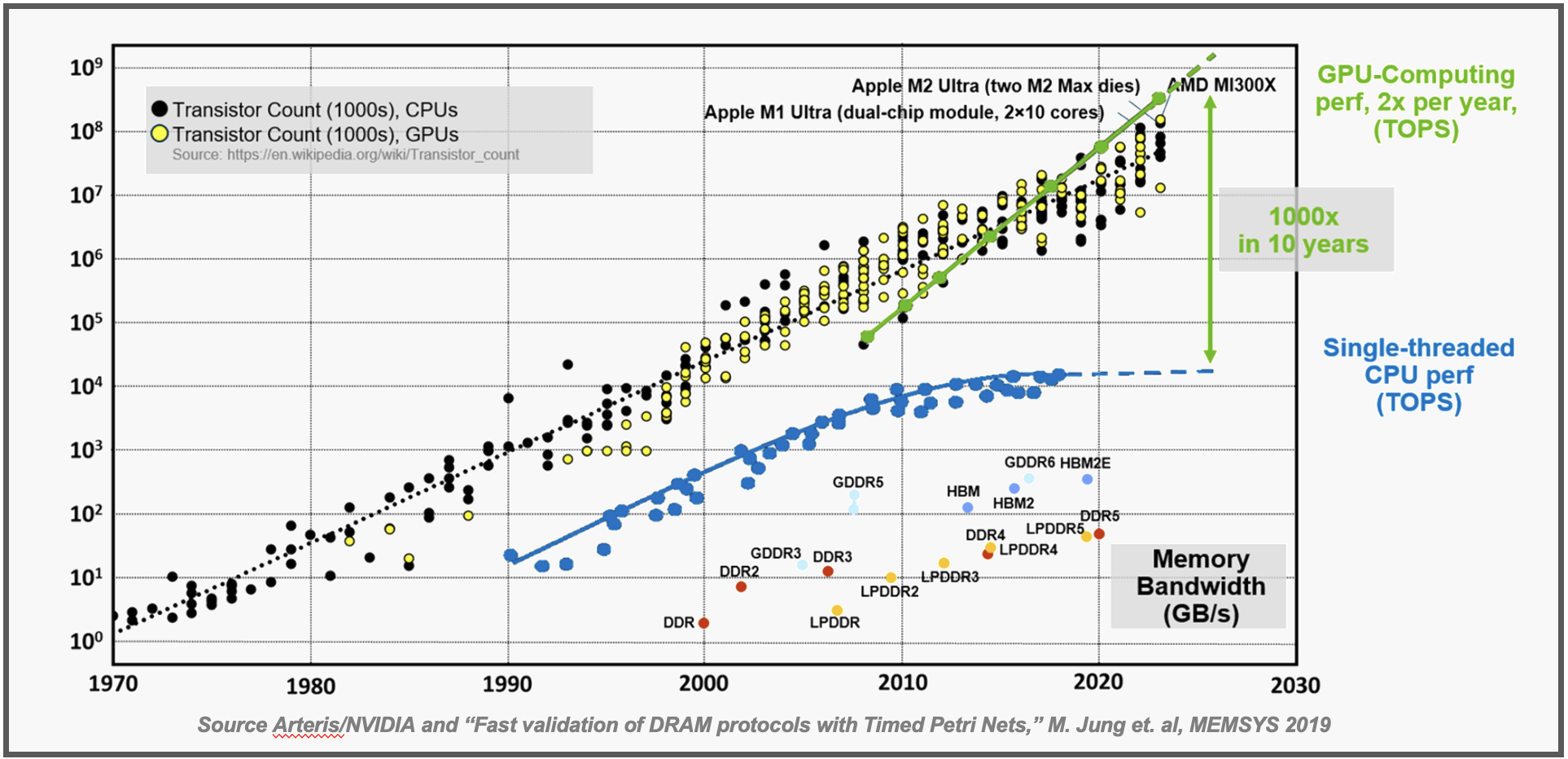

Grafikken øverst i dette innlegget illustrerer minneveggproblemet. Du kan se den jevne økningen i ytelsen til entrådede CPUer vist med den blå linjen. Den grønne linjen viser den eksponentielle økningen i ytelse som legges til av klynger av GPUer. Ytelsesøkningen til GPUer vs. CPUer er estimert til å være 100X på 10 år – en forbløffende statistikk. Som en sidenotat kan du se at transistoren teller for både CPU-er og GPU-er klynger seg rundt en lignende rett linje. GPU-ytelse leveres ved å utføre færre oppgaver mye raskere i motsetning til å kaste flere transistorer på problemet.

Mange systemer i dag er en kombinasjon av en rekke CPUer som utfører brede administrasjonsoppgaver med et stort antall GPUer som utfører spesifikke oppgaver, ofte relatert til AI. Kombinasjonen gir den fantastiske gjennomstrømningen vi ser i mange produkter. Det er en mørk side ved denne harmoniske arkitekturen som er avbildet nederst på diagrammet. Her ser vi ytelsesdataene for de ulike minneteknologiene som leverer all informasjonen for disse systemene å behandle. Som du kan se, er levert ytelse vesentlig lavere enn CPU-ene og GPUene som er avhengige av disse minnesystemene.

Dette er problemet med minneveggen. La oss utforske den unike måten Arteris løser dette problemet på.

Arteris-tilnærmingen – en svært konfigurerbar Cache Coherent NoC

En godt akseptert tilnærming til å håndtere langsommere minnetilgangshastighet er å forhåndshente de nødvendige dataene og lagre dem i en lokal hurtigbuffer. Å få tilgang til data på denne måten er langt raskere – noen få CPU-sykluser kontra over 100 CPU-sykluser. Det er en flott tilnærming, men det kan være skremmende å implementere all programvaren og maskinvaren som kreves for å få tilgang til minnet fra hurtigbufferen og sikre at riktig data er på rett sted til rett tid og konsistent på tvers av alle cacher. Systemer som effektivt leverer denne løsningen kalles cache sammenhengende, og det er ikke lett å nå dette målet. En koherensimplementering som kun er programvare, kan for eksempel konsumere så mye som ~25 % av alle CPU-sykluser i systemet, og er svært vanskelig å feilsøke. SoC-designere velger ofte cache-koherente NoC-maskinvareløsninger i stedet, som er transparente for programvaren som kjører på systemet.

Nylig hadde jeg en mulighet til å snakke med Andy Nightingale, visepresident for produktledelse og markedsføring hos Arteris. Andy gjorde en god jobb med å forklare utfordringene med å implementere cache-koherente systemer og den unike løsningen Arteris har utviklet for å takle disse utfordringene.

Det viser seg at utviklingen av en pålitelig og strømeffektiv cache-koherent arkitektur berører mange maskinvare- og programvareaspekter ved systemdesign. Det kan være ganske vanskelig å få alt til å fungere pålitelig, effektivt og nå de nødvendige PPA-målene. Andy estimerte at alt dette arbeidet kunne kreve 50 ingeniørår per prosjekt. Det er mye tid og kostnader.

Den gode nyheten er at Arteris har betydelige ferdigheter på dette området, og selskapet har skapt en komplett cache-koherent arkitektur i et av sine nettverk-på-brikke (NoC)-produkter. Andy beskrev Ncore, en fullstendig cache-koherent NoC som tilbys av Arteris. Håndtering av minnetilgang passer godt inn i den generelle nettverk-på-brikke-arkitekturen som Arteris er kjent for. Ncore administrerer den cache-koherente delen av SoC-en gjennomsiktig for programvare – og frigjør systemdesigneren til å fokusere på utfordringene på høyere nivå knyttet til å få CPU-en og alle de GPU-ene til å utføre oppgaven.

Andy kjørte ned en liste over Ncore-funksjoner som var betydelig:

- Produktivt: Koble sammen flere prosesseringselementer, inkludert Arm og RISC-V, for maksimal ingeniørproduktivitet og akselerasjon fra tid til marked, og sparer 50+ årsverk per prosjekt.

- Konfigurerbar: Skalerbar fra heterogene til mesh-topologier, støtter CHI-E, CHI-B og ACE-koherente, samt ACE-Lite IO-koherente grensesnitt. Ncore gjør det også mulig for AXI ikke-koherente agenter å fungere som IO-koherente agenter.

- Økosystemintegrering: Forhåndsvalidert med de nyeste Arm v9 bilkjernene, og leverer på et tidligere annonsert partnerskap med Arm.

- Safe: Støtter ASIL B til ASIL D-kravene for bilsikkerhetsapplikasjoner, og er ISO26262-sertifisert.

- Effektiv: Mindre dyseareal, lavere effekt og høyere ytelse ved design, sammenlignet med andre kommersielle alternativer.

- Markeder: Egnet for bil-, industri-, bedriftsdatabehandling, forbruker- og IoT SoC-løsninger.

Andy detaljerte noen av fordelene som er oppnådd med en SoC-design for forbrukere. Disse inkluderte strømlinjeformet gulvplanlegging takket være den svært distribuerte arkitekturen, som fremmer effektiv ressursutnyttelse. Arteris høyytelses-sammenkobling med høybåndbredde og lav latensstoff sørget for sømløs dataoverføring og økte den generelle systemytelsen.

Ved å grave litt dypere gir Ncore også sanntidssynlighet inn i sammenkoblingsstrukturen med sporing på transaksjonsnivå, ytelsesovervåking og feildeteksjon og korrigering. Alle disse funksjonene letter enkel feilsøking og overlegen produktkvalitet. Den omfattende økosystemstøtten og kompatibiliteten med industristandardgrensesnitt som AMBA, letter også enklere integrasjon med tredjepartskomponenter og EDA-verktøy.

Dette var en veldig nyttig diskusjon. Det ser ut til at Arteris har redusert kostnadene for implementering av cache-koherente arkitekturer dramatisk.

Å lære mer

Jeg nevnte noen detaljer om arbeidet Arteris gjør med Arm. Tror ikke det er den eneste partneren selskapet jobber med. Arteris har blitt kalt Sveits for system IP. Selskapet har også betydelig arbeid med RISC-V-fellesskapet som detaljert i SemiWiki-innlegget her.

Arteris annonserte nylig utvidelse av sitt Ncore-produkt. Du kan lese hvordan Arteris utvider Ncore cache coherent interconnect IP for å akselerere ledende elektronikkdesign her. I utgivelsen sier Leonid Smolyansky, Ph.D. SVP SoC Architecture, Security & Safety hos Mobileye ga disse kommentarene:

"Vi har jobbet med Arteris nettverk-på-brikke-teknologi siden 2010, og brukt den i vår avanserte autonome kjøring og sjåførassistanse-teknologier. Vi er glade for at Arteris har tatt med seg sin betydelige ingeniørkompetanse for å hjelpe til med å løse problemene med feiltoleranse og pålitelig SoC-design."

Det er også en kort (litt over ett minutt) video som forklarer utfordringene som Ncore adresserer. Jeg fant videoen ganske informativ.

Hvis du trenger forbedret ytelse for ditt neste design, bør du definitivt ta en nærmere titt på de cache-sammenhengende løsningene som tilbys av Arteris. Du kan lær mer om Ncore her. Og det er hvordan Arteris er å slippe løs innovasjon ved å bryte ned minnemuren.

Del dette innlegget via:

- SEO-drevet innhold og PR-distribusjon. Bli forsterket i dag.

- PlatoData.Network Vertical Generative Ai. Styrk deg selv. Tilgang her.

- PlatoAiStream. Web3 Intelligence. Kunnskap forsterket. Tilgang her.

- PlatoESG. Karbon, CleanTech, Energi, Miljø, Solenergi, Avfallshåndtering. Tilgang her.

- PlatoHelse. Bioteknologisk og klinisk etterretning. Tilgang her.

- kilde: https://semiwiki.com/ip/arteris/342991-arteris-is-unleashing-innovation-by-breaking-down-the-memory-wall/