Atiq Raza, bekend in de halfgeleiderindustrie, heeft opgemerkt dat "er geen simpele chips onder de 16nm zullen zijn". Waarmee hij bedoelde dat alleen complexe en dus hoogwaardige SoC's de kosten van diep submicronontwerp rechtvaardigen. Het wordt steeds moeilijker om PPA-doelen te behalen voor dergelijke ontwerpen, vooral nu bij 7nm en 5nm. Plaats- en routetechnologieën en teams zijn niet het probleem - ze zijn net zo capabel als altijd. Het probleem zit hem in de steeds sterkere koppeling tussen architectonisch en logisch ontwerp en fysieke uitvoering. Ontwerp/fysieke koppeling op blokniveau wordt goed begrepen en is aangepakt door middel van fysieke synthese. Onder 16nm is het echter heel goed mogelijk om geldige SoC-architecturen te ontwerpen die steeds moeilijker te plaatsen en te routeren zijn, wat leidt tot projectvertragingen of zelfs SoC-projectannuleringen als gevolg van gemiste marktvensters.

Waarom werd dit zo moeilijk?

Fysieke implementatie is uiteindelijk een optimalisatieprobleem. Het vinden van een plaatsing van verbindingscomponenten en verbindingen tussen blokken in de plattegrond die optimale prestaties en oppervlakte zal opleveren. Terwijl het ook voldoet aan een reeks beperkingen en voldoet aan de doelspecificaties binnen een redelijk schema. Het eerste doel is altijd mogelijk als u bereid bent een compromis te sluiten over wat u bedoelt met 'optimaal'. Het tweede doel hangt sterk af van waar optimalisatie begint en hoeveel tijd elke nieuwe iteratie kost om een beter resultaat te vinden. Begin te ver weg van een punt dat de vereiste specificaties zal opleveren, of het duurt te lang om de stappen te doorlopen om dat punt te vinden en het product zal problemen krijgen.

Dit was altijd al het geval, maar SoC-integraties in geavanceerde processen worden steeds groter. Honderd blokken en tienduizenden verbindingen vergroten de grootte van de optimalisatieruimte. Meer klok- en krachtdomeinen voegen meer dimensies en beperkingen toe. Veiligheidseisen voegen logica en meer beperkingen toe, wat direct van invloed is op de implementatie. Samenhangende netwerken voegen nog meer beperkingen toe, aangezien grote latenties de gegarandeerde prestaties over coherente domeinen naar beneden halen. In deze uitbreidende, veeldimensionale en complexe beperkte optimalisatieruimte met onvoorspelbare contouren is het niet verwonderlijk dat afsluiting steeds moeilijker te vinden is.

Een aanpak met een veel lager risico zou beginnen en leiden op een punt dat redelijk dicht bij een goede oplossing ligt, zonder afhankelijk te zijn van lange iteratiecycli tussen ontwerp en implementatie.

Fysiek bewust NoC-ontwerp

De integratie-interconnectie in een SoC vormt de kern van dit probleem. Lange draden zorgen voor lange vertragingen die timingsluiting teniet doen. Veel draden die door gemeenschappelijke kanalen lopen, creëren congestie die het chipgebied dwingt uit te breiden om congestie te verminderen. Crossbar-interconnecties met hun intrinsiek overbelaste connectiviteit werden om deze reden lang geleden vervangen door Network-on-Chip-interconnects (NoC). NoC-interconnects gebruiken netwerktopologieën die congestie gemakkelijker kunnen beheren, netwerkplaatsing en routering door kanalen en witruimte in een plattegrond kunnen leiden.

Maar toch moet de topologie van de NoC (of meerdere NoC's in een groot ontwerp) voldoen aan timingdoelen; het NoC-ontwerp moet fysiek bewust zijn. Al die eerder genoemde extra beperkingen en dimensies versterken deze uitdaging nog meer.

NoC-ontwerp begint als een logisch doel, om alle IP-communicatiepoorten te verbinden zoals gedefinieerd door de functionele productspecificatie, terwijl een beoogde servicekwaliteit wordt gegarandeerd. En het behalen van doelstellingen op het gebied van vermogen, veiligheid en beveiliging. Nu is het duidelijk dat we aan deze logische doelstellingen een component van fysiek bewustzijn moeten toevoegen. Inschatting van de timing tussen IP-eindpunten en congestie op basis van een plattegrond in vroege stadia van RTL-ontwikkeling, om in latere stadia te verfijnen met een nauwkeurigere plattegrond.

Met een dergelijke mogelijkheid zou een NoC-ontwerper heel snel meerdere proeven kunnen uitvoeren, waarbij het ontwerp naar behoefte opnieuw kan worden gepartitioneerd, om een goed startpunt te bieden voor het plaats- en routeteam. Dat team zou dan hun magie gebruiken om de schatting van het fysieke bewustzijn volledig te optimaliseren. Er zeker van zijn dat het optimum waarnaar ze zoeken redelijk dicht bij dat startpunt ligt. Dat ze het ontwerp niet hoeven terug te sturen voor herstructurering en hersynthese.

Extra mogelijkheden

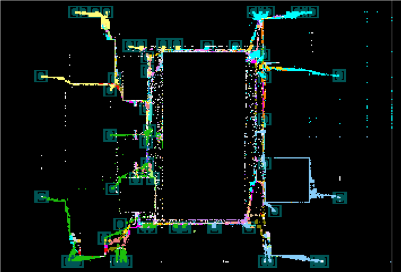

Fysiek bewust NoC-ontwerp kan extra voordelen bieden. Door plattegrondinformatie in de ontwerpfase op te nemen, kan een NoC-ontwerper een betere NoC bouwen. Door latenties, plaatsingen en kanaalgebruik te begrijpen terwijl ze nog steeds de NoC RTL bouwen, kunnen ze mogelijkheden realiseren om een andere topologie te gebruiken (zie de topologie hierboven als een voorbeeld). Misschien kunnen ze smallere of langere verbindingen gebruiken op latentie-ongevoelige paden, waardoor congestie wordt vermeden zonder het gebied uit te breiden.

Uiteindelijk kan fysiek bewustzijn wijzigingen in de plattegrond suggereren die een nog betere implementatie kunnen opleveren dan aanvankelijk werd gedacht.

Conclusie

Charlie Janac, CEO van Arteris, benadrukte dit punt in een recente SemiWiki-podcast:

Fysiek bewustzijn is nuttig voor back-end fysieke lay-outteams om de bedoeling van de front-end architectuur en RTL-ontwikkelingsteams te begrijpen. Het hebben van een startpunt dat is gevalideerd voor schendingen van latentie en timing kan het fysieke ontwerp aanzienlijk versnellen en de resultaten van SoC-projecten verbeteren. Dit is vooral belangrijk in scenario's waarin de architectuur wordt gedaan door het ene bedrijf en de lay-out door een ander. Dergelijke gevallen doen zich vaak voor tussen systeemhuizen zoals auto-OEM's en hun ontwerppartners voor halfgeleiders. Lichamelijk bewustzijn is overal gunstig. Het is een win-winsituatie voor alle betrokkenen.

Commerciële interconnectieaanbieders moeten een stap verder gaan om hun NoC IP direct fysiek bewust te maken. Dit wordt een minimumvereiste voor NoC-ontwerp in geavanceerde technologieën. Misschien wil je geven slagader een telefoontje, om te begrijpen hoe ze denken over deze behoefte.

Deel dit bericht via:

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- Platoblockchain. Web3 Metaverse Intelligentie. Kennis versterkt. Toegang hier.

- Bron: https://semiwiki.com/ip/323847-taming-physical-closure-below-16nm/