빠르게 변화하는 데이터 통신 세계에서 고속 데이터 전송에 대한 욕구는 데이터 기밀성과 무결성에 대한 요구 증가를 동반합니다. 널리 사용되는 연결용 PCIe 인터페이스 표준은 데이터 전송 속도를 증가시켰을 뿐만 아니라 IDE(Integrity and Data Encryption) 보안 옵션도 도입했습니다. PCIe에 IDE 기능을 도입하면 데이터를 암호화하여 무결성을 유지하면서 더 높은 데이터 대역폭을 처리할 수 있습니다.

Siemens EDA는 PCIe 및 기본 소프트웨어 스택의 IDE 트랜잭션 계층 패킷(TLP)에서 사용되는 암호화 흐름에 대해 설명하는 백서를 게시했습니다. 이 백서에서는 링크 간 연결 및 스위치를 통해 연결된 장치를 포함하여 송신기에서 수신기로 전송되는 TLP에 대한 디지털 공격에 대해 IDE가 어떻게 보안을 보장하는지 설명합니다. TLP는 IDE 키 관리 중에 교환된 키를 사용하여 암호화됩니다. 또한 백서는 DOE(Data Object Exchange), CMA(Component Measurement and Authentication), SPDM(Security Protocol and Data Model) 등 IDE에서 사용되는 기본 프로토콜에 대해 설명합니다.

DOE(데이터 개체 교환)

PCIe의 DOE(데이터 개체 교환)는 장치 간에 다양한 유형의 데이터 개체를 전송하기 위해 도입된 확장 기능입니다. 각 공급업체는 PCI-SIG에서 할당한 공급업체 ID로 식별되는 특정 데이터 개체를 정의할 수 있습니다. 데이터는 한 번에 하나의 더블 워드(32비트) 데이터 개체로 전송되며 PCIe의 구성 쓰기 트랜잭션을 통해 패킷을 형성합니다. 송신 장치는 데이터 객체의 전체 길이를 보낸 후 DOE go 비트를 설정합니다. 수신 장치는 데이터를 소비하고 응답을 형성하기 시작합니다. 응답이 준비되면 수신 장치는 구성 공간에서 DOE 데이터 개체 준비 비트를 설정합니다. 송신기는 데이터 개체 준비 비트가 높을 때까지 한 번에 하나의 더블 워드 응답을 읽습니다. 이 프로세스를 통해 한 장치에서 다른 장치로 데이터를 전송할 수 있습니다.

구성 요소 측정 및 인증(CMA)

PCIe의 구성 요소 측정 및 인증(CMA) 기능은 기본 SPDM(보안 프로토콜 및 데이터 모델) 프로토콜에 의존합니다. CMA는 보안 연결 설정을 위해 DOE 기능을 활용하여 패킷을 전송합니다. CMA/SPDM 프레임워크 내에서 연결된 장치의 진위 여부는 디지털 서명 및 공개 키 암호화를 사용하여 확인됩니다. 이 프로세스는 연결과 관련된 장치가 정품이고 신뢰할 수 있는지 확인합니다. 연결된 장치의 인증이 설정되면 요청자와 응답자 간에 보안 연결이 형성됩니다. 그런 다음 보안 CMA/SPDM 프로토콜을 사용하여 데이터 개체를 안전하게 전송합니다. 데이터 개체는 보안 연결을 설정하는 동안 사용된 협상된 알고리즘을 사용하여 전송됩니다.

IDE 키 관리

IDE 키 관리는 IDE TLP를 암호화하는 데 사용할 키를 교환하는 데 사용됩니다. 이 프로세스에는 TLP 전송 및 수신 모두에 대해 하위 스트림별로 키를 교환하는 작업이 포함됩니다. IDE 접두사에서 K 비트로 식별되는 두 세트의 키가 있을 수 있으며 각 세트에는 Tx 및 Rx 방향에 대한 서로 다른 키가 포함되어 있습니다. IDE 키 관리 프로세스에는 각각 개체 ID 필드로 식별되는 XNUMX가지 유형의 패킷이 있습니다. 전체 세부 사항이 설명되어 있습니다. 백서에서.

무결성 및 데이터 암호화(IDE)

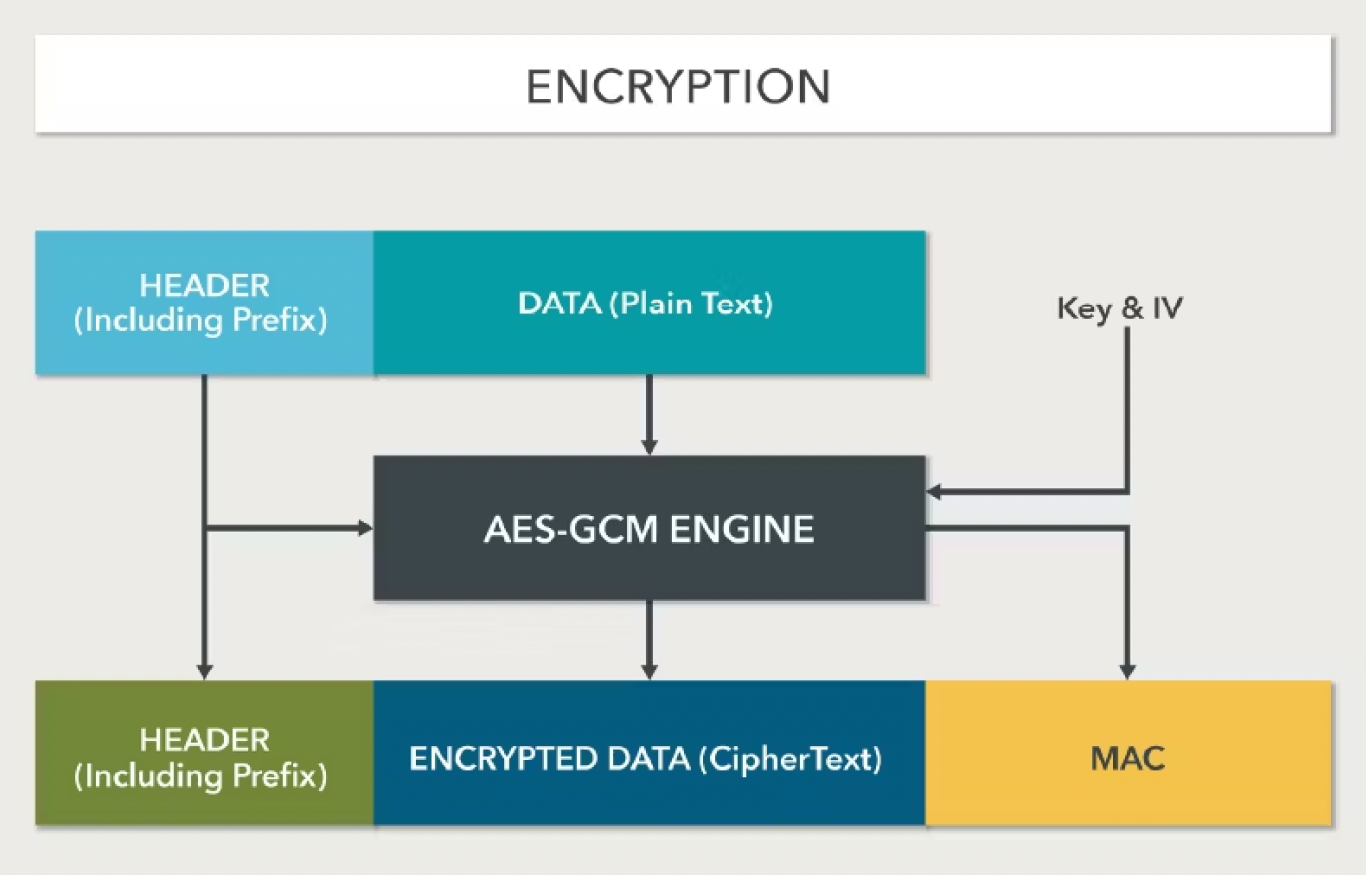

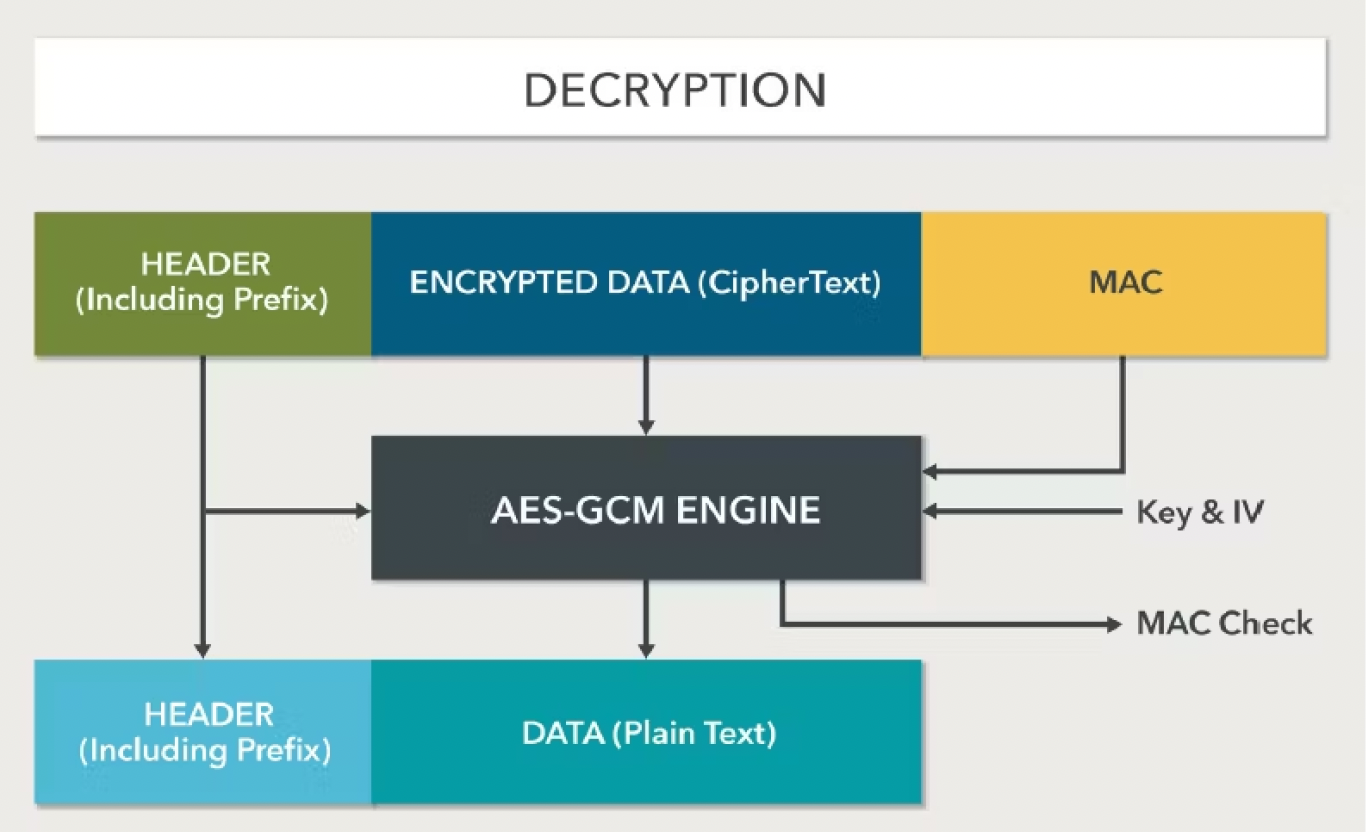

데이터 전송 보안의 목표는 무단 액세스를 방지할 뿐만 아니라 변조를 방지하는 것입니다. 암호화를 사용하더라도 데이터 무결성을 확인하지 않는 한 공격자가 수신자 모르게 데이터를 수정할 수 있습니다. IDE 메커니즘의 메시지 인증 코드(MAC) 기능은 데이터 무결성 검사를 가능하게 합니다. 보안 상태는 CMA/SPDM을 사용한 보안 연결 설정, IDE 키 관리를 사용한 키 구성, IDE 활성화 비트 설정을 통한 IDE 활성화를 통해 달성됩니다. 백서 송수신 데이터 흐름과 키 및 초기화 벡터를 사용하는 AES-GCM(Advanced Encryption Standard-Galois/Counter Mode) 암호화/복호화 프로세스에 대해 자세히 설명합니다. MAC 검사를 기반으로 IDE 스트림은 보안 상태 또는 비보안 상태로 표시될 수 있습니다. 보안 상태가 손상되면 IDE 스트림이 보안 상태에서 비보안 상태로 전환될 수 있습니다.

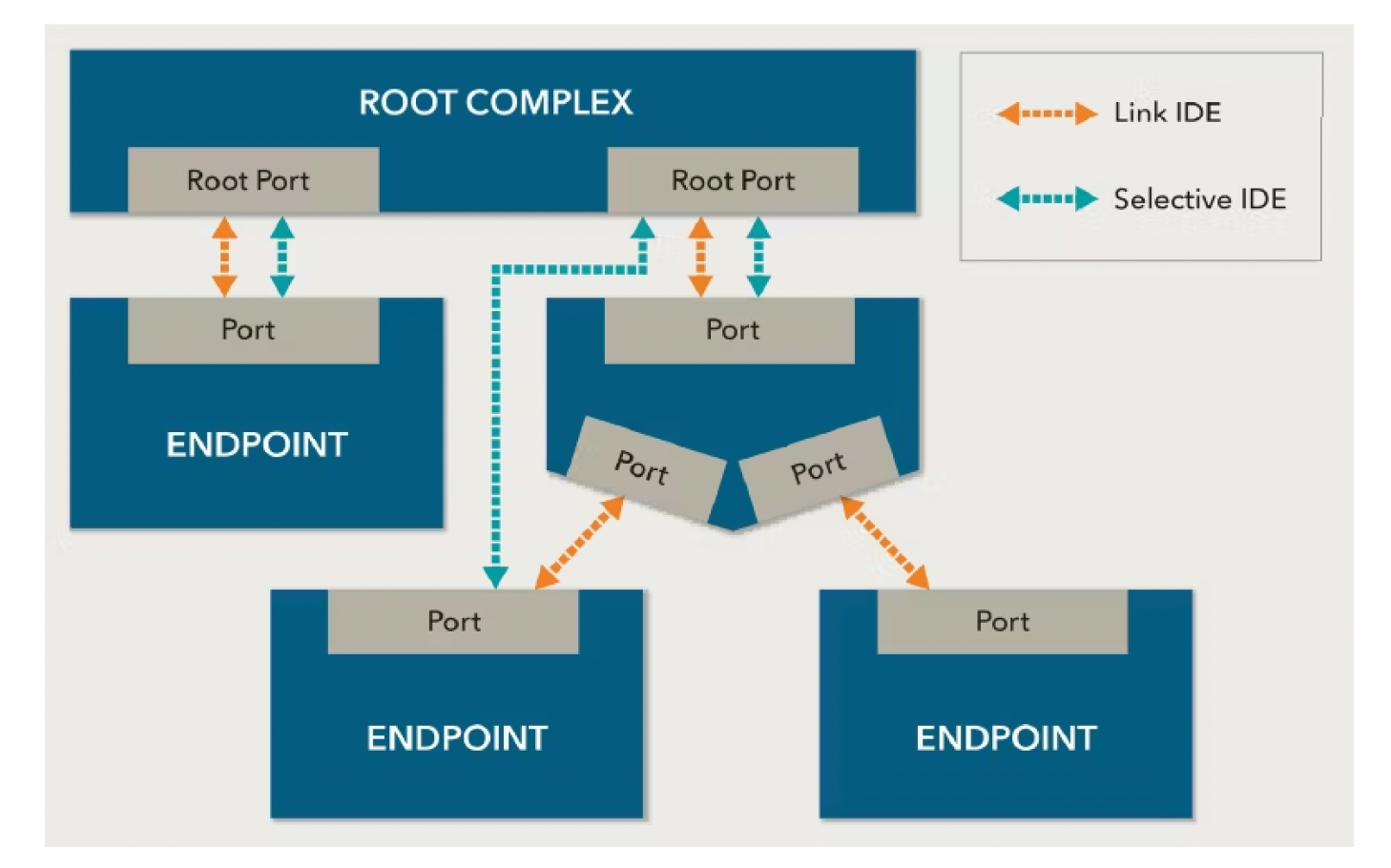

IDE 메커니즘은 또한 TLP 전송 보안에 유연성을 제공합니다. 두 포트 간의 IDE 스트림 설정은 Link IDE 또는 Selective IDE를 사용하여 연결하여 수행할 수 있습니다. 포트 사이에 스위치가 있는 경우 선택적 IDE를 사용하여 포트 간에 전송되는 패킷을 암호화합니다. 링크 IDE와 선택적 IDE는 직접 연결된 포트에 대해 독립적으로 또는 함께 작동할 수 있습니다.

Siemens EDA의 Questa VIP로 IDE 기능 검증

Siemens QVIP는 전체 IDE 기능 검증 프로세스를 지원하는 포괄적인 검증 솔루션 역할을 합니다. 여기에는 자극 생성, 어설션 확인, 오류 주입 기능 및 광범위한 시퀀스 라이브러리가 포함됩니다. 디버그 및 로그 기능의 존재는 검증 프로세스의 효율성과 효과를 더욱 향상시킵니다.

요약

이 백서는 또한 IDE TLP 접두사(M-비트, K-비트, T-비트 및 P-비트)와 이들이 제공하는 용도에 대해 자세히 설명합니다. 예를 들어, IDE 접두사에 M 비트가 있으면 MAC이 있는지 여부를 나타냅니다. 또한 이 백서에서는 처리량을 늘리기 위해 전송을 위해 여러 TLP를 단일 장치로 결합할 수 있는 TLP 집계에 대해서도 다룹니다.

백서 PCIe 기반 시스템의 데이터 무결성 및 보안 구현과 관련된 모든 사람에게 귀중한 자료가 될 것입니다.

또한 읽기 :

CDX를 통한 Chiplet 모델링 및 워크플로 표준화

Tessent SSN은 SoC ATPG의 상당한 테스트 시간 절약을 가능하게 합니다.

다음을 통해이 게시물 공유 :

- SEO 기반 콘텐츠 및 PR 배포. 오늘 증폭하십시오.

- PlatoAiStream. Web3 데이터 인텔리전스. 지식 증폭. 여기에서 액세스하십시오.

- 미래 만들기 w Adryenn Ashley. 여기에서 액세스하십시오.

- PREIPO®로 PRE-IPO 회사의 주식을 사고 팔 수 있습니다. 여기에서 액세스하십시오.

- 출처: https://semiwiki.com/ip/329897-securing-pcie-transaction-layer-packet-tlp-transfers-against-digital-attacks/