ב-13 בספטמבר 2021, Andes Technology Corporation הנפיק בהצלחה את הנפקת ה-GDR (תעודת פיקדון גלובלית) שלה בבורסת לוקסמבורג. באותה תקופה היא הפכה את האנדים לספקית ה-IP של המעבדים הבינלאומיים הציבוריים היחידים של RISC-V הוראות ארכיטקטורת (ISA) CPU. זה אפשר למשקיעים ברחבי העולם להשתתף בצמיחת האנדים שחזונו עבור RISC-V. הזרמת הון זו תניע את שאיפת האנדים להפוך למובילה בשוק ה-RISC-V המתפתח במהירות, בעל צמיחה גבוהה ופתוח. בשנת 2015, מתוך הכרה בפוטנציאל העצום של RISC-V ISA, Andes הפך לחבר מייסד וראשי ב-RISC-V International.

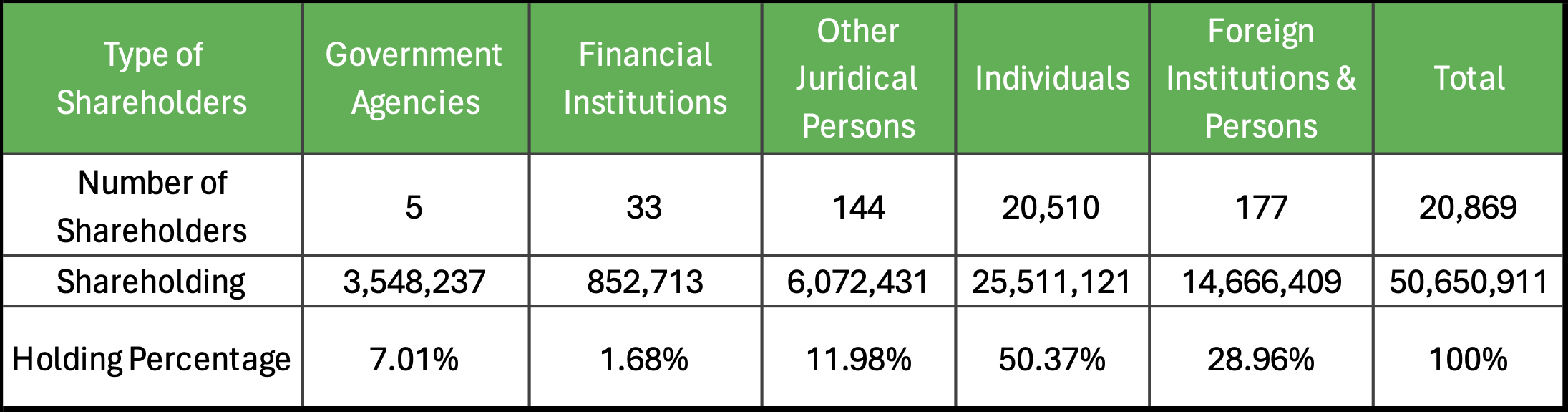

החל מ-2 באפריל, 2023; יחידה: מניות, %

ההשקעה השתלמה באופן משמעותי במיוחד מכיוון שהיא עלתה בקנה אחד עם אשרור הרחבת RISC-V Vector בנובמבר 2021. אירוע זה סימן נקודת מפנה בהתפתחות ארכיטקטורת ערכת ההוראות של RISC-V. הרחבה וקטורית RISC-V הגיעה בתקופה שבה מחשוב מרכזי הנתונים הפך מעיבוד למטרות כלליות לעיבוד בינה מלאכותית, המטפל במערכות נתונים גדולות במיוחד. עיבוד וקטור מצטיין בעיבוד יעיל של מערכים גדולים או נתונים מובנים. לעיבוד וקטור יש פוטנציאל להפוך את RISC-V ל-ISA הגדול הבא בעולם.

הארכיטקטורה המקבילה ביותר של מעבד וקטור מפחיתה זמן חביון ותקורה. זה משיג יעילות אנרגטית טובה יותר על ידי ניצול מקסימלי של משאבי המעבד ומזעור מחזורי סרק, ובכך מימוש ביצועים גבוהים יותר לוואט. יתר על כן, החומרה ליישום יחידות עיבוד וקטור RISC-V (VPUs) ואוגרים וקטורים פשוטה יותר מארכיטקטורות מקבילות ביותר המשמשות לעיבוד גרפי. ו-VPUs מספקים מודל תכנות הרבה פחות מורכב.

צוותי המחקר והפיתוח של האנדים הן בפעילות בצפון אמריקה והן בצוות המורחב של טייוואן התמקדו בפיתוח ארכיטקטורות מתקדמות עבור מעבדי RISC-V מתקדמים. יש לציין שהשניים השיגו אבן דרך משמעותית על ידי פיתוח מנוע RISC-V וקטור (RVV) הראשון, AndesCore™ NX27V, המבוסס על מפרט RISC-V International RVV. תוך הצגת הזריזות והחדשנות של צוות ההנדסה של האנדים, התכנון הושלם תוך שנה והתבסס על גרסה V0.8 של מפרט ההרחבה הווקטורית של RISC-V, ובהמשך שונה לגרסה V1.0 כאשר RVV אושרר. הישג זה הוביל לכמה ניצחונות גדולים בעיצוב OEM.

בשנה שעברה בכנס הבינלאומי לסימפוזיון על ארכיטקטורת מחשבים (ISCA) 2023 באורלנדו, פלורידה, META הציגה את המאמר שלה, "MTIA: First Generation Silicon Targeting Meta's Recommendation Systems", שהוא פרויקט מרכז הנתונים של החברה, שרתי AI. ישנם 64 רכיבי עיבוד (PE) בעיצוב השרת התומכים במאיץ הקנייני של MRETA שנבנה בהתאמה אישית. כל PE מכיל שני מעבדים: אחד סקלרי ואחד וקטור. שניהם הם IP של האנדים שמהנדסי META התאימו מאוד, תוך שימוש בהרחבות מותאמות אישית של Andes (ACE) כדי לייצר פתרון ייחודי לחלוטין המכוון לדרישות מחשוב ה-AI הספציפיות של META.

התכנון אימת את היעילות של RISC-V עם הרחבות וקטוריות כפתרון רב עוצמה לצרכי מחשוב מרכז נתונים בינה מלאכותית בזמן שהביקוש לחומרת עיבוד מרכזי נתונים מתפוצץ. לפי תובנות עתידיות בשוקדוח "תחזית שוק המעבד של מרכז הנתונים (2023 עד 2033)", שוק המעבדים של מרכזי הנתונים צפוי לגדול באופן משמעותי במהלך השנים הקרובות, מונע על ידי הביקוש הגובר למחשוב ענן, ניתוח נתונים גדולים ובינה מלאכותית (AI) . המניעים העיקריים של צמיחה זו כוללים את הצורך בעיבוד נתונים מהיר יותר, יעילות מוגברת והפחתת עלויות.

בשנת 2021, בנוסף להרחבות הווקטוריות RISC-V International אשרר 11 הרחבות נוספות. איור 1 ממחיש את מפת הדרכים של מוצר האנדים לתמיכה בהרחבות אלו. לאורך הדרך לסוף 2022 סדרות N25F-SE, 27 ו-45 נמסרו מאז, בשנת 2023, Andes סיפקה לשוק שש ליבות RISC-V חדשות, כגון D25F-SE, D23, N225, NX45V, AX45MPV כמו גם AX65. מפת הדרכים משתרעת ממעבד RISC-V בעל הספק נמוך ומאובטח מאוד AndesCore™ D23 ועד ל-AX65, הראשון בסדרת 60, ששוחרר ברבעון הרביעי של 2023 ונשלח כעת ללקוחות עיצובים.

ה-AX65 הוא מעבד 13 שלבים, 4 כיוונים 64 סיביות לא בסדר עם פרופיל RVA 22 (פרופיל RVA22U64 מציין את תכונות ה-ISA הזמינות לסביבות הפעלה במצב משתמש במעבדי יישומים של 64 סיביות). מצוידת בצנרת של 13 שלבים, פענוח רחב של 4, ביצוע מחוץ לסדר רחב של 8, הסדרה מכוונת לשקעי מעבד יישומי לינוקס של בקרי מחשוב, רשתות ובקרים מתקדמים.

ה-AX65 מאפשר אשכולות מרובי ליבות מאחת עד ארבע עד שמונה ליבות. הביצועים ברמה עולמית, פועלים בתדר שעון של 2.4 גיגה הרץ בתהליך TSMC של שבעה ננומטר. ביצועי המספרים השלמים (Specint 2006) הם 8.25 לג'יגה-הרץ, ו-SpecFp2006 הוא 10.2 לג'יגה-הרץ, שהם הביצועים הידועים ביותר של SPEC CPU® 2006 עם עיצוב מטמון בשתי רמות. ה-AX66, AX63 ו-AX67 יימסרו לאחר מכן.

תחום נוסף שאנדים השקיעו בו הוא ביצועים גבוהים של מעבד RISC-V CPU IP בדרגת רכב. החדירה של RISC-V SoCs בעיצובי רכב צפויה להגיע ל-21.4% עד 2030, על פי The SHD Group "דוח שוק RISC-V: תחזיות יישומים בעולם הטרוגני." Andes פיתחה מוצרים תואמי בטיחות פונקציונליים, כוללים את ה-N25F-SE שלה, ה-IP של מעבד RISC-V המעבד הראשון בעולם התואם לחלוטין ל-ISO 26262; D25F-SE, התומך בהוראות הרחבת DSP; והמעבדים מסדרת 45-SE העומדים ברמת ASIL הגבוהה ביותר, פונקציית ASIL D. ACE תשופר כדי להוסיף תמיכה במעבדים מסדרת 45.

על בסיס הביקוש למוצרי Andes RISC-V חוו, החברה ממשיכה להישאר רווחית וממשיכה ליהנות מצמיחה מהירה. מ-2021 עד 2023, הכנסות האנדים הראו צמיחה של כמעט 30%. זה ניזון על ידי למעלה מ-300 בעלי רישיונות מסחריים ויותר מ-600 הסכמי רישיון חתומים עם לקוחות מבוזרים גיאוגרפית בטייוואן, סין, קוריאה, יפן, אירופה וארה"ב. מספר העובדים העולמי של החברה צמח בכמעט 70% באותה תקופה.

סיכום

בעידן המוגדר על ידי התפתחות טכנולוגית מהירה, Andes Technology Corp. עומדת בחזית החדשנות בשוק ה-IP RISC-V CPU. מההנפקה החלוצית של תעודות פיקדון בחו"ל (GDR) ועד להתקדמות פורצת הדרך בארכיטקטורת RISC-V, טכנולוגיית האנדים ממשיכה להגדיר מחדש את הסטנדרטים בתעשייה ולעצב את עתיד המחשוב. ככל שהדרישה לפתרונות מחשוב יעילים ובעלי ביצועים גבוהים ממשיכה לעלות, טכנולוגיית Andes נותרה מחויבת לספק פתרונות RISC-V שאין שני להם כדי להניע שינוי טרנספורמטיבי בנוף הטכנולוגי הגלובלי.

גם לקרוא:

WEBINAR חי: RISC-V ארכיטקטורת ערכת הוראות: שיפור כוח המחשוב

רשת אינטרנט: נצל RISC-V IP מוסמך ליצירת שבבי רכב בדרגת ASIL ISO 26262

שתף את הפוסט הזה באמצעות:

- הפצת תוכן ויחסי ציבור מופעל על ידי SEO. קבל הגברה היום.

- PlatoData.Network Vertical Generative Ai. העצים את עצמך. גישה כאן.

- PlatoAiStream. Web3 Intelligence. הידע מוגבר. גישה כאן.

- PlatoESG. פחמן, קלינטק, אנרגיה, סביבה, שמש, ניהול פסולת. גישה כאן.

- PlatoHealth. מודיעין ביוטכנולוגיה וניסויים קליניים. גישה כאן.

- מקור: https://semiwiki.com/ip/343097-andes-technology-pioneering-the-future-of-risc-v-cpu-ip/