Durante l' GOMACTech conferenza tenutasi nella Carolina del Sud la scorsa settimana ho avuto una chiamata Zoom con Deepak Shankar, fondatore e VP Technology di Mirabilis Design Inc. per porre domande e visualizzare una demo dal vivo di VisualSim – una piattaforma di modellazione, simulazione, esplorazione e collaborazione per sviluppare elettronica e SoC. Ciò che rende VisualSim così distintivo è che viene fornito in bundle con circa 500 blocchi IP di alto livello pronti per l'uso, inclusi 35 processori ARM, circa 100 processori e oltre 30 diverse interconnessioni. Gli utenti di VisualSim collegano rapidamente questi blocchi IP insieme visivamente per creare i loro sistemi, completi di reti. Un progettista automobilistico può modellare l'intera rete, comprese le comunicazioni 5G, gli aggiornamenti Ethernet, SDA e OTA con VisualSim.

Un modello di alto livello consente l'esplorazione più rapida dell'architettura e la realizzazione di compromessi architettonici, molto prima ancora che l'implementazione inizi con il codice RTL. Puoi modellare attività complesse come un bus, memorie e persino cache, misurando cose come ritardi e latenza end-to-end. Gli ingegneri possono misurare il rapporto successi/mancati della cache e cosa succede con le richieste alle cache L2. Sono modellati tutti i protocolli di rete più diffusi: AXI, CHI, CMN600, Arteris NOC, UCIe, ecc.

Con questo approccio di modellazione un architetto può modellare un SoC, un aereo completo o un sistema automobilistico e quindi iniziare a misurarne le prestazioni per vedere se soddisfa i requisiti. VisualSim è un simulatore multidominio in grado di integrare analogico, software, sistemi di alimentazione, digitale e networking in un unico modello.

Per la demo dal vivo Deepak mi ha mostrato un design basato su chiplet che aveva chiplet separati per DSP, GPU, processore AI e CPU tutti collegati insieme utilizzando UCIe e ciascun blocco IP era parametrizzato per consentire la personalizzazione e l'esplorazione.

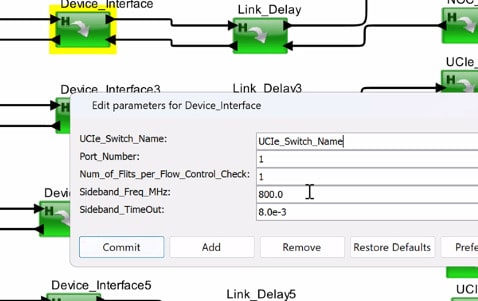

Inserendo il blocco UCIe c'era un IP chiamato switch UCIe e un utente può personalizzare questo blocco con cinque parametri, tutti ad alto livello.

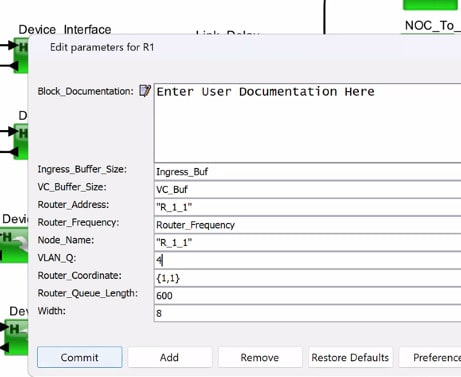

Un blocco IP del router aveva 10 parametri per la personalizzazione.

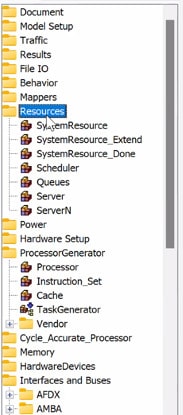

Per trovare ciascun blocco IP era presente un elenco scorrevole sul lato sinistro della GUI, con ciascuna famiglia di IP nella libreria. In pochi secondi puoi sfogliare, selezionare e iniziare a personalizzare un IP.

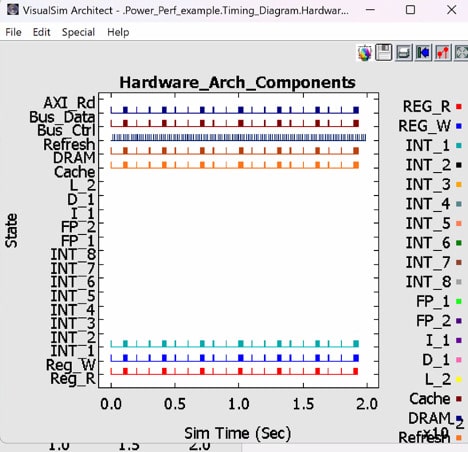

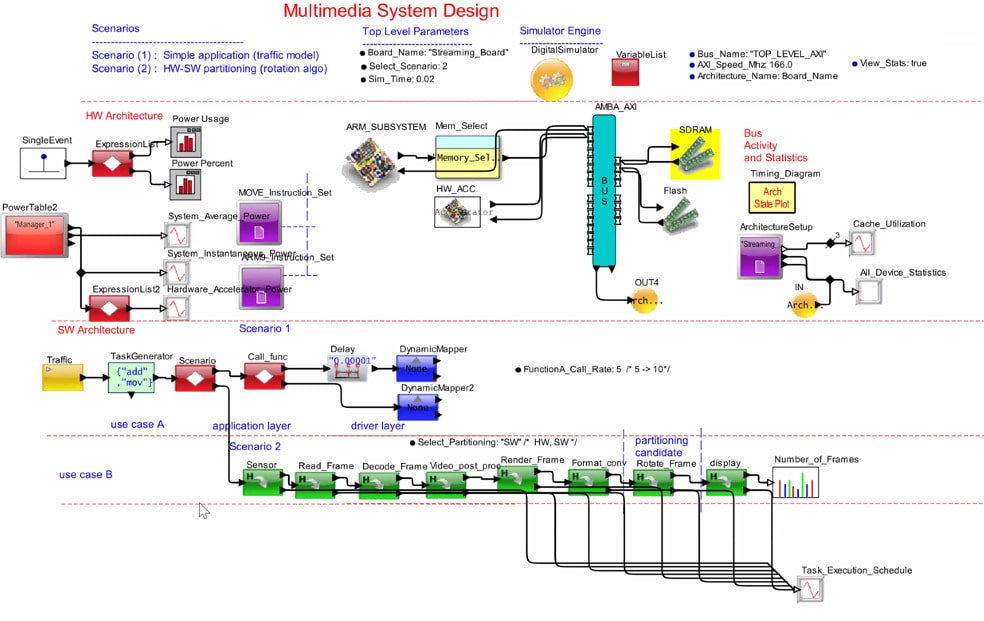

In VisualSim colleghi ciascun IP nel flusso di dati, rimanendo ad un livello elevato. La successiva demo dal vivo riguardava la progettazione di un sistema multimediale e per simulare 20 ms sono stati necessari circa 15 secondi di tempo, eseguito su un laptop. Mentre la simulazione è in esecuzione è possibile visualizzare le prestazioni del sistema come potenza istantanea, misurare l'utilizzo della pipeline, l'utilizzo della cache, l'utilizzo della memoria e persino visualizzare un diagramma temporale. Questa simulazione in tempo reale ha attivato 7.5 milioni di eventi e il cliente ha realizzato questo modello, che includeva l'intero SoC, in meno di 2 settimane.

Un altro esempio di cliente menzionato da Deepak include 45 master ed è stato completato in circa 4 settimane, completamente testato.

Puoi guardare all'interno di qualsiasi blocco IP e analizzare parametri come superato/fallito, quindi capire perché non è riuscito. C'è anche un motore AI per aiutare ad analizzare i dati in modo più efficiente, come trovare un overflow del buffer che ha causato un errore. Mentre il tuo modello è in esecuzione, vengono acquisite analisi per aiutare a misurare le prestazioni del sistema e identificare i colli di bottiglia dell'architettura.

VisualSim viene aggiornato due volte all'anno e poi ci sono aggiornamenti patch per quando vengono aggiunti nuovi blocchi IP. Un architetto definisce i requisiti in un file Excel, con parametri come limiti di latenza e occupazione del buffer.

Gli utenti di VisualSim possono definire l'intervallo di dimensioni del carico utile in termini di byte, intervalli di velocità e valori preferiti. Il modello del tuo sistema può essere analizzato tra le combinazioni per trovare il miglior set di parametri. Il simulatore capisce anche come esplorare i valori minimo, massimo e preferito. Puoi definire quali parametri di sistema verranno esplorati. Successivamente è stata mostrata una demo del sistema multimediale e poi simulata dal vivo.

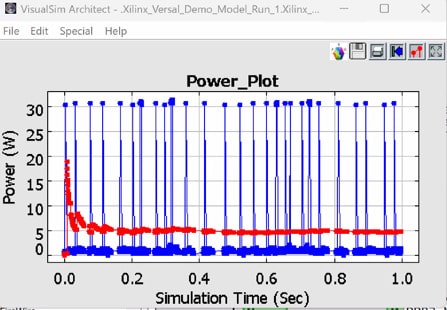

Per un blocco FPGA scegli il fornitore e il numero di parte, quindi puoi vedere la latenza per ciascuna attività e le statistiche del canale del NOC dopo l'esecuzione di una simulazione. È stato mostrato un diagramma di potenza per 1 secondo di funzionamento quando si utilizzavano parti Xilinx Versal.

Tutte le demo live sono state eseguite su un laptop Windows. Altri sistemi operativi supportati sono: Unix, Mac. L'esecuzione di VisualSim richiede un'infrastruttura HW minima, poiché i modelli sono di alto livello.

Gli utenti VisualSim ricevono oltre 500 esempi precostruiti per aiutarti a iniziare rapidamente, come un sistema di comunicazione completo con antenna, ricetrasmettitore, FPGA con banda base e interfaccia Ethernet. Gli architetti di sistema che utilizzano VisualSim possono collaborare con tutti gli specialisti di basso livello, come i progettisti RTL.

I compromessi a livello di sistema possono essere modellati e valutati, come:

- Passaggio dalla modulazione 64-QAM alla modulazione QPSK

- Processore da più veloce a più lento

- Modifica delle specifiche Ethernet

Se inizi con VisualSim per modellare, implementare e quindi misurare, aspettati di vedere una precisione del 95% rispetto ai risultati dell'implementazione RTL. La promessa dell'utilizzo di modelli di alto livello è quella di eliminare i problemi di prestazioni prima dell'implementazione o dell'integrazione. In realtà non è necessaria alcuna codifica per un intero modello di sistema.

Mirabilis conta finora 65 clienti in tutto il mondo e circa 250 progetti completati. Alcuni dei clienti più noti includono: NASA, Samsung, Qualcomm, Broadcom, GM, Boeing, HP, Imagination, Raytheon, AMD, Northrup Grumman.

In breve

Ai vecchi tempi un progettista di sistemi poteva disegnare le proprie idee su un tovagliolo mentre mangiava in un ristorante, per poi tornare al lavoro e mettere insieme alcuni fogli di calcolo Excel con equazioni arcane per creare un modello. Oggi c'è una nuova scelta, ed è dare VisualSim da Mirabilis una prova. Ora puoi modellare un intero sistema in poche settimane, oltre a fare compromessi architetturali durante l'esecuzione di simulazioni effettive, il tutto prima di entrare nei dettagli dettagliati dell'implementazione.

Blog correlati

Condividi questo post tramite:

- Distribuzione di contenuti basati su SEO e PR. Ricevi amplificazione oggi.

- PlatoData.Network Generativo verticale Ai. Potenzia te stesso. Accedi qui.

- PlatoAiStream. Intelligenza Web3. Conoscenza amplificata. Accedi qui.

- PlatoneESG. Carbonio, Tecnologia pulita, Energia, Ambiente, Solare, Gestione dei rifiuti. Accedi qui.

- Platone Salute. Intelligence sulle biotecnologie e sulle sperimentazioni cliniche. Accedi qui.

- Fonte: https://semiwiki.com/ip/343387-a-modeling-simulation-exploration-and-collaborative-platform-to-develop-electronics-and-socs/